没有合适的资源?快使用搜索试试~ 我知道了~

开发利用ip核和三段式流水灯的开发。Xilinx有很多IP核可以直接使用,例如数学运算(乘法器、除法器、浮点运算器等)、信号处理(FFT、DFT、DDS等)。IP核类似编程中的函数库(例如C语言中的printf()函数),可以直接调用,非常方便,大大加快了开发速度。

资源推荐

资源详情

资源评论

1

IP 核的配置和三段式流水灯

目录

第一章 IP 核的配置 ................................................................................................................. 2

1.1 ip 核的概述 ..................................................................................................................... 2

1.2 ip 核分类 ......................................................................................................................... 2

1.3 ip 核的介绍 ..................................................................................................................... 3

1.4 创建一个 ip 核 ............................................................................................................... 4

1.5 一个简单的 ip 核测试文件 ........................................................................................... 7

第二章 三段式流水灯 ........................................................................................................... 16

2.1 三段式流水灯框图 ....................................................................................................... 16

2.2 LED0 模块 ...................................................................................................................... 17

2.3 LED1 模块 ...................................................................................................................... 23

2.4 led2 模块 ....................................................................................................................... 27

2.5 muk 模块 ....................................................................................................................... 32

2.6 时钟模块 ...................................................................................................................... 33

2.7 锁相环模块 .................................................................................................................. 35

2.8 system 模块 ................................................................................................................... 39

2

第一章 IP 核的配置

Xilinx 有很多 IP 核可以直接使用,例如数学运算(乘法器、除

法器、浮点运算器等)、信号处理(FFT、DFT、DDS 等)。IP 核类似

编程中的函数库(例如 C 语言中的 printf()函数),可以直接调用,

非常方便,大大加快了开发速度。

输入输出的缓冲 buf

目前,大型设计一般推荐使用同步时序电路。同步时序电路基于

时钟触发沿设计,对时钟的周期、占空比、延时和抖动提出了更高的

要求。为了满足同步时序设计的要求,一般在 FPGA 设计中采用全局

时钟资源驱动设计的主时钟,以达到最低的时钟抖动和延迟。 FPGA

全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱

动结构,从而使全局时钟到达芯片内部的所有可配置单元(CLB)、I/O

单元(IOB)和选择性块 RAM(Block Select RAM)的时延和抖动都为最

小。为了适应复杂设计的需要,Xilinx 的 FPGA 中集成的专用时钟资

源与数字延迟锁相环(DLL)的数目不断增加,最新的 Virtex II 器件

最多可以提供 16 个全局时钟输入端口和 8 个数字时钟管理模块

(DCM)。

1.1 ip 核的概述

利用 IP 核设计电子系统,引用方便,修改基本元件的功能容易。

具有复杂功能和商业价值的 IP 核一般具有知识产权,尽管 IP 核的市

场活动还不规范,但是仍有许多集成电路设计公司从事 IP 核的设计、

开发和营销工作。IP 核有两种,与工艺无关的 VHDL 程序称为软核;

具有特定电路功能的集成电路版图称为硬核。硬核一般不允许更改,

利用硬核进行集成电路设计难度大,但是容易成功流片。

1.2 ip 核分类

IP 内核的三种类型

IP 内核可以在不同的硬件描述级实现,由此产生了三类 IP 内核:

软核、固核和硬核。这种分类主要依据产品交付的方式,而这三种

IP 内核实现方法也各具特色。

3

软核是用 VHDL 等硬件描述语言描述的功能块,但是并不涉及用

什么具体电路元件实现这些功能。软 IP 通常是以硬件描述语言 HDL

源文件的形势出现,应用开发过程与普通的 HDL 设计也十分相似,只

是所需的开发硬 软件环境 比较昂贵。软 IP 的设计周期短,设计投

入少。由于不涉及物理实现,为后续设计留有很大的发挥空间,增大

了 IP 的灵活性和适应性。其主要缺点是在一定程度上使后续工序无

法适应整体设计,从而需要一定程度的软 IP 修正,在性能上也不可

能获得全面的优化。由于软核是以 源代码 的形式提供,尽管源代码

可以采用加密方法,但其知识产权保护问题不容忽视。

硬核提供设计阶段最终阶段产品:掩模。以经过完全的布局布线

的网表形式提供,这种硬核既具有可预见性,同时还可以针对特定工

艺或购买商进行功耗和尺寸上的优化。尽管硬核由于缺乏灵活性而可

移植性差,但由于无须提供寄存器转移级(RTL)文件,因而更易于实

现 IP 保护。

固核则是软核和硬核的折衷。大多数应用于 FPGA 的 IP 内核均为

软核,软核有助于用户调节参数并增强可复用性。软核通常以加密形

式提供,这样实际的 RTL 对用户是不可见的,但布局和布线灵活。

在这些加密的软核中,如果对内核进行了参数化,那么用户就可通过

头文件或图形用户接口(GUI)方便地对参数进行操作。对于那些对时

序要求严格的内核(如 PCI 接口内核),可预布线特定信号或分配特定

的布线资源,以满足时序要求。这些内核可归类为固核,由于内核是

预先设计的代码模块,因此这有可能影响包含该内核的整体设计。由

于内核的建立(setup)、保持时间和握手信号都可能是固定的,因此

其它电路的设计时都必须考虑与该内核进行正确地接口。如果内核具

有固定布局或部分固定的布局,那么这还将影响其它电路的布局。

1.3 ip 核的介绍

IP(知识产权)核将一些在数字电路中常用,但比较复杂的功能

块,如 FIR 滤波器 、SDRAM 控制器、PCI 接口等设计成可修改参数

的模块。IP 核的重用是设计人员赢得迅速上市时间的主要策略。随

着 CPLD/FPGA 的规模越来越大,设计越来越复杂(IC 的复杂度以每

年 55%的速率递增,而设计能力每年仅提高 21%),设计者的主要任

务是在规定的时间周期内完成复杂的设计。调用 IP 核能避免重复劳

动,大大减轻工程师的负担,因此使用 IP 核是一个发展趋势。

4

IP 核包括硬 IP 与软 IP。可配置 IP 是参数化后的可重定目标 IP,

其优点是可以对功能加以裁剪,以符合特定的应用。这些参数包括总

线宽度、存储器容量、使能或禁止功能块。

硬 IP 最大的优点是确保性能,如速度、功耗等。然而,硬 IP 难

以转移到新工艺或集成到新结构中,是不可重配置的。

软 IP 是以综合形式交付的,因而必须在目标工艺中实现,并由

系统设计者验证。其优点是源代码灵活,可重定目标于多种制作工艺,

在新功能级中重新配置。

不过目前大多数库是收费的,但也可以从网上下载一些免费的

IP 核。

1.4 创建一个 ip 核

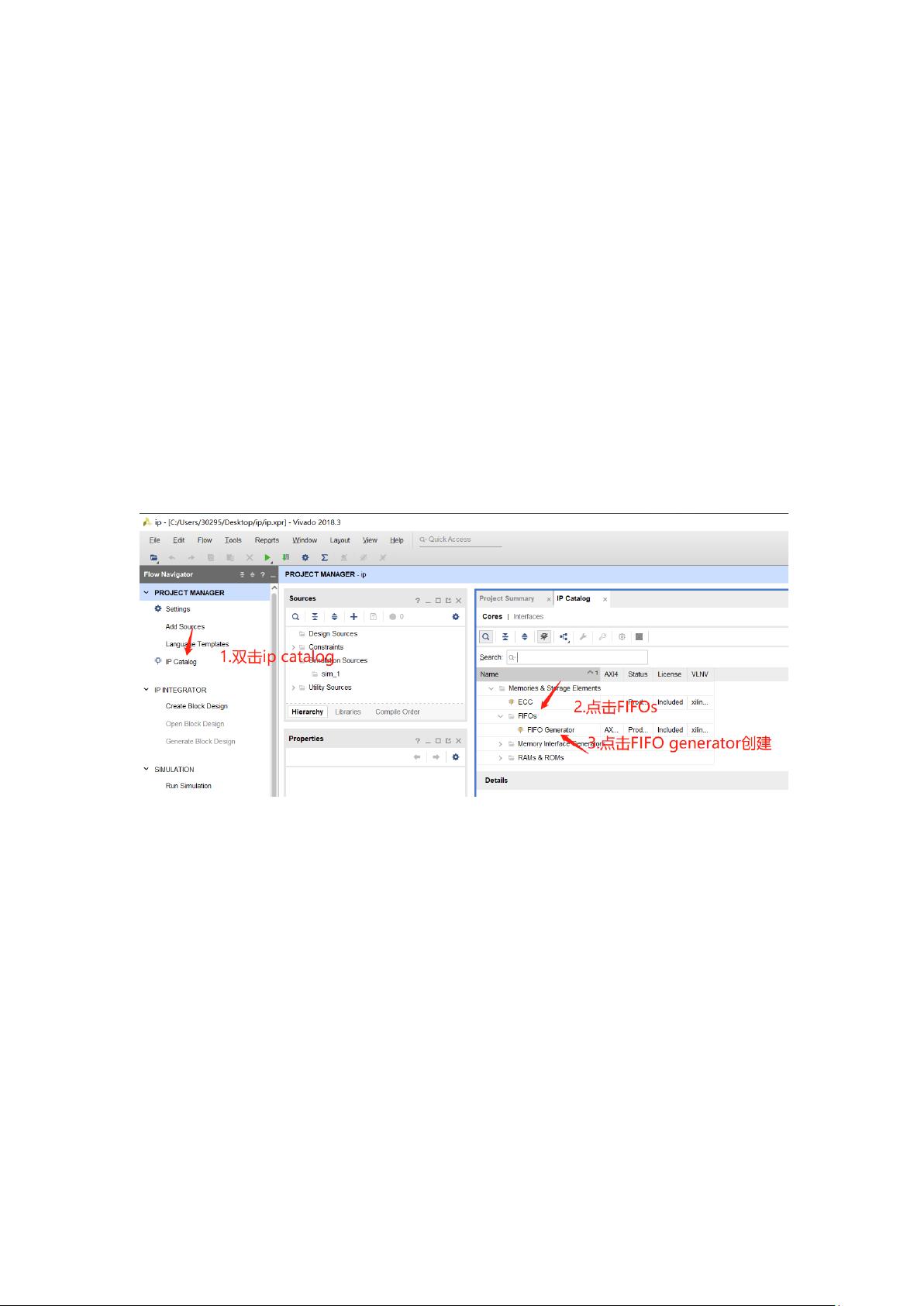

步骤一、创建 IP 核,点击 xilinx 中自带的 ip 核。从 1-2-3。

5

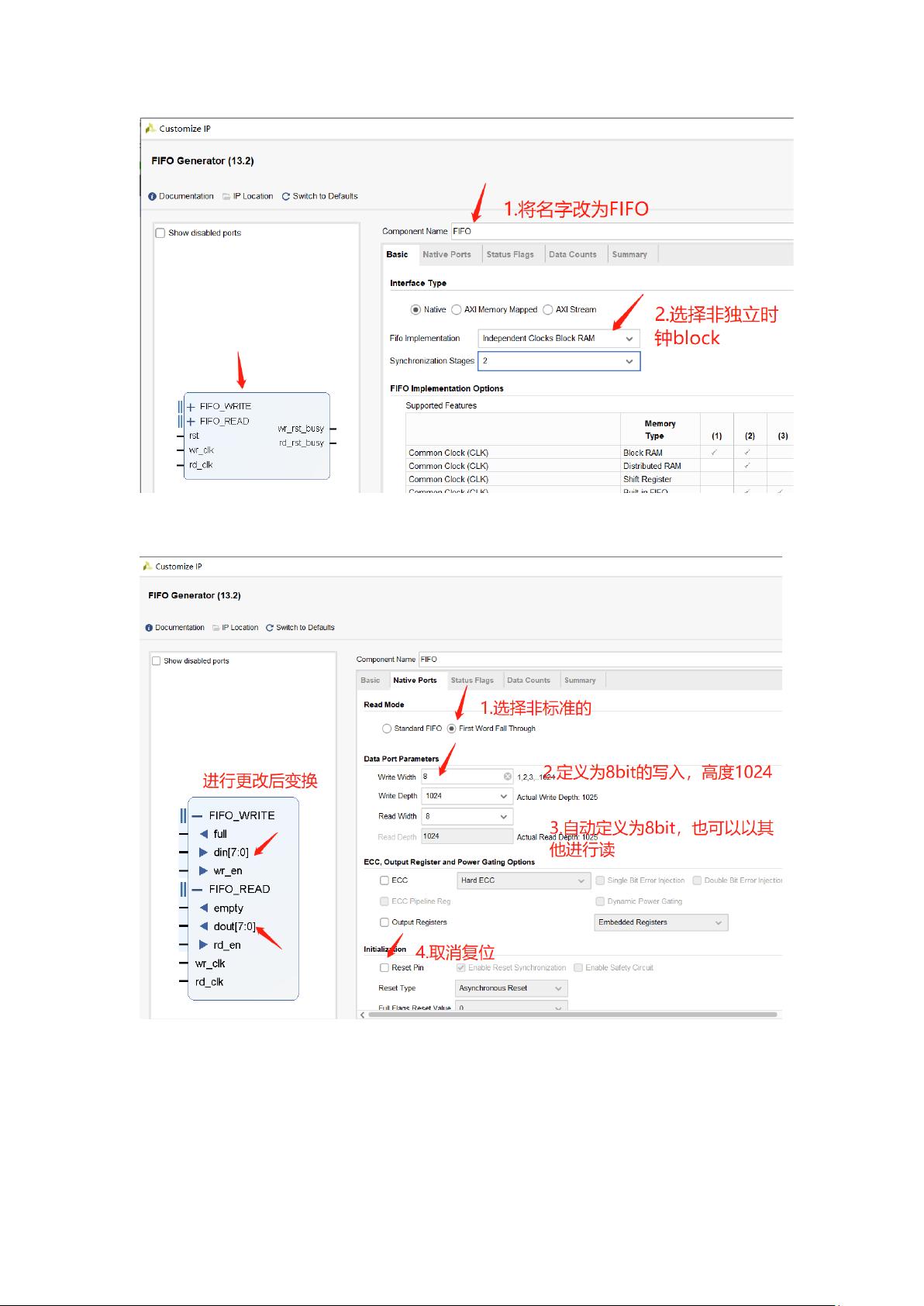

步骤二、更改名字 FIFO,选择非独立时钟。

步骤三、选择非标,8 字节,取消复位。

剩余40页未读,继续阅读

资源评论

韩叙白1997

- 粉丝: 0

- 资源: 5

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功