dc使用教程借鉴.pdf

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

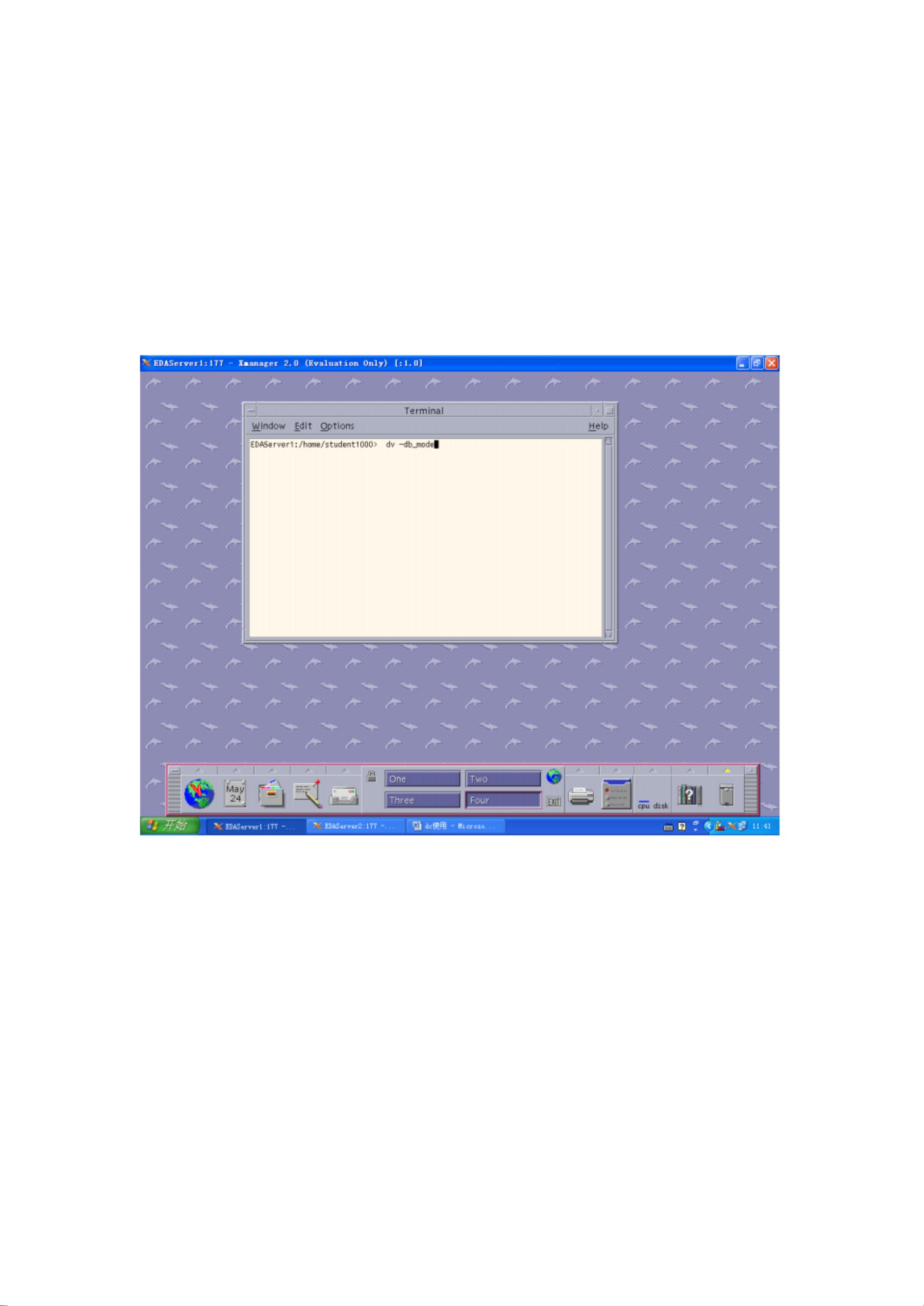

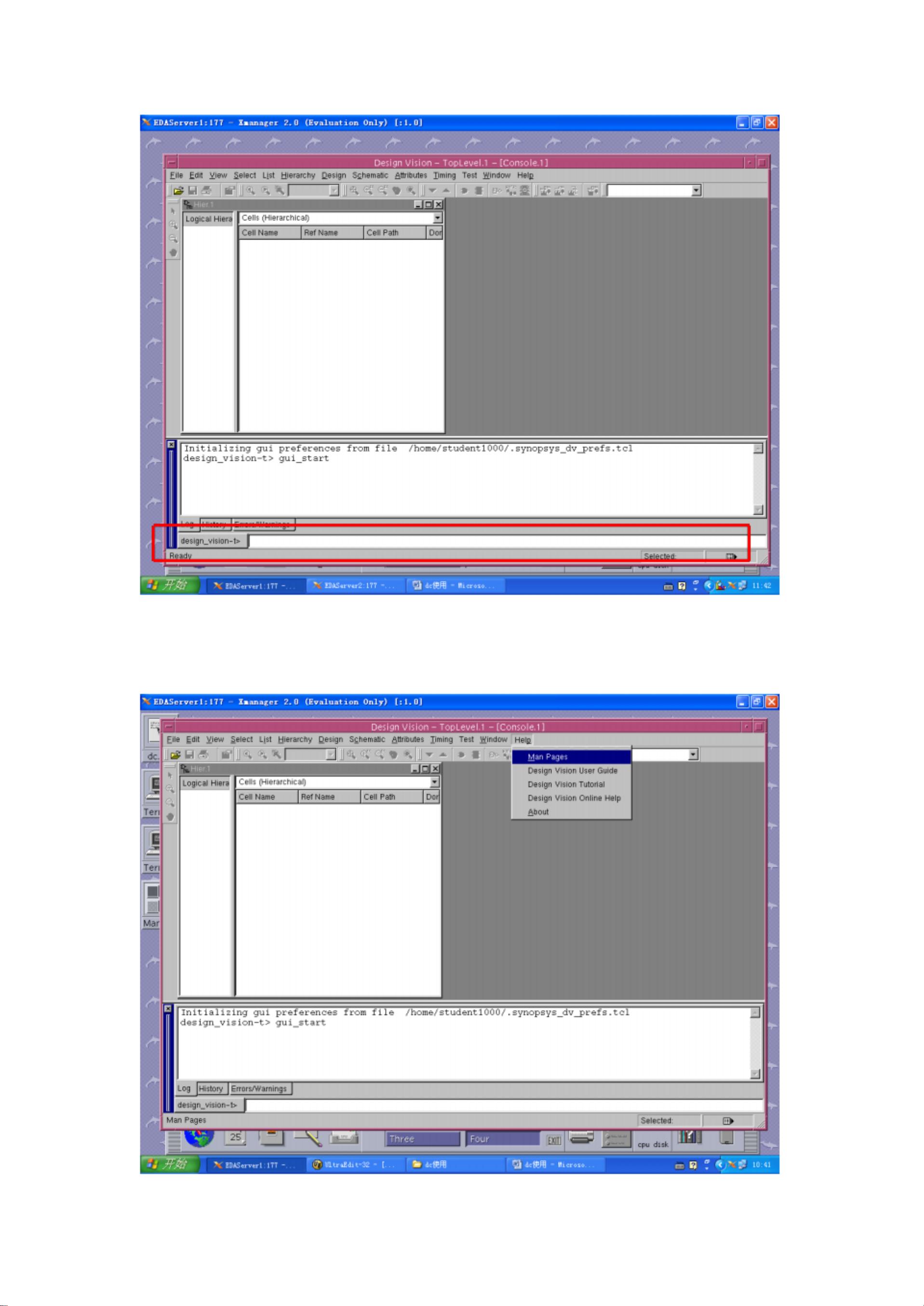

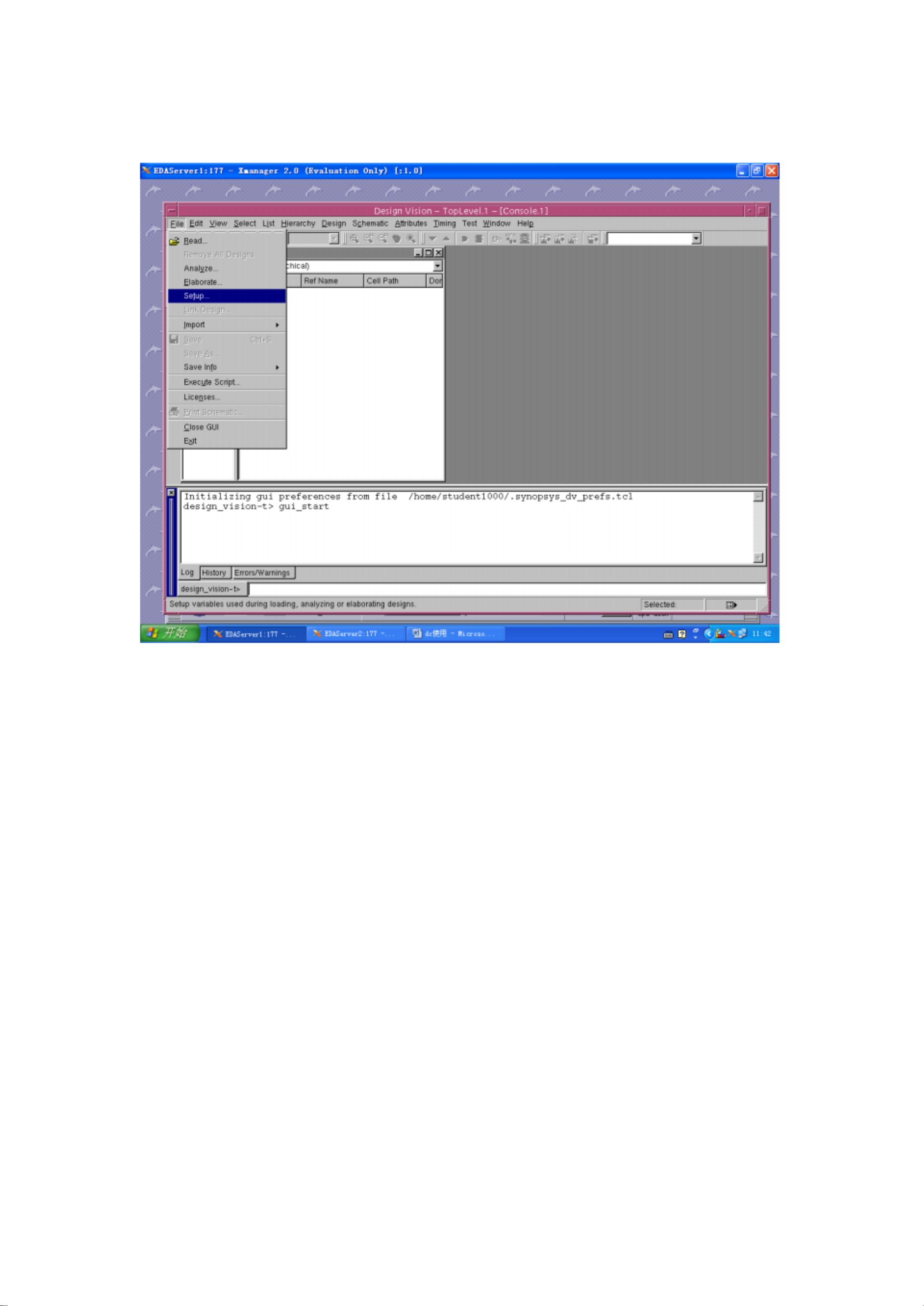

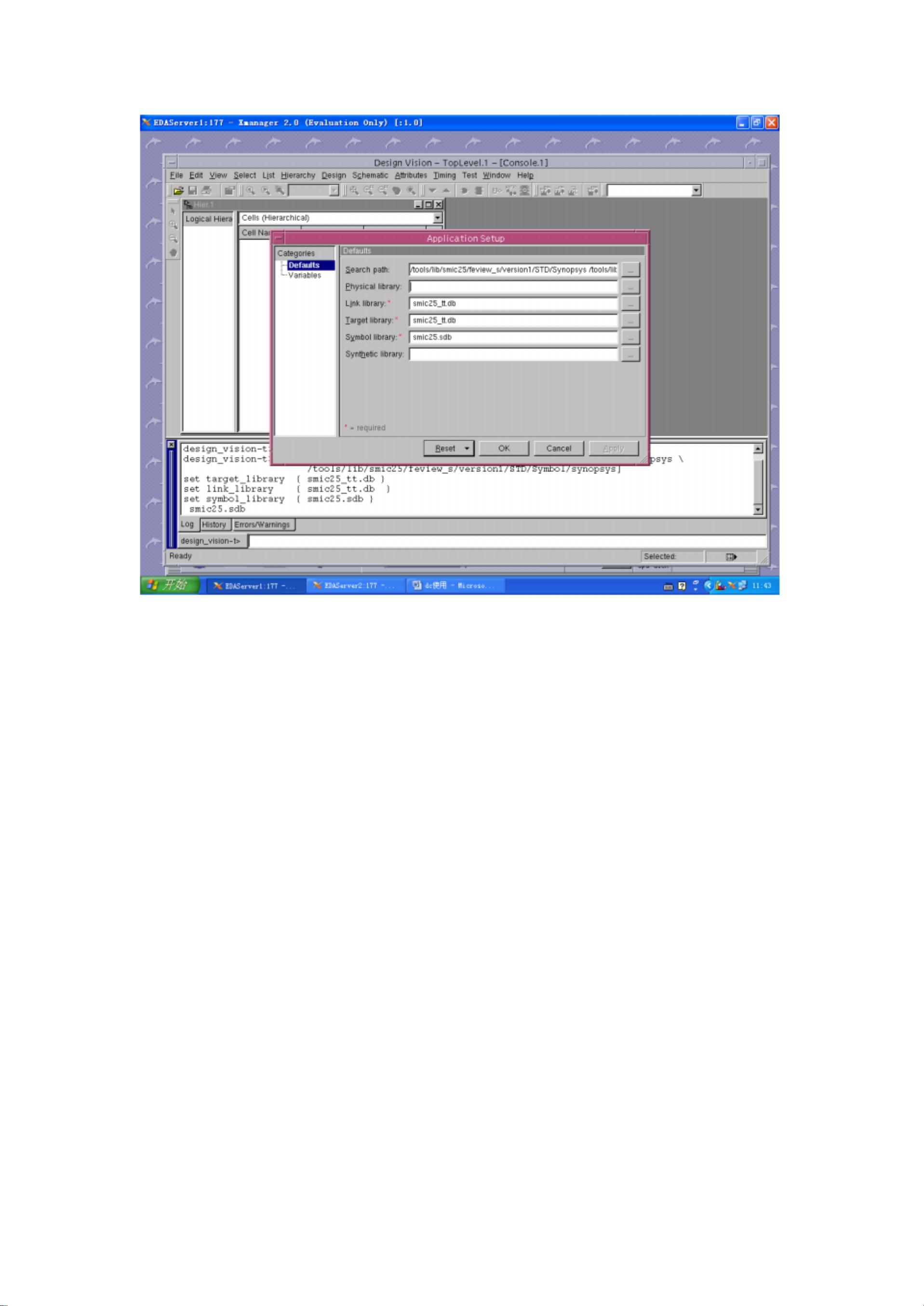

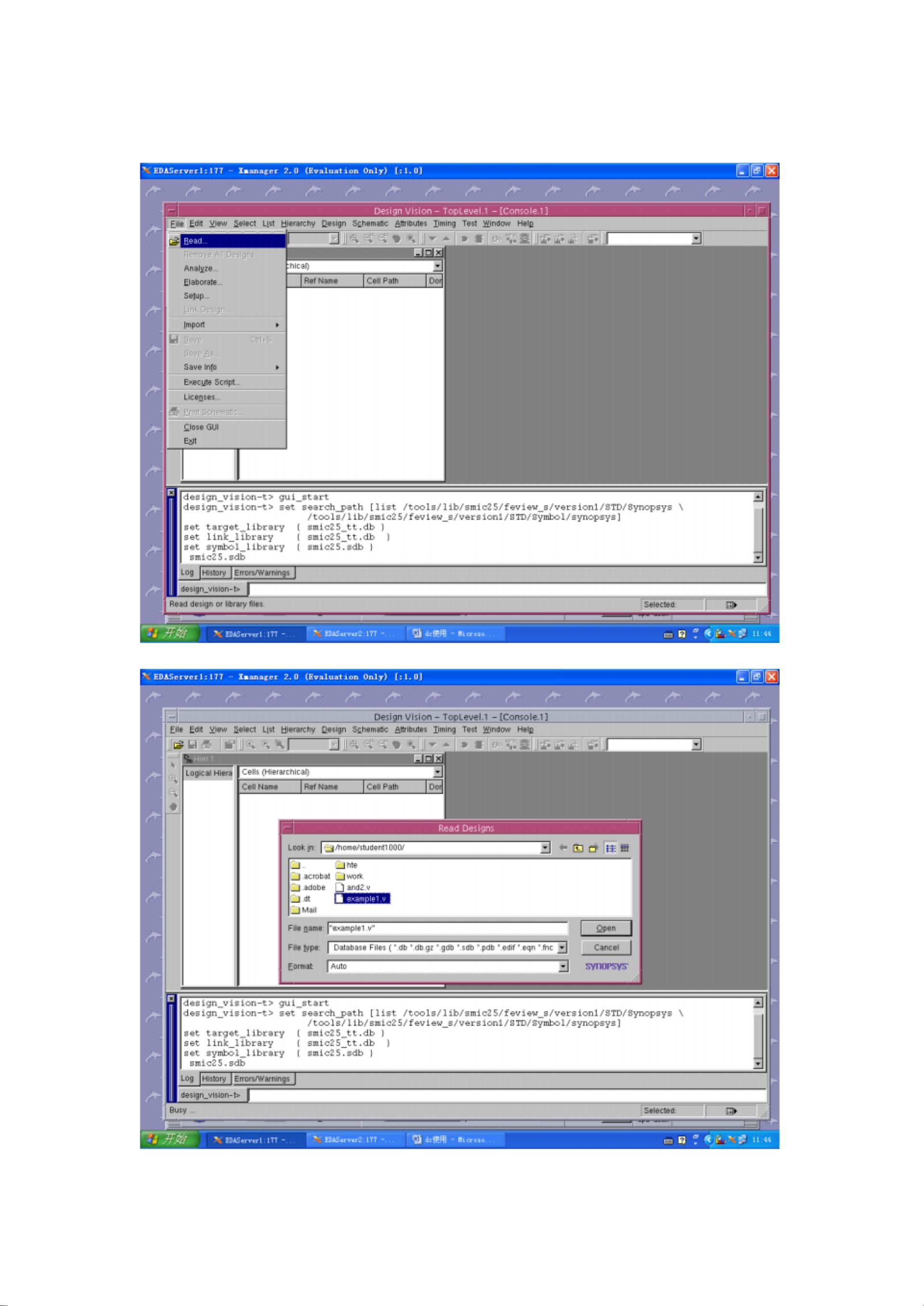

《DC使用教程详解》 DC(Design Compiler)是一款由Synopsys公司开发的高级综合工具,广泛应用于集成电路设计流程中的逻辑综合阶段。本教程将详细讲解如何使用DC的图形界面进行电路综合,包括启动DC、设置库文件、读入Verilog代码、设置约束条件以及进行综合优化和报告查看。 启动DC的图形界面。在终端窗口中输入命令`dv –db_mode`,然后按回车键。启动后,DC的命令输入框会显示在屏幕上方,你可以在这里输入各种操作命令。通过选择“Help”菜单下的“Man Pages”,可以查看DC的在线帮助文档,如需查询特定命令,例如`man create_clock`,即可获取相关命令的帮助信息。 接下来是设置库文件,这是DC综合的基础。在“File”菜单中选择“Setup”,在弹出的对话框中,需要设置搜索路径、目标库文件、链接库文件和符号库文件。示例中的设置如下: ```bash set search_path [list /tools/lib/smic25/feview_s/version1/STD/Synopsys \ /tools/lib/smic25/feview_s/version1/STD/Symbol/synopsys] set target_library {smic25_ff.db} set link_library {smic25_ff.db smic25_ss.db} set symbol_library {smic25.sdb} ``` 确认设置无误后,点击“OK”。 读入Verilog代码,通过“File”菜单的“Read”选项,选择你要综合的Verilog文件,如`example1.v`。成功读入后,日志框会显示“successfully”字样,表明操作成功。此外,可以通过查看按钮查看电路的符号图。 接着设置约束条件。时钟约束是必不可少的,选择时钟端口,如`clk`,然后在“Attributes”菜单中选择“Specify Clock”。设定时钟名称、周期、上升沿和下降沿。在本例中,时钟周期设为20ns。复位信号约束同样重要,选中`rst_n`端口,勾选“Don’t touch network”选项。 对于输入信号延迟,同时选择输入端口`a`、`b`、`c`,在“Attributes”菜单中选择“Operating Environment”下的“Input Delay”,设置相对于时钟的上升延迟。以20ns的时钟周期为例,设置为8ns(40%的时钟周期)。输出端口的约束类似,选择输出端口`o`,设置输出延迟也为8ns。 设置面积约束有助于优化电路面积。在“Attributes”菜单的“Optimization Constraints”中选择“Design Constraints”,设置`Max area`为0以最小化面积,`Max fanout`为4,`Max transition`为0.5,这些参数的具体含义可以参考SYNTHESIS.pdf文档。 完成以上步骤后,选择“Design”菜单的“Compile Design”,点击“OK”进行综合。当Log框显示“Optimization Complete”时,优化完成。 查看综合结果报告。可以使用“Design”菜单的“Report Area”查看面积报告,了解设计的总面积。同样,选择“Report Constraint Summary”查看约束满足情况。这些报告有助于评估综合结果是否符合设计要求。 DC的图形界面提供了直观且方便的使用方式,通过一系列的配置和操作,可以实现对Verilog代码的高效综合,满足设计中的各种约束,从而得到优化后的电路网表。熟悉并掌握这些步骤,将极大地提高你的设计效率。

剩余29页未读,继续阅读

m0_721688292024-09-26资源内容详细全面,与描述一致,对我很有用,有一定的使用价值。

m0_721688292024-09-26资源内容详细全面,与描述一致,对我很有用,有一定的使用价值。

- 粉丝: 2

- 资源: 7万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功