This quick reference guide presents the following step-by-step flows for

quickly closing timing, based on the recommendations in the UltraFast

Design Methodology Guide for Xilinx FPGAs and SoCs (UG949):

Initial Design Checks: Review utilization, logic levels, and timing

constraints before implementing the design.

Timing Baselining: Review and address timing violations after each

implementation step to help close timing after routing.

Timing Violation Resolution: Identify the root cause of setup or hold

violations, and resolve the timing violations.

Failfast and QoR Assessment Reports

You can use the failfast and quality of results (QoR) assessment reports

interchangeably to quickly review your design. Both reports compare

key design and constraints metrics against guideline limits. Metrics that

do not comply with guidelines are marked as REVIEW. The reports

include the following sections:

Design characteristics

Methodology checks

Conservative logic-level assessments based on a target Fmax

In the Vivado® tools, you can run these reports as follows:

xilinx::designutils::report_failfast

report_qor_assessment

See Failfast Report Overview (page 10) and the Vivado Design Suite

User Guide: Design Analysis and Closure Techniques (UG906).

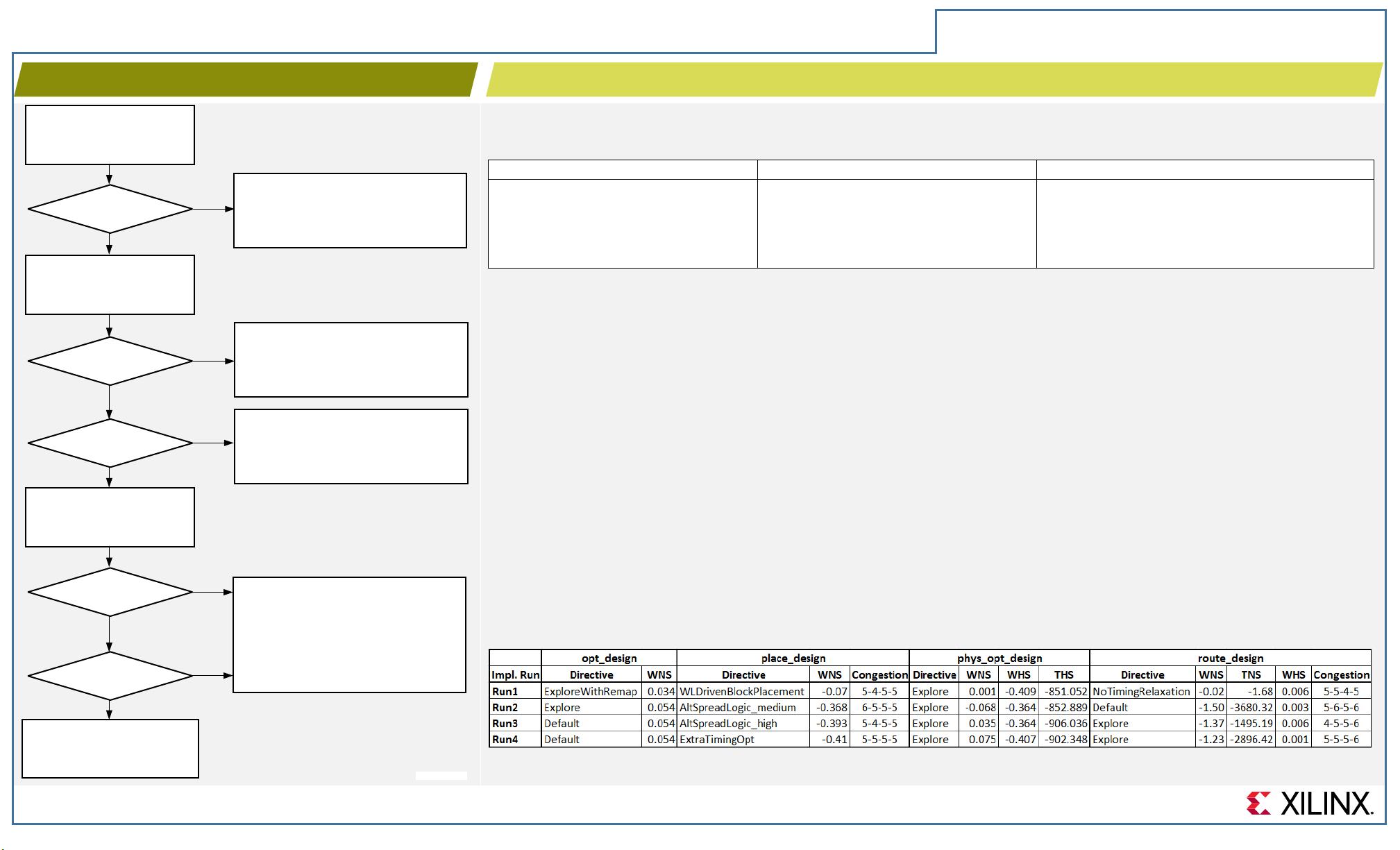

In the Vivado tools, report_qor_suggestions is called during the

implementation phase. This report analyzes the design, offers

suggestions, and automatically applies the suggestions in some cases.

Reports in the Vitis Environment

In the Vitis™ environment, report_failfast is called during the

compilation flow when using v++ –R 1 or v++ –R 2. To generate QoR

assessment and suggestions in the Vivado tools, use:

v++ --interactive

TIP: To automatically address most timing closure challenges during

implementation, you can use an Intelligent Design Run (IDR), which

is a special type of implementation run that leverages

report_qor_suggestions, ML-based strategy predictions, and

incremental compile. See UG949: Using Intelligent Design Runs.

Although implementing a design on a Xilinx® device is a fairly automated

task, achieving higher performance and resolving compilation issues due

to timing or routing violations can be a complex and time-consuming

activity. It can be difficult to identify the reason for a failure based on

simple log messages or post-implementation timing reports generated

by the tools. Therefore, it is essential to adopt a step-by-step design

development and compilation methodology, including the review of

intermediate results to ensure the design can proceed to the next

implementation step.

The first step is to make sure all initial design checks are addressed.

Review these checks at the following levels:

Each kernel made of custom RTL or generated by Vivado HLS

Note: Check that target clock frequency constraints are realistic.

Each major hierarchy corresponding to a subsystem, such as a

Vivado IP integrator block diagram with several kernels, IP blocks,

and connectivity logic

Complete design with all major functions and hierarchies, I/O

interfaces, complete clocking circuitry, and physical and timing

constraints

If the design uses floorplanning constraints, such as super logic region

(SLR) assignments or logic assigned to Pblocks, review the estimated

resource utilization for each physical constraint, and make sure that the

utilization guidelines are met. See the default guidelines in the failfast

report. To generate reports, use the following commands:

report_utilization –pblocks <pblockName>

report_failfast –pblock <pblockName>

report_failfast [–slr SLRn | -by_slr]

UG1292 (v2021.2) November 19, 2021

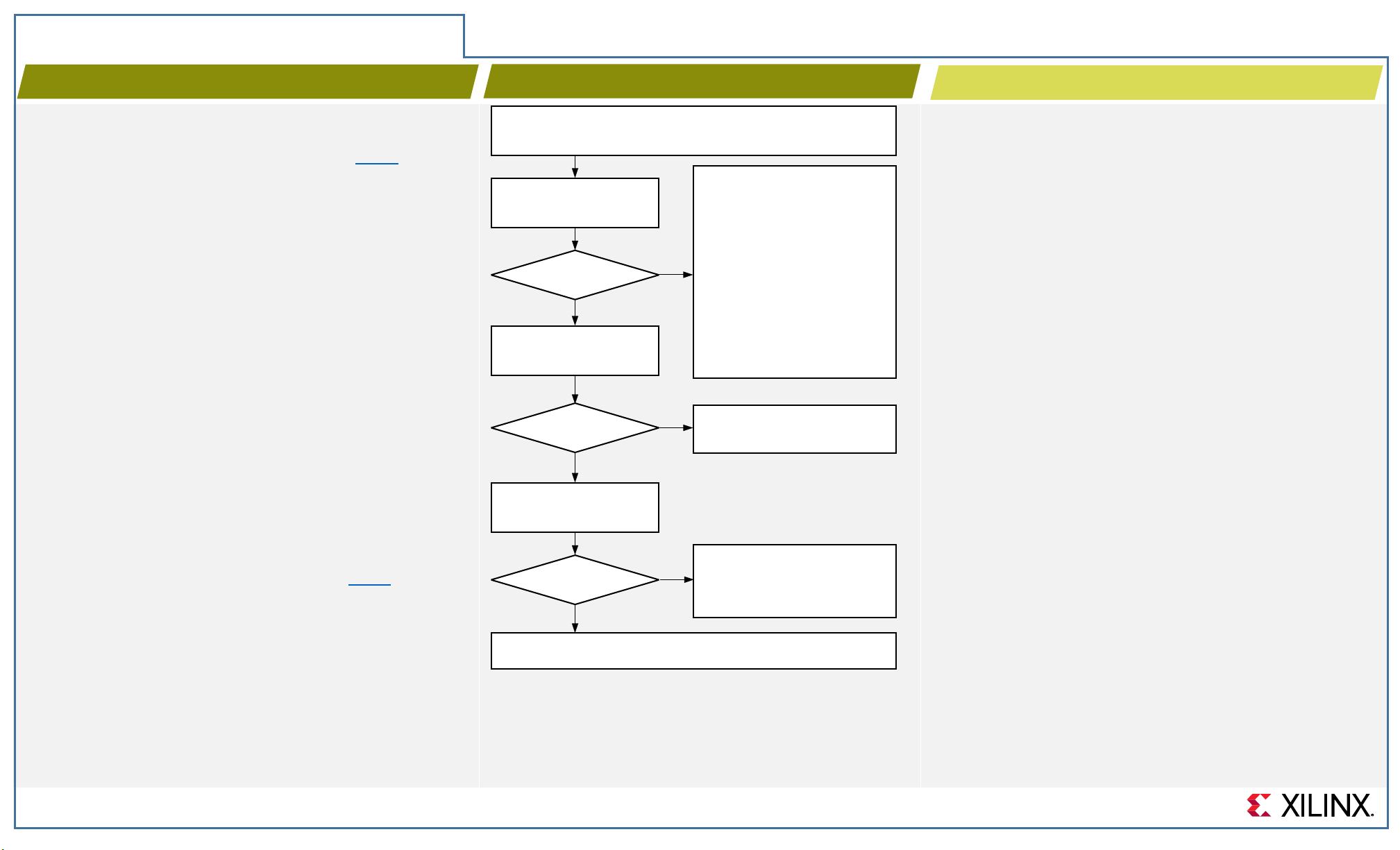

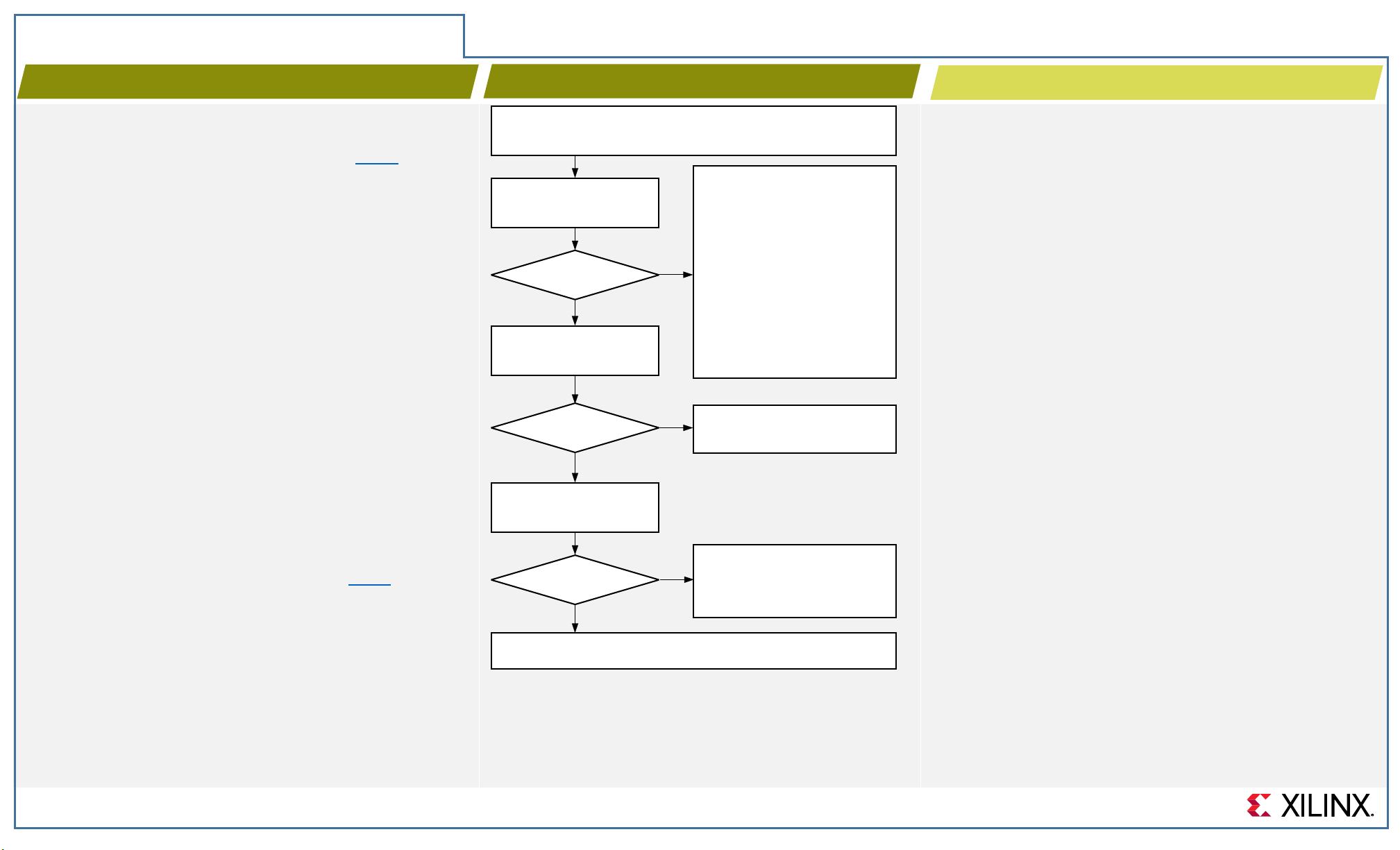

Open the synthesized design checkpoint (DCP) or the post-opt_design DCP

(if available)

Run report_failfast

Review Check Timing section in

report_timing_summary

Run report_methodology

Proceed to design implementation (logic optimization, placement, routing)

Fix methodology checks that impact

timing closure (Fmax)

Create missing clock constraints to

eliminate unconstrained internal

endpoints and avoid timing loops

Review the detailed reports to identify

the design characteristics or

constraints to improve:

● Estimated device and SLR Pblock

resource utilization

● Constraints preventing optimizations

● Control signals and average fanout

● Clock tree and clock domain

crossing constraints

● High logic levels given the target

frequency

Clean report?

Clean report?

Clean report?

Yes

Yes

Yes

No

No

No

X21574-091818

INITIAL DESIGN CHECKS - DETAILS

INITIAL DESIGN CHECKS FLOW

INITIAL DESIGN CHECKS DETAILS

UltraFast Design Methodology Timing Closure

Quick Reference Guide (UG1292)

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功