没有合适的资源?快使用搜索试试~ 我知道了~

HYNIX-HY64UD16162B-DF60I.pdf

需积分: 9 0 下载量 148 浏览量

2021-04-29

16:32:12

上传

评论

收藏 286KB PDF 举报

温馨提示

试读

11页

HYNIX-HY64UD16162B-DF60I.pdf

资源详情

资源评论

资源推荐

HY64UD16162B Series

1

Revision 1.0 / December. 2002

This document is a general product description and is subject to change without notice. Hynix Semiconductor Inc. does not

assume any responsibility for use of circuits described. No patent licenses are implied.

Document Title

Document Title

1

1

M x 16 bit Low Low Power 1T/1C

M x 16 bit Low Low Power 1T/1C

Pseudo SRAM

Pseudo SRAM

Revision history

Revision history

Revision No.

Revision No.

1.0

Draft Date

Draft Date

Dec. 3. ’02

Remark

Remark

Preliminary

History

History

Initial

HY64UD16162B Series

2

Revision 1.0 / December. 2002

This document is a general product description and is subject to change without notice. Hynix Semiconductor Inc. does not

assume any responsibility for use of circuits described. No patent licenses are implied.

1

1

M x 16 bit Low

M x 16 bit Low

Low Power 1T/1C

Low Power 1T/1C

SRAM

SRAM

DESCRIPTION

The HY64UD16162B is a 16Mbit 1T/1C SRAM

featured by high-speed operation and super low

power consumption. The HY64UD16162B adopts

one transistor memory cell and is organized as

1,048,576 words by 16bits. The HY64UD16162B

operates in the extended range of temperature and

supports a wide operating voltage range. The

HY64UD16162B also supports the deep power

down mode for a super low standby current. The

HY64UD16162B delivers the high-density low

power SRAM capability to the high-speed low power

system.

• CMOS Process Technology

• 1M x 16 bit Organization

• TTL compatible and Tri-state outputs

• Deep Power Down : Memory cell data hold invalid

• Standard pin configuration : 48-FBGA(6mmX8mm)

• Data mask function by /LB, /UB

• Separated I/O Power Supply : Vddq

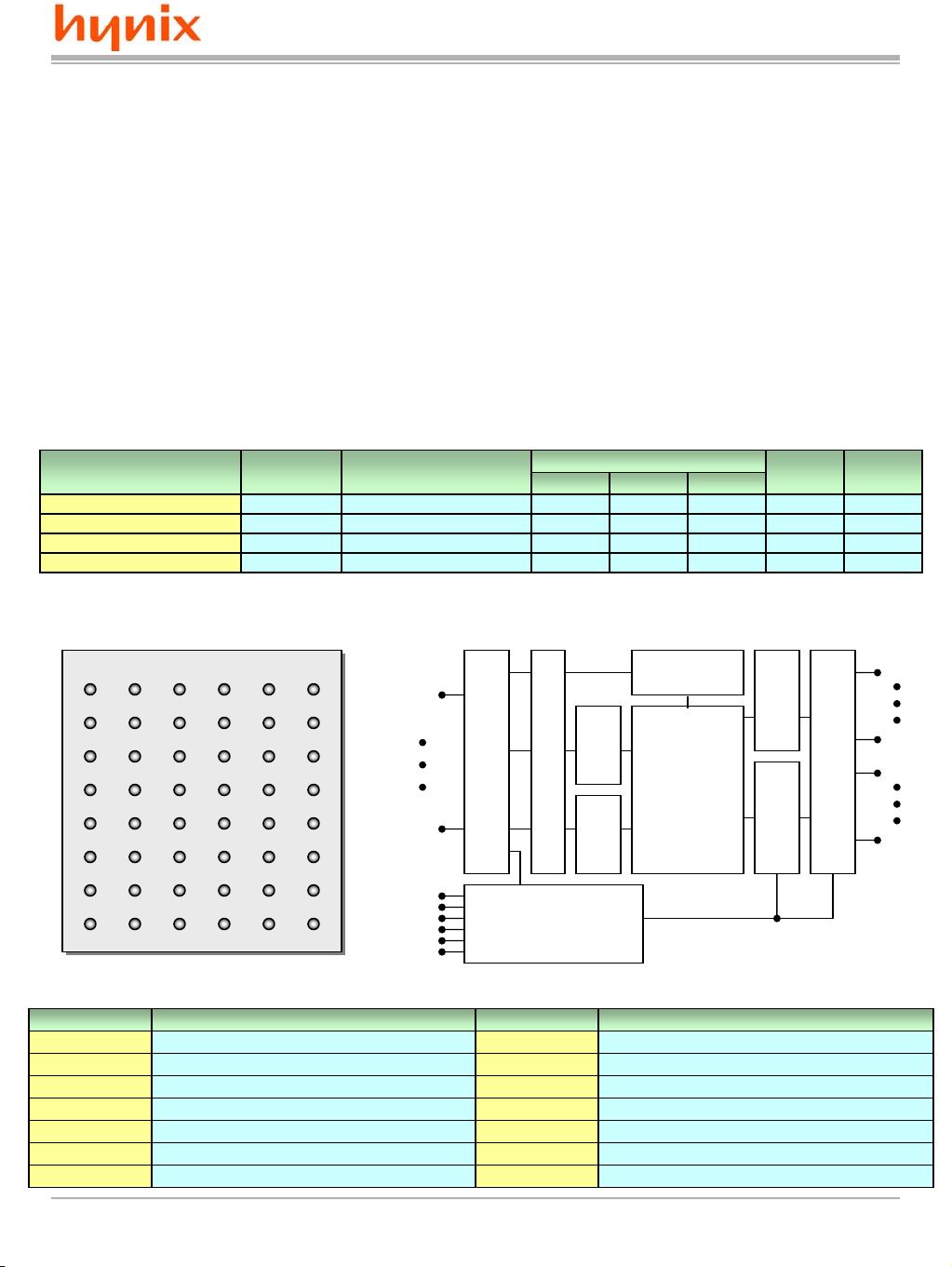

PRODUCT FAMILY

FEATURES

Note 1. tCS - /UB,/LB=High : Chip Deselect.

PIN DESCRIPTION

Pin Name Pin Function Pin Name Pin Function

/CS1 Chip Select

IO1~IO8 Lower Data Inputs/Outputs

/WE Write Enable

A0~A19 Address Inputs

/OE Output Enable

Vdd Power Supply for Internal Circuit

/LB Lower Byte(I/O1~I/O8)

Vss Ground

/UB Upper Byte(I/O9~I/O16)

CS2 Deep Power Down

DNU Do Not Use

IO9~IO16 Upper Data Inputs/Outputs

Vddq Power Supply for I/O

NC No Connection

PIN CONNECTION (Top View)

/LB /OE A0 A1 A2 CS2

IO9 /UB A3 A4 /CS1 IO1

IO10 IO11 A5 A6 IO2 IO3

Vss IO12 A17 A7 IO4 Vdd

Vddq IO13 DNU A16 IO5 Vss

IO15 IO14 A14 A15 IO6 IO7

IO16 A19 A12 A13 /WE IO8

A18 A8 A9 A10 A11 NC

BLOCK DIAGRAM

ADD INPUT

BUFFER

PRE DECODER

COLUMN

DECODER

BLOCK

DECODER

ROW

DECODER

SENSE AMP WRITE DRIVER

DATA I/O

BUFFER

MEMORY ARRAY

1,024K x 16

CONTROL

LOGIC

A0

A19

IO1

IO8

IO9

IO16

/CS1

CS2

/OE

/LB

/UB

/WE

Product No.

Voltage [V]

Vdd/Vddq

Speed

tRC[ns]

Temp.

[°C]

(ISB1,Max) (IDPD,Max) (ICC2,Max)

Power Dissipation

Mode

HY64UD16162B-DF70E 3.0/3.0 70 -25~8585µA 2µA 25mA1CS with /UB,/LB:tCS

1

HY64UD16162B-DF60E 3.0/3.0 TBD -25~85TBD 2µA 25mA1CS with /UB,/LB:tCS

1

HY64UD16162B-DF60I 3.0/3.0 TBD -40~85TBD 2µA 25mA1CS with /UB,/LB:tCS

1

HY64UD16162B-DF70I 3.0/3.0 70 -40~8585µA 2µA 25mA1CS with /UB,/LB:tCS

1

HY64UD16162B Series

3

Revision 1.0 / December. 2002

Note

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent

damage to the device. This is stress rating only and the functional operation of the device under these or

any other conditions above those indicated in the operation of this specification is not implied. Exposure

to the absolute maximum rating conditions for extended period may affect reliability.

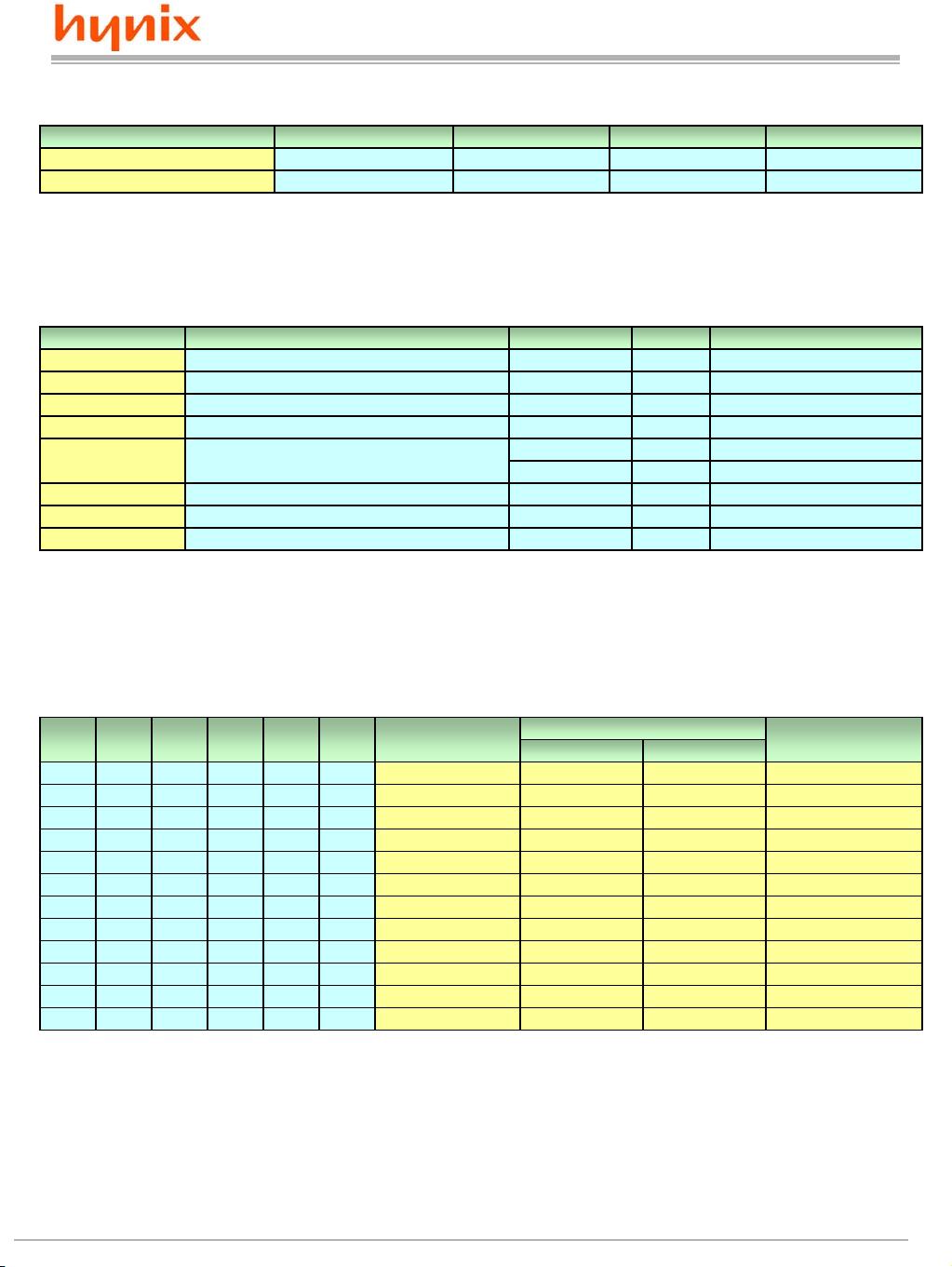

TRUTH TABLE

Power

Standby

/CS1

H

CS2

H

/WE

X

/OE

X

/LB

X

/UB

X

Mode

Deselected

I/O1~I/O8

High-Z

I/O9~I/O16

High-Z

I/O Pin

X

X

L

L

L

L

L

L

L

L

L

L

H

H

H

H

H

H

H

H

H

H

X

X

L

H

H

L

H

H

L

H

H

X

X

X

L

H

X

L

H

X

L

H

X

H

L

L

L

H

H

H

L

L

L

X

H

H

H

H

L

L

L

L

L

L

Deselected

Deselected

Write

Read

Output Disabled

Write

Read

Output Disabled

Write

Read

Output Disabled

High-Z High-Z

High-Z High-Z

DIN High-Z

DOUT High-Z

High-Z High-Z

DINHigh-Z

DOUT

High-Z

DIN

DOUT

High-Z

High-Z

High-Z

DIN

DOUT

High-Z

Deep Power Down

Standby

Active

Active

Active

Active

Active

Active

Active

Active

Active

Note

1. H=V

IH, L=VIL, X=don’t care(VIL or VIH)

2. /UB, /LB(Upper, Lower Byte enable)

These active LOW inputs allow individual bytes to be written or read.

When /LB is LOW, data is written or read to the lower byte, I/O1 - I/O8.

When /UB is LOW, data is written or read to the upper byte, I/O9 - I/O16.

ORDERING INFORMATION

Part Number Speed Package

HY64UD16162B-E 60 / 70 FBGA

HY64UD16162B-I 60 / 70 FBGA

Power

LL-Part

LL-Part

Temperature

E

1

I

2*

Note

1. E : Extended Temp. (-25°C~ 85°C)

2. I : Industrial Temp. (-40°C~ 85°C)

ABSOLUTE MAXIMUM RATINGS

1

Symbol Parameter Rating Remark

VIN Input Voltage

-0.3 to Vdd+0.3

Unit

V

Vdd Core Power Supply -0.3 to 3.6 V

TA Ambient Temperature

-25 to 85 HY64PD16162A-E°C

TSTG Storage Temperature -55 to 150 °C

PD Power Dissipation 1.0 W

TSOLDER Ball Soldering Temperature & Time 260•10 °C•sec

-40 to 85 HY64PD16162A-I°C

Vddq I/O Power Supply -0.3 to 3.6 V

VOUT Output Voltage

-0.3 to Vddq+0.3

V

剩余10页未读,继续阅读

LC灵灵

- 粉丝: 1

- 资源: 261

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0