5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Title

Size Document Number Rev

Date: Sheet

of

COVER PAGE 1.2

Altera Cyclone III Eval Board

B

117Tuesday, April 17, 2007

Title

Size Document Number Rev

Date: Sheet

of

COVER PAGE 1.2

Altera Cyclone III Eval Board

B

117Tuesday, April 17, 2007

Title

Size Document Number Rev

Date: Sheet

of

COVER PAGE 1.2

Altera Cyclone III Eval Board

B

117Tuesday, April 17, 2007

17 ~ 17

TOP 01 ~ 03

04 ~ 08

PAGE

09 ~ 11

15 ~ 16

SCHEMATIC

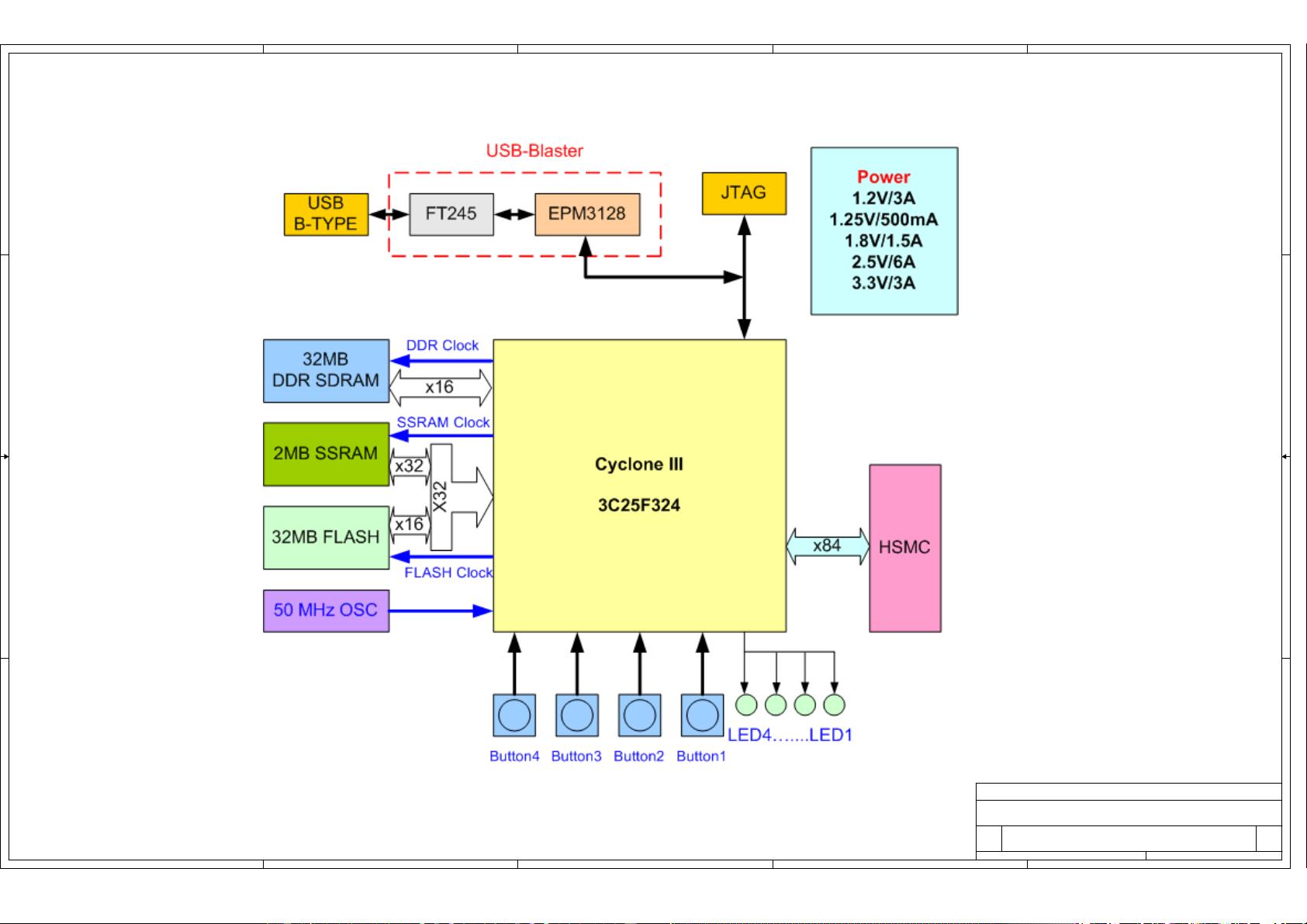

Cyclone III Starter Board

CONTENT

COVER PAGE, TOP

EP3C25 EP3C25 BANK1..BANK8, POWER, CONFIG

12 ~ 14

IN/OUT CLOCK, LEVEL SHIFT, KEY, CONNECT, HSMC

MEMORY DDR, SSRAM, FLASH

POWER POWER

USB BLASTER USB BLASTER

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Title

Size Document Number Rev

Date: Sheet

of

PLACEMENT 1.2

Altera Cyclone III Eval Board

B

217Tuesday, April 17, 2007

Title

Size Document Number Rev

Date: Sheet

of

PLACEMENT 1.2

Altera Cyclone III Eval Board

B

217Tuesday, April 17, 2007

Title

Size Document Number Rev

Date: Sheet

of

PLACEMENT 1.2

Altera Cyclone III Eval Board

B

217Tuesday, April 17, 2007

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

DDR_CLK_p

DDR_CKE

DDR_BA0

DDR_BA1

DDR_WE_n

DDR_CAS_n

DDR_RAS_n

DDR_CS_n

DDR_DQ[0..15]

DDR_DM0

DDR_DM1

JTAG_TDO

TMS

TCK

CONF

nCE

CONF_DONE

nSTATUS

DDR_A[0..12]

CIII_TDO

DDR_CLK_n

DDR_DQS0

DDR_DQS1

SRAM_WE_n

SRAM_CE1_n

SRAM_OE_n

SRAM_ADSC_n

SRAM_BE_n[0..3]

SRAM_CLK

FLASH_SRAM_DQ[0..31]

FLASH_SRAM_A[1..25]

FLASH_CLK

FLASH_ADV_n

FLASH_CE_n

FLASH_OE_n

FLASH_RESET_n

FLASH_WE_n

FLASH_CE_n

HSMC_CLKIN_p[1..2]

HSMC_CLKIN_n[1..2]

HSMC_TX_p[4..16]

HSMC_TX_n[4..16]

HSMC_SDA

CIII_TDI

TMS

TCK

HSMC_CLKOUT_p[1..2]

HSMC_CLKOUT_n[1..2]

HSMC_CLKOUT0

LED[0..3]

JTAG_TDO

HSMC_CLKIN0

HSMC_RX_p[4..16]

HSMC_RX_n[4..16]

HSMC_SCL

HSMC_D[0..19]

KEY[0..3]

50MHZ

SRAM_WE_n

SRAM_CE1_n

SRAM_CLK

HSMC_SCL

KEY[0..3]

DDR_DQ[0..15]

DDR_DQS1

DDR_CLK_p

DDR_CKE

DDR_BA0

DDR_BA1

DDR_WE_n

DDR_CAS_n

DDR_RAS_n

DDR_CS_n

DDR_DM0

DDR_DM1

DDR_A[0..12]

DDR_CLK_n

DDR_DQS0

HSMC_RX_n[4..16]

HSMC_RX_p[4..16]

HSMC_D[0..19]

HSMC_CLKOUT_p[1..2]

HSMC_CLKOUT_n[1..2]

FLASH_CLK

FLASH_ADV_n

FLASH_CE_n

FLASH_OE_n

FLASH_RESET_n

FLASH_WE_n

HSMC_TX_p[4..16]

HSMC_TX_n[4..16]

50MHZ

TMS

TCK

nCONFIG

CIII_TDI

CONF_DONE

nSTATUS

nCE

CIII_TDO

SRAM_BE_n[0..3]

SRAM_ADSC_n

SRAM_OE_n

FLASH_SRAM_A[1..25]

FLASH_SRAM_DQ[0..31]

HSMC_CLKIN0

HSMC_CLKIN_p[1..2]

HSMC_CLKIN_n[1..2]

HSMC_CLKOUT0

HSMC_SDA

FLASH_WAIT

FLASH_WAIT

LINK_D3 LINK_D0

LINK_D1

LINK_D2

LINK_D0

LINK_D1

LINK_D2

LINK_D3

LED[0..3]

CONF

nCONFIG

CPU_RST_n

CPU_RST_n

Title

Size Document Number Rev

Date: Sheet

of

TOP LEVEL 1.2

Altera Cyclone III Eval Board

B

317Tuesday, April 17, 2007

Title

Size Document Number Rev

Date: Sheet

of

TOP LEVEL 1.2

Altera Cyclone III Eval Board

B

317Tuesday, April 17, 2007

Title

Size Document Number Rev

Date: Sheet

of

TOP LEVEL 1.2

Altera Cyclone III Eval Board

B

317Tuesday, April 17, 2007

Memory PAGE 12-14

SRAM_WE_n

DDR_CLK_n

DDR_RAS_n

SRAM_CLK

FLASH_CE_n

SRAM_CE1_n

DDR_CAS_n

DDR_CLK_p

FLASH_ADV_n

FLASH_CLK

DDR_DM0

DDR_DM1

FLASH_OE_n

SRAM_ADSC_n

FLASH_RESET_n

SRAM_OE_n

DDR_A[0..12]

DDR_DQ[0..15]

DDR_DQS0

DDR_CKE

DDR_DQS1

DDR_CS_n

DDR_WE_n

DDR_BA0

FLASH_WE_n

SRAM_BE_n[0..3]

DDR_BA1

FLASH_SRAM_A[1..25]

FLASH_SRAM_DQ[0..31]

FLASH_WAIT

Power PAGE 15-16

Clock, LED, Tact SW, HSMC PAGE 9-11

KEY[0..3]

50MHZ

HSMC_TX_n[4..16]

HSMC_D[0..19]

LF_TMS

HSMC_SCL

LF_TCK

HSMC_RX_p[4..16]

HSMC_CLKIN_n[1..2]

HSMC_CLKIN_p[1..2]

HSMC_CLKOUT_n[1..2]

HSMC_CLKOUT_p[1..2]

HSMC_SDA

HSMC_RX_n[4..16]

LED[0..3]

HSMC_TX_p[4..16]

LF_TDOLF_TDI

HSMC_CLKOUT0 HSMC_CLKIN0

CONF

nCONFIG

CPU_RST_n

USB BLASTER PAGE 17

JTAG_TDI

JTAG_TMS

JTAG_TDO

CONF

JTAG_TCK

CONF_DONE

nCE

nSTATUS

FLASH_CE_n

LINK_D3 LINK_D0

LINK_D1

LINK_D2

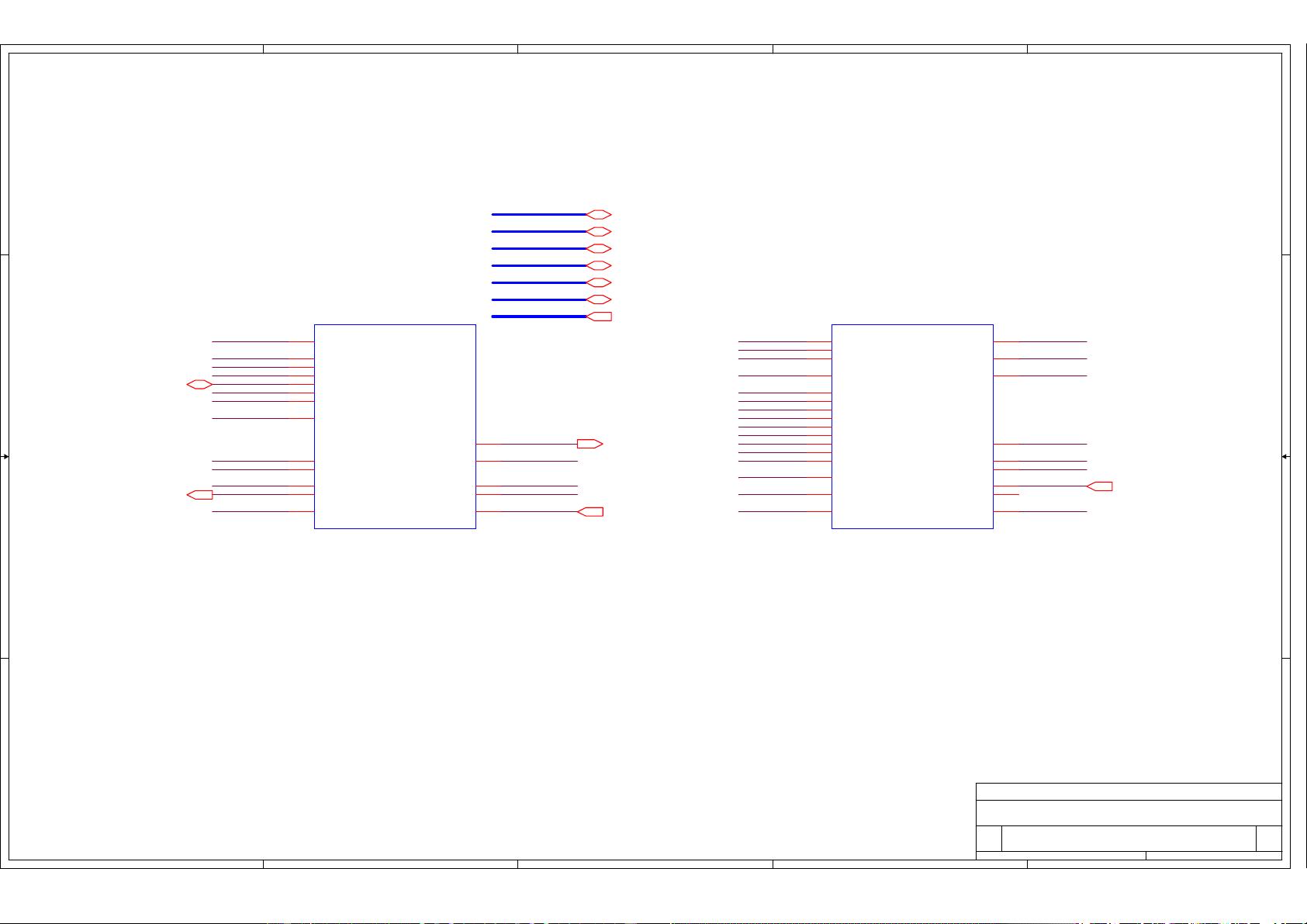

EP3C25 PAGE 4-8

KEY[0..3]

LED[0..3]

SRAM_WE_n

DDR_CLK_n

HSMC_TX_n[4..16]

HSMC_D[0..19]

DDR_RAS_n

SRAM_CLK

FLASH_CE_n

SRAM_CE1_n

DDR_CAS_n

DDR_CLK_p

FLASH_ADV_n

FLASH_CLK

DDR_DM0

DDR_DM1

FLASH_OE_n

HSMC_SCL

HSMC_RX_p[4..16]

SRAM_ADSC_n

FLASH_RESET_n

SRAM_OE_n

DDR_A[0..12]

DDR_DQ[0..15]

HSMC_CLKOUT_n[1..2]

DDR_DQS0

DDR_CKE

HSMC_CLKOUT_p[1..2]

DDR_DQS1

HSMC_SDA

HSMC_RX_n[4..16]

DDR_CS_n

DDR_WE_n

HSMC_TX_p[4..16]

DDR_BA0

FLASH_WE_n

SRAM_BE_n[0..3]

DDR_BA1

CIII_TDI

CIII_TDO

nCE

CONF_DONE

nSTATUS

CIII_TMS

CIII_TCK

nCONFIG

50MHz

FLASH_SRAM_A[1..25]

FLASH_SRAM_DQ[0..31]

HSMC_CLKIN_p[1..2]

HSMC_CLKIN_n[1..2]

HSMC_CLKIN0

HSMC_CLKOUT0

FLASH_WAIT

LINK_D0

LINK_D1

LINK_D2

LINK_D3

CPU_RST_n

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

HSMC_RX_p5

FLASH_SRAM_DQ19

HSMC_RX_n4

HSMC_TX_n5

HSMC_TX_p5

HSMC_TX_p4

HSMC_D1

HSMC_TX_p8

HSMC_TX_n15

HSMC_RX_n6

HSMC_RX_n9

HSMC_TX_p9

HSMC_RX_p7

HSMC_RX_p8

HSMC_RX_p9

HSMC_RX_n7

HSMC_RX_n8

HSMC_TX_n7

HSMC_TX_p7

HSMC_RX_p6

HSMC_TX_n6

HSMC_TX_p6

KEY0

KEY1

HSMC_D5

HSMC_D7

HSMC_D3

HSMC_TX_p15

HSMC_TX_n9

HSMC_TX_n8

HSMC_RX_n5

FLASH_SRAM_DQ1

HSMC_RX_p4

HSMC_TX_n4 HSMC_D0

HSMC_D2

HSMC_D4

FLASH_SRAM_DQ[0..31]

HSMC_D[0..19]

KEY[0..1]

HSMC_RX_p[4..16]

HSMC_RX_n[4..16]

HSMC_TX_p[4..16]

HSMC_TX_n[4..16]

FLASH_RESET_n

FLASH_CE_n

HSMC_SDA

HSMC_SCL

CPU_RST_n

Title

Size Document Number Rev

Date: Sheet

of

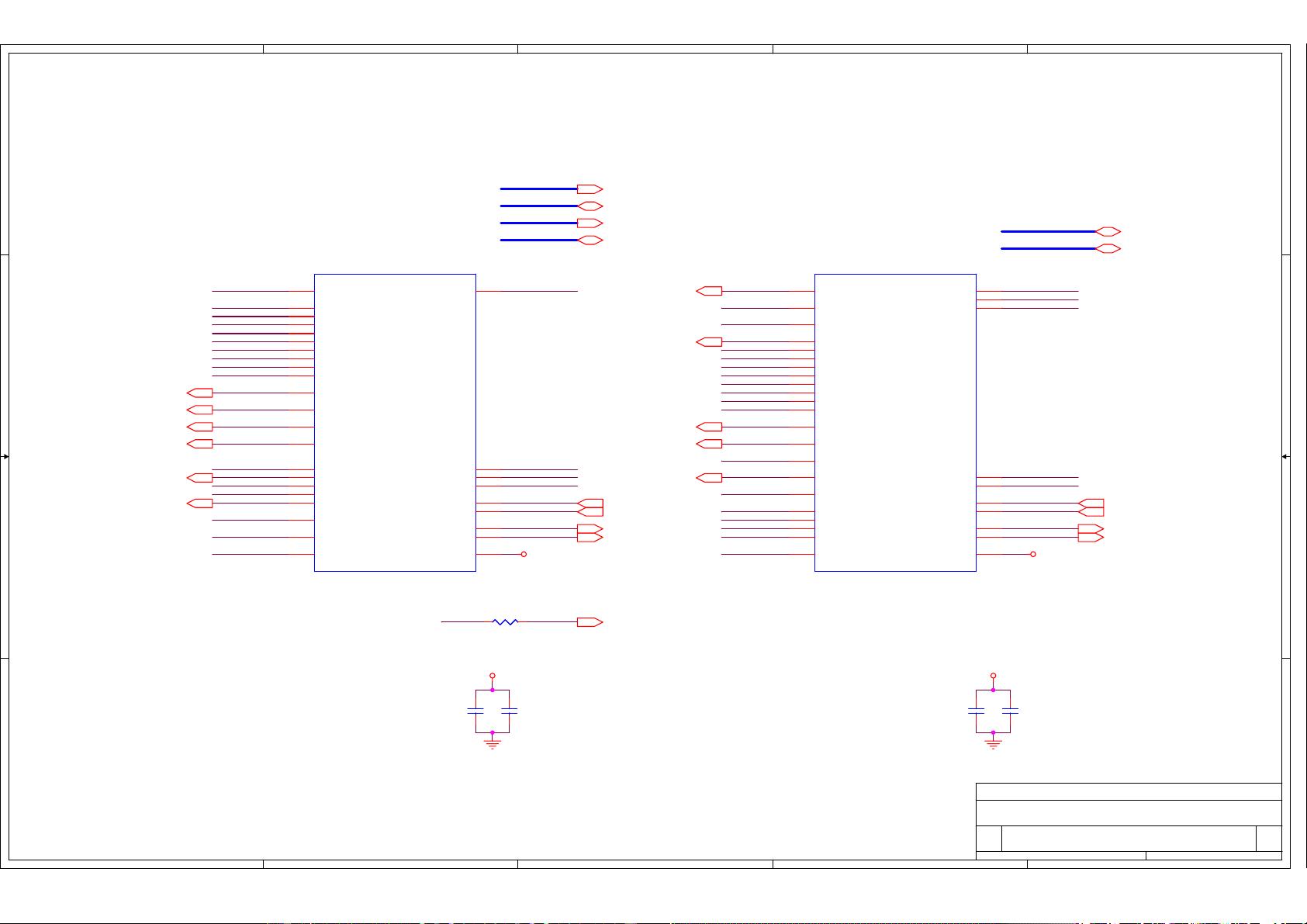

EP2C35 BANK1(I/O : 2.5V) and BANK 2(I/O : 2.5V) 1.2

Altera Cyclone III Eval Board

B

417Tuesday, April 17, 2007

Title

Size Document Number Rev

Date: Sheet

of

EP2C35 BANK1(I/O : 2.5V) and BANK 2(I/O : 2.5V) 1.2

Altera Cyclone III Eval Board

B

417Tuesday, April 17, 2007

Title

Size Document Number Rev

Date: Sheet

of

EP2C35 BANK1(I/O : 2.5V) and BANK 2(I/O : 2.5V) 1.2

Altera Cyclone III Eval Board

B

417Tuesday, April 17, 2007

BANK 2

EP3C25F324

U1B

BANK 2

EP3C25F324

U1B

LVDSL_9P/DQ3L0

L2

LVDSL_9N/DQ3L1

L1

LVDSL_7P/DQ1L6

K2

LVDSL_7N/DQ1L7

K1

LVDSL_8P/DQ1L8

K5

LVDSL_10P/DQ3L2

L4

LVDSL_10N/DQ3L3

L3

LVDSL_12P/DQ3L4

P2

LVDSL_12N/DQ3L5

P1

LVDSL_13P/DQ3L6

R2

LVDSL_14P/DQ3L7

T3

LVDSL_14N/DQ3L8

R3

LVDSL_8N/DM1L

L5

LVDSL_15N/DM3L

R4

LVDSL_11P/DQS1L

M2

DQS3L

M5

LVDSL_11N

M1

LVDSL_15P

R5

LVDSL_13N

R1

IO2_0

L6

IO/RDN1

T1

IO/RUP1

T2

CLK3/LVDSCLK1n

N1

CLK2/LVDSCLK1p

N2

IO/VREF0B2

M3

BANK 1

EP3C25F324

U1A

BANK 1

EP3C25F324

U1A

LVDSL_1P/DQ1L0

B2

LVDSL_2N/DQ1L1

C1

LVDSL_3P/DQ1L2

D2

LVDSL_4N/DQ1L3

E1

LVDSL_5P/DQ1L4

G2

LVDSL_5N/DQ1L5

G1

DQS2L

D3

LVDSL_6P/DQS0L

H2

LVDSL_1N

B1

LVDSL_2P

C2

LVDSL_3N/DATA1

D1

LVDSL_6N

H1

IO/nRESET

C3

IO1_0

H6

CLK1/LVDSCLK0n

F1

CLK0/LVDSCLK0p

F2

IO/VREF0B1

F3

LVDSL_4P/FLASH_nCE

E2

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

DDR_A3

DDR_DQ1

DDR_DQ2

DDR_DQ4

DDR_A6

DDR_A9

LED1

DDR_DQ15

DDR_DQ12

DDR_DQ14

DDR_DQ11

HSMC_RX_n15

HSMC_RX_p15 DDR_A5

DDR_A0

LED3

HSMC_D8

DDR_A2

DDR_A4

DDR_A1

DDR_A8

LED0

LED2

HSMC_RX_n16

HSMC_RX_p16

DDR_A7

LED3

DDR_DQ3

DDR_DQ7

DDR_DQ5

DDR_DQ6

DDR_DQ0

DDR_A10

DDR_A12

DDR_A11

DDR_DQ10

DDR_DQ8

DDR_DQ13

DDR_DQ9

HSMC_D18

HSMC_D12

HSMC_D14HSMC_D6

DDR_DQ[0..15]

DDR_A[0..12]

HSMC_D[0..19]

HSMC_CLKOUT_n2

HSMC_CLKOUT_p2

LED[0..3]

HSMC_RX_p[4..16]

HSMC_RX_n[4..16]

DDR_DM1

DDR_DM0

DDR_DQS1

DDR_DQS0

DDR_CKE

DDR_CS_n

50MHz

LINK_D0

DDR_CLK_n

DDR_CLK_p

DDR_CAS_n

DDR_BA1

DDR_BA0

LINK_D2

LINK_D1

LINK_D3

DDR_WE_n

DDR_RAS_n

VCC125 VCC125

VCC125 VCC125

Title

Size Document Number Rev

Date: Sheet

of

EP2C35 BANK3(I/O : 2.5V) and BANK 4(I/O : 3.3V) 1.2

Altera Cyclone III Eval Board

B

517Tuesday, April 17, 2007

Title

Size Document Number Rev

Date: Sheet

of

EP2C35 BANK3(I/O : 2.5V) and BANK 4(I/O : 3.3V) 1.2

Altera Cyclone III Eval Board

B

517Tuesday, April 17, 2007

Title

Size Document Number Rev

Date: Sheet

of

EP2C35 BANK3(I/O : 2.5V) and BANK 4(I/O : 3.3V) 1.2

Altera Cyclone III Eval Board

B

517Tuesday, April 17, 2007

BC4

0.1U

BC4

0.1U

TP 0TP 0

BC3

0.001U

BC3

0.001U

BC2

0.1U

BC2

0.1U

BC1

0.001U

BC1

0.001U

BANK 4

EP3C25F324

U1D

BANK 4

EP3C25F324

U1D

LVDSB_20N/DQ5B0

V16

DQ5B1

R11

LVDSB_19N/DQ5B2

V15

LVDSB_18N/DQ5B3

V14

LVDSB_18P/DQ5B4

U14

LVDSB_17P/DQ5B5

P10

LVDSB_16P/DQ5B6

U13

LVDSB_14P/DQ5B7

U12

LVDSB_13P/DQ5B8

U11

LVDSB_23N/DQS0B

R13

DQS2B

P12

LVDSB_16N/DQS4B

V13

LVDSB_13N

V11

LVDSB_14N

V12

LVDSB_17N

P11

LVDSB_19P

U15

LVDSB_20P

U16

LVDSB_21P

N10

LVDSB_21N

N11

LVDSB_22P

U17

LVDSB_22N

V17

LVDSB_24P

P13

LVDSB_24N

N12

LVDSB_25P

M13

LVDSB_25N

N13

IO/RDN2

T14

IO/RUP2

T13

CLK12/LVDSCLK7n

V10

CLK13/LVDSCLK7p

U10

PLL4_OUTn

V18

PLL4_OUTp

U18

IO/VREF0B4

T11

BANK 3

EP3C25F324

U1C

BANK 3

EP3C25F324

U1C

LVDSB_12P/DQ3B0

U8

LVDSB_11N/DQ3B1

V7

LVDSB_10N/DQ3B2

V6

LVDSB_10P/DQ3B3

U6

LVDSB_9N/DQ3B4

P9

LVDSB_8P/DQ3B5

R8

LVDSB_7N/DQ3B6

V5

LVDSB_6N/DQ3B7

V4

LVDSB_6P/DQ3B8

U4

DQS1B

P6

LVDSB_5N/DM3B

V3

LVDSB_12N/DM5B

V8

LVDSB_5P/DQS3B

U3

LVDSB_8N/DQS5B

T8

LVDSB_1P

U1

LVDSB_1N

V1

LVDSB_2P

M6

LVDSB_2N

N6

LVDSB_3P

T4

LVDSB_4N

N7

LVDSB_7P

U5

LVDSB_9P

P8

LVDSB_11P

U7

IO3_0

N8

IO3_1

N9

IO3_2

P7

CLK14/LVDSCLK6n

V9

CLK15/LVDSCLK6p

U9

PLL1_OUTn

V2

PLL1_OUTp

U2

IO/VREF0B3

T6

评论5