5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Drawing Title:

Size Document Number Rev

Date: Sheet of

Page Title:

Designer:

Drawn by:

Approved:

Multimedia Application Division,

Wireless & Mobile System Group

This document contains information proprietary to Freescale Semiconductor and shall not be used for

engineering design, procurement or manufacture in whole or in part without the express written permission

of Freescale Semiconductor.

SCH-26241 PDF: SPF-26241 D

i.MX28 EVK

Custom

Thursday, August 05, 2010

Cover

Mark Middleton

<Approver>

DRAWN_BY

1 18

____X____

Drawing Title:

Size Document Number Rev

Date: Sheet

of

Page Title:

Designer:

Drawn by:

Approved:

Multimedia Application Division,

Wireless & Mobile System Group

This document contains information proprietary to Freescale Semiconductor and shall not be used for

engineering design, procurement or manufacture in whole or in part without the express written permission

of Freescale Semiconductor.

SCH-26241 PDF: SPF-26241 D

i.MX28 EVK

Custom

Thursday, August 05, 2010

Cover

Mark Middleton

<Approver>

DRAWN_BY

1 18

____X____

Drawing Title:

Size Document Number Rev

Date: Sheet

of

Page Title:

Designer:

Drawn by:

Approved:

Multimedia Application Division,

Wireless & Mobile System Group

This document contains information proprietary to Freescale Semiconductor and shall not be used for

engineering design, procurement or manufacture in whole or in part without the express written permission

of Freescale Semiconductor.

SCH-26241 PDF: SPF-26241 D

i.MX28 EVK

Custom

Thursday, August 05, 2010

Cover

Mark Middleton

<Approver>

DRAWN_BY

1 18

____X____

ICAP Classification: FCP: FIUO: PUBI:

Page 14

Block Diagram

Table of Contents

Cover

Revision History

Page 1

Page 2

Page 3

Page 4

Page 5

Page 6

Page 7

Page 8

Page 9

Page 10

Page 11

Page 12

Page 13

i.MX28 EVK Board, Rev. D

Page 15

Page 16

Page 17

Page 18

CPU_Power&JTAG&ADC&USB

CPU_EMI&LCD

CPU_GPMI&ENET&UART&SSP&SAIF

DDR2

NAND & SD Card

Audio&SPDIF

Ethernet

USB

UART

CAN

Power Supply

Boot&UI&ID

JTAG&ETM

LCD Connector&Expansion Port

RIB&SPI&I2C&ADC

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Drawing Title:

Size Document Number Rev

Date: Sheet of

Page Title:

ICAP Classification: FCP: FIUO: PUBI:

SCH-26241 PDF: SPF-26241 D

i.MX28 EVK

C

Thursday, August 05, 2010

Revison History

2 18

___ ___

X

Drawing Title:

Size Document Number Rev

Date: Sheet

of

Page Title:

ICAP Classification: FCP: FIUO: PUBI:

SCH-26241 PDF: SPF-26241 D

i.MX28 EVK

C

Thursday, August 05, 2010

Revison History

2 18

___ ___

X

Drawing Title:

Size Document Number Rev

Date: Sheet

of

Page Title:

ICAP Classification: FCP: FIUO: PUBI:

SCH-26241 PDF: SPF-26241 D

i.MX28 EVK

C

Thursday, August 05, 2010

Revison History

2 18

___ ___

X

Original Release

Revision History

1, change all the boot mode resistors (R244, R246, R248, R250, R345, R346, R347, R352, R336, R337, R335, R338) to 10 Kohms.

2, C180 (reset pin external capacitor) needs to change to 0.01uF. This is to ensure the reset persistant bit is reset properly to 0 after startup after a power cycle.

3, Change the USB5V and WALL 5V selection method to use S16 to switch the sources onto the VDD5V pin. 02

4, Change the LCD Backlight supply to be powered from VDD4P2 by default. Add a FET (switched by VDD_5V) from LI-ION_BATTERY to VDD4P2 to improve efficiency.

Also add an option to power the LCD backlight from WALL_5V_IN for very large displays (with very high backlight current requirements).

5, Change to the new 5V reset circuit to match the MX28 mDDR CPU card.

6, Change the COM pin of the LTC2495 to 1/2 of the VCC_ID supply by adding a 47K resistor between VDD_ID and COM and GND and COM.

This is to fix the ADC readings and to increase the ADC range to full supply voltage.

7, On U63, connect pins 7 and 8 (VREF2 and EN) together and then connect these two pins to the VDDIO_ID net with a 200k resistor.

If pins 7 and 8 (VREF2 and EN) are connected directly to VDDIO_ID, U63 could potentially backpower the VDDIO_3V3 rail.

8, The current GND test points are small and alligator clips easily fall off. Change TP12, TP14, TP11, and TP13 to Agile part number 211-30043 and label as "GND" on the top silkscreen with large font.

Add one addition 211-30043 "GND" test point somewhere in the middle of the board.

9, Add 0.02 ohm resistor in series with the main power supply signals for current measurement.

10, Add SPDIF connector - requested by marketing

11, Add GPMI_CE2, GPMI_CE3, GPMI_READY2, and GPMI_READY3 signal connections to NAND flash connector, J93.

12, Change USB Host and USB OTG power from WALL 5V net to 5V net. This is to meet the software debugging requirement so the system is able to provide a Host 5V supply (from USB0)

when connected to a battery power supply (no WALL 5V supply).

13, Rotate the NAND flash connector 180 degrees to be compatible with the legacy NAND flash d-cards.

14, Need to change to the LTC2495, 16 channel ADC, (same as on the Armadillo 2 board) so that we can add the CPU_ID0 and CPU_ID1 ADC channels.

When adding the LTC2495, all ADC channels need to have a 10K pull-up resistor. In addition, there should be a 10K pull-down resistor added on the CPU_ID1 (ADC channel 13), which identifies the

board as the MX28 DDR2 rev B EVK, per the master ID table on the wiki.

15, Add 5 pin header (J96) to be convinient for customer to test their own kinds of touch panels.

16, Add the same DC overvoltage protection circuit as on the Armadillo 2 main board.

17, Add TVS diodes (agile part # 480-77934) at the VDD5V input pin of the MX28 and at the 5V adapter input.

1, Change WALL 5V detection circuit.

2, Remove D15

3, Move R265 to RESETN net

4,Change OverVoltage LED indication circuit.

5, PCA9306 pin 1 and the LTC2495 Fo pin are connected to GND. The LTC2495 CA1 pin is connected to R385.

6,connect the following pins on the NAND flash connector (J93) to GND: 1, 2, 11, 12, 21, 22, 31, 32, 41, 42, 51, 52.

7,U7 connects to WALL_5V_IN instead of 5V

8, Add 10K pull-up resistor to USB0_ID

9, Change C28 to 1000pF from 0.01uF.

1. Fixed DRC errors.

2. Added GPMI_READY2, READY3, CE2, CE3 connections to the MX28 (shared with CAN0 and CAN1 pins).

1. Added common mode choke and EMI capacitive filter at the input of the 5V DC adapter for EMI suppression.

2. Swapped the pin 1 and 3 connections on J85.

3. Increased the voltage rating of C159 to avoid damaging the capacitor when a high voltage adapter is plugged in.

4. Added additional 10uF capacitor on the WALL_5V_IN net after Q15.

5. Added a ferrite bead on the HEADPHONE_DETECT line of J80 to reduce the board radiated emissions.

6. Changed the FB1-FB6 ferrite beads to higher impedance and wider bandwidth frequency performance ferrites to reduce the board radiated emissions.

7. Added a ferrite bead on the USB_0_ID signal near the USB OTG connector (J82).

8. Added ferrite beads on the RS232 port connector signals.

REV C: 6/11/2010, Jamie Happ

REVB: 04/15/2010, Jamie Happ

REVB: 04/09/2010, Alfred Liu

REVB: 03/10/2010, Alfred Liu

REVA: 11/04/2009, Alfred Liu

REV D: 8/04/2010, Jamie Happ

1. Connected pin 5 of J83 to GND.

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Drawing Title:

Size Document Number Rev

Date: Sheet of

Page Title:

ICAP Classification: FCP: FIUO: PUBI:

SCH-26241 PDF: SPF-26241 D

i.MX28 EVK

B

Thursday, August 05, 2010

Block Diagram

3 18

___ ___

X

Drawing Title:

Size Document Number Rev

Date: Sheet

of

Page Title:

ICAP Classification: FCP: FIUO: PUBI:

SCH-26241 PDF: SPF-26241 D

i.MX28 EVK

B

Thursday, August 05, 2010

Block Diagram

3 18

___ ___

X

Drawing Title:

Size Document Number Rev

Date: Sheet

of

Page Title:

ICAP Classification: FCP: FIUO: PUBI:

SCH-26241 PDF: SPF-26241 D

i.MX28 EVK

B

Thursday, August 05, 2010

Block Diagram

3 18

___ ___

X

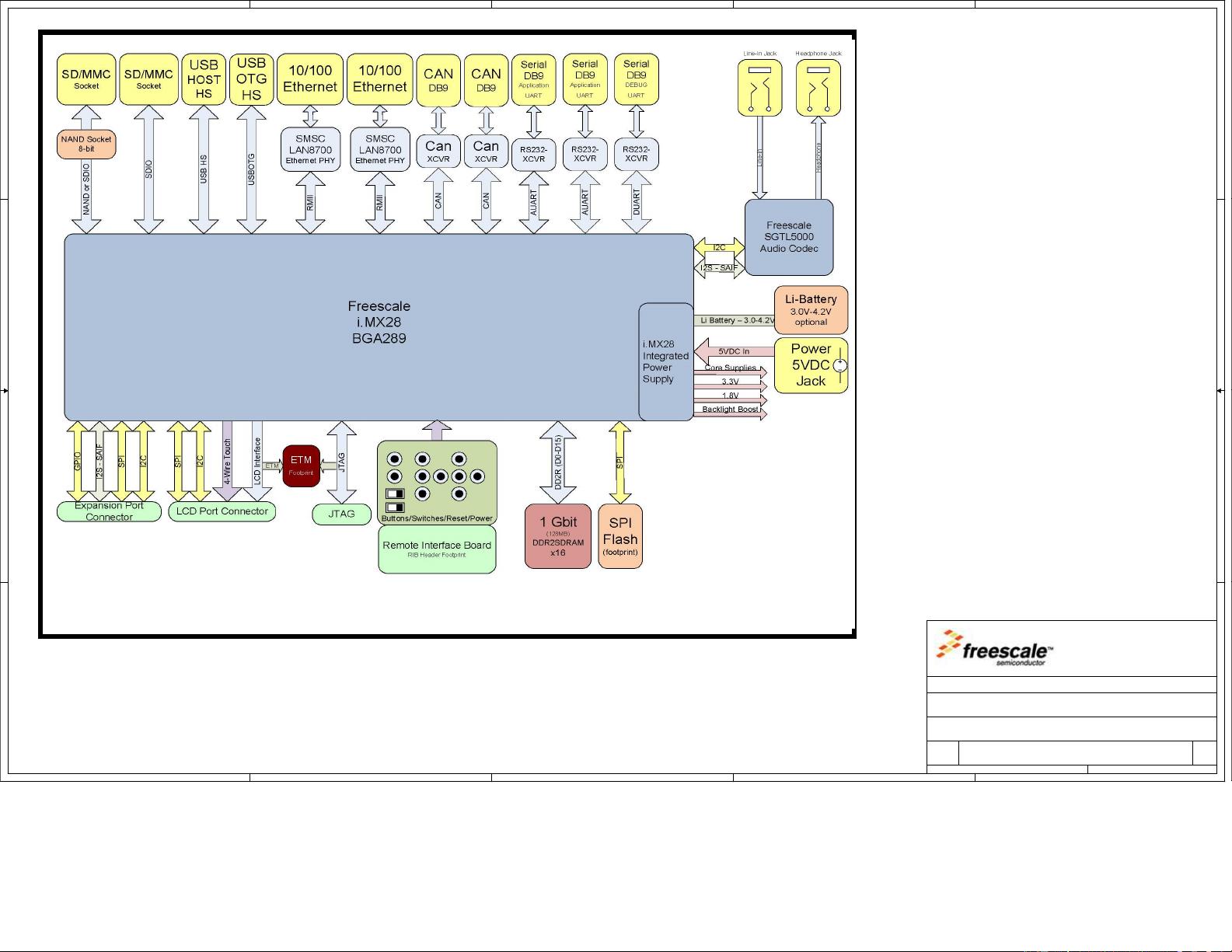

Block Diagram

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

LRADC0

LRADC1

LRADC2

LRADC3

LRADC4

LRADC5

LRADC6

HSADC0

LRADC0

LRADC1

LRADC2

LRADC3

LRADC4

LRADC5

LRADC6

HSADC0

GND

LI-ION_BATTERY

VDDXTAL

GND

GND

GND

GND

DCDC_VDDIO

DCDC_VDDA

DCDC_VDDD

VDD1P5VDD1P5

DCDC_VDDIO

DCDC_VDDA

DCDC_VDDD

VDD4P2

LI-ION_BATTERY

GND

VDD4P2

GND

GND

VDDIO_3V3

VDDIO_3V3

VDDD

VDDIO_3V3

VDDIO_1V8

VDDIO33_EMI

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

VDDIO_EMI

VDDIO_EMI

VDDA_1V8

GND

VDD_5V

GND

GND

USB_1_DM (11)

USB_1_DP (11)

USB_0_DM (11)

USB_0_DP (11)

JTAG_TDI (16)

JTAG_TMS (16)

JTAG_TCK (16)

JTAG_RTCK (16)

JTAG_TDO (16)

JTAG_TRST (16)

PSWITCH (15,16)

RESETN (15,18)

LRADC0 (14)

LRADC1 (15,18)

LRADC2 (17)

LRADC3 (17)

LRADC4 (17)

LRADC5 (17)

LRADC6 (17,18)

HSADC0 (18)

Drawing Title:

Size Document Number Rev

Date: Sheet of

Page Title:

ICAP Classification: FCP: FIUO: PUBI:

SCH-26241 PDF: SPF-26241 D

i.MX28 EVK

C

Thursday, August 05, 2010

CPU_Power&JTAG&ADC&USB

4 18

___ ___

X

Drawing Title:

Size Document Number Rev

Date: Sheet

of

Page Title:

ICAP Classification: FCP: FIUO: PUBI:

SCH-26241 PDF: SPF-26241 D

i.MX28 EVK

C

Thursday, August 05, 2010

CPU_Power&JTAG&ADC&USB

4 18

___ ___

X

Drawing Title:

Size Document Number Rev

Date: Sheet

of

Page Title:

ICAP Classification: FCP: FIUO: PUBI:

SCH-26241 PDF: SPF-26241 D

i.MX28 EVK

C

Thursday, August 05, 2010

CPU_Power&JTAG&ADC&USB

4 18

___ ___

X

DEBUG=1 for ARM ETM.

DEBUG=0 for boudary scan.

DC-DC &JTAG&ADC

CPU Power

Add this circuit

for dampening a overshoot

when USB cable inserting.

C17

0.1UF

C17

0.1UF

C187

22UF

C187

22UF

R364

0.1

R364

0.1

C195

10uF

C195

10uF

C24

0.1UF

C24

0.1UF

C2

0.1UF

C2

0.1UF

C37

0.1UF

C37

0.1UF

C204

0.01UF

C204

0.01UF

C38

0.01UF

C38

0.01UF

Y1

32.768KHZ

Y1

32.768KHZ

12

C40

1UF

C40

1UF

R363

0.1

R363

0.1

C92

1UF

C92

1UF

C49

0.1UF

C49

0.1UF

R366

0.1

R366

0.1

R10 10KR10 10K

C182

0.1UF

C182

0.1UF

R351

1

R351

1

R354 1M

DNP

R354 1M

DNP

C202

0.01UF

C202

0.01UF

C59

10PF

C59

10PF

C47

0.1UF

C47

0.1UF

C118

0.1UF

C118

0.1UF

C191

10uF

C191

10uF

R18 0R18 0

C27

1UF

C27

1UF

C56

0.1UF

C56

0.1UF

C16

0.1UF

C16

0.1UF

C45

0.1UF

C45

0.1UF

C25

0.01UF

C25

0.01UF

C3

1UF

C3

1UF

C36

0.1UF

C36

0.1UF

D1

MBR120VLSFT1G

D1

MBR120VLSFT1G

21

C186

22UF

C186

22UF

C194

10uF

C194

10uF

C18

0.01UF

C18

0.01UF

C55

0.1UF

C55

0.1UF

C33

0.1UF

C33

0.1UF

C43

0.01UF

C43

0.01UF

C57

10PF

C57

10PF

C20

1UF

C20

1UF

U1F

PCIMX287DJM4A

U1F

PCIMX287DJM4A

VSS1

A1

VSS2

A9

VSS3

B7

VSS4

C16

VSS5

E5

VSS6

E15

VSS7

H3

VSS8

H9

VSS9

H10

VSS10

H11

VSS11

H12

VSS12

H16

VSS13

J11

VSS14

J12

VSS15

J15

VSS16

K9

VSS17

K10

VSS18

K11

VSS19

L10

VSS20

L11

VSS21

M14

VSS22

N4

VSS23

U1

VDDIO33_8

A7

VSSA2_A

B11

VSSA1

B13

VDDA1

C13

VDDIO33_0

E6

VDDIO33_7

E16

VDDIO18_0

F8

VDDIO18_1

F9

VDDIO18_2

G8

VDDIO18_3

G9

VDDD0

F10

VDDD1

F11

VDDD2

F12

VDDD3

G10

VDDD4

G11

VDDD5

G12

VDDD6

K12

VDDIO_EMI_8_1

G13

VDDIO33_5_1

H8

VDDIO33_5_2

J8

VDDIO33_5_3

J9

VDDIO33_5_4

J10

VSSIO_EMI10

F14

VSSIO_EMI9

F16

VDDIO_EMI_8_2

G15

VDDIO_EMI_8_3

G17

VDDIO33_1

G3

VSSIO_EMI8

H14

VDDIO_EMIQ2

J13

VDDIO_EMIQ1

K15

VSSIO_EMI7

L12

VDDIO_EMI_7

L13

VDDIO_EMI_0

M10

VDDIO_EMI_3_1

M11

VDDIO_EMI_3_2

M12

VSSIO_EMI6

M16

VDDIO33_4

N3

VDDIO_EMI_3_3

N13

VDDIO_EMI_6

N15

VDDIO33_EMI

N17

VDDIO_EMI_1

P11

VSSIO_EMI4

P14

VSSIO_EMI5

P16

VSSIO_EMI_11

R10

VSSIO_EMI1

R12

VDDIO_EMI_3_4

R13

VDDIO_EMIQ0

R15

VSSIO_EMI3

T14

VSSIO_EMI2

U17

C7

1UF

C7

1UF

C205

0.01UF

C205

0.01UF

C31

0.1UF

C31

0.1UF

C189

22UF

C189

22UF

C9

0.01UF

C9

0.01UF

C52

0.1UF

C52

0.1UF

C5

0.01UF

C5

0.01UF

C11

1UF

C11

1UF

C190

10uF

C190

10uF

C15

0.1UF

C15

0.1UF

C53

0.1UF

C53

0.1UF

C54

0.1UF

C54

0.1UF

C29

0.1UF

C29

0.1UF

R11 0

DNP

R11 0

DNP

C23

0.1UF

C23

0.1UF

C39

0.1UF

C39

0.1UF

C183

0.1UF

C183

0.1UF

C41

0.1UF

C41

0.1UF

C104

0.1UF

C104

0.1UF

C193

10uF

C193

10uF

C50

0.1UF

C50

0.1UF

PMU

JTAG

LRADC

USB

XTAL

HSADC

U1E

PCIMX287DJM4A

PMU

JTAG

LRADC

USB

XTAL

HSADC

U1E

PCIMX287DJM4A

DCDC_LN

B17

DCDC_VDDA

B16

DCDC_VDDIO

C17

DCDC_VDDD

D17

DCDC_GND

A17

DCDC_LP

A16

DCDC_BATT

B15

VDD4P2

A13

BATTERY

A15

PSWITCH

A11

RESET

A14

VDD5V

E17

VDD1P5

D16

VDDXTAL

C12

RTC_XTALO

C11

RTC_XTALI

D11

XTALO

B12

XTALI

A12

JTAG_TMS

D12

JTAG_TCK

E11

JTAG_TDI

E12

JTAG_TDO

E13

JTAG_TRST

D14

JTAG_RTCK/GPIO4_20

E14

DEBUG

B9

TESTMODE

C10

USB0DM

A10

USB0DP

B10

USB1DM

B8

USB1DP

A8

HSADC0

B14

LRADC6

C14

LRADC5

D15

LRADC4

D13

LRADC3

D9

LRADC2

C8

LRADC1

C9

LRADC0

C15

C203

0.01UF

C203

0.01UF

C42

0.1UF

C42

0.1UF

C185

22UF

C185

22UF

C48

0.1UF

C48

0.1UF

R365

0.1

R365

0.1

C181

0.1UF

C181

0.1UF

C26

0.1UF

C26

0.1UF

C60

10PF

C60

10PF

C46

0.1UF

C46

0.1UF

C14

0.1UF

C14

0.1UF

C188

22UF

C188

22UF

C117

0.1UF

C117

0.1UF

24.0000 MHZ

Y2

24.0000 MHZ

Y2

12

C1

0.01UF

C1

0.01UF

C22

0.1UF

C22

0.1UF

C201

0.01UF

C201

0.01UF

C44

0.1UF

C44

0.1UF

C35

0.1UF

C35

0.1UF

C34

0.1UF

C34

0.1UF

C206

0.01UF

C206

0.01UF

C19

0.1UF

C19

0.1UF

C6

0.1UF

C6

0.1UF

C184

22UF

C184

22UF

C32

0.1UF

C32

0.1UF

R5 0 DNPR5 0 DNP

C192

10uF

C192

10uF

C51

0.1UF

C51

0.1UF

C58

10PF

C58

10PF

C10

0.1UF

C10

0.1UF

C13

0.1UF

C13

0.1UF

C30

0.1UF

C30

0.1UF

R355 10M

DNP

R355 10M

DNP

R6 0R6 0

L1

15UH

L1

15UH

1 2

C28

0.01UF

DNP

C28

0.01UF

DNP

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

EMI_DDR_OPEN

EMI_VREF

EMI_D01 (7)

EMI_D13 (7)

EMI_D05 (7)

EMI_D14 (7)

EMI_D08 (7)

EMI_D00 (7)

EMI_D06 (7)

EMI_D12 (7)

EMI_D07 (7)

EMI_D03 (7)

EMI_D09 (7)

EMI_D04 (7)

EMI_D11 (7)

EMI_D02 (7)

EMI_D10 (7)

EMI_D15 (7)

EMI_A07 (7)

EMI_A11 (7)

EMI_A05 (7)

EMI_A06 (7)

EMI_A04 (7)

EMI_A10 (7)

EMI_A09 (7)

EMI_A02 (7)

EMI_A12 (7)

EMI_A08 (7)

EMI_A01 (7)

EMI_A03 (7)

EMI_A00 (7)

EMI_A13 (7)

EMI_A14 (7)

EMI_DQS0N (7)

EMI_DQS1N (7)

EMI_DQM1 (7)

EMI_DQM0 (7)

EMI_DQS0 (7)

EMI_DQS1 (7)

EMI_CLK (7)

EMI_CLKN (7)

EMI_CKE (7)

EMI_CE0n (7)

EMI_CASn (7)

EMI_WEn (7)

EMI_RASn (7)

EMI_BA0 (7)

EMI_BA1 (7)

EMI_BA2 (7)

EMI_ODT0 (7)

LCD_D08 (16,17)

LCD_D09 (16,17)

LCD_D11 (16,17)

LCD_D12 (16,17)

LCD_D13 (16,17)

LCD_D14 (16,17)

LCD_D15 (16,17)

LCD_D16 (16,17)

LCD_D20 (17)

LCD_D21 (17)

LCD_D22 (17)

LCD_D23 (17)

LCD_D19 (17)

LCD_D18 (16,17)

LCD_D17 (16,17)

LCD_D04 (15,16,17)

LCD_D07 (17)

LCD_D05 (15,17)

LCD_D06 (15,17)

LCD_D10 (16,17)

LCD_D00 (15,16,17)

LCD_D02 (15,16,17)

LCD_D03 (15,16,17)

LCD_D01 (15,16,17)

LCD_CS (17)

LCD_RD_E (17)

LCD_WR_RWN (17)

LCD_RS (15,17)

LCD_PWR_EN (17)

SAIF1_SDATA1_CONN (16,17)

SAIF1_MCLK_CONN (16,17)

I2C_INT (17)

SAIF1_SDATA0_CONN (17)

Drawing Title:

Size Document Number Rev

Date: Sheet of

Page Title:

ICAP Classification: FCP: FIUO: PUBI:

SCH-26241 PDF: SPF-26241 D

i.MX28 EVK

C

Thursday, August 05, 2010

CPU_EMI&LCD

5 18

___ ___

X

Drawing Title:

Size Document Number Rev

Date: Sheet

of

Page Title:

ICAP Classification: FCP: FIUO: PUBI:

SCH-26241 PDF: SPF-26241 D

i.MX28 EVK

C

Thursday, August 05, 2010

CPU_EMI&LCD

5 18

___ ___

X

Drawing Title:

Size Document Number Rev

Date: Sheet

of

Page Title:

ICAP Classification: FCP: FIUO: PUBI:

SCH-26241 PDF: SPF-26241 D

i.MX28 EVK

C

Thursday, August 05, 2010

CPU_EMI&LCD

5 18

___ ___

X

EMI DDR2

LCD&SAIF1

Short to match trace length to CLK+DATA signals

TP1TP1

R13 0R13 0

TP2TP2

EMI

U1A

PCIMX287DJM4A

EMI

U1A

PCIMX287DJM4A

EMI_CAS

U16

EMI_RAS

R16

EMI_WE

T15

EMI_CE0

P12

EMI_CE1

P9

EMI_DDR_OPEN

K14

EMI_DDR_OPEN_FB

L15

EMI_CLK

L16

EMI_CLK

L17

EMI_CKE

T13

EMI_BA2

N12

EMI_BA1

T12

EMI_BA0

T16

EMI_A00

U15

EMI_A01

U12

EMI_A02

U14

EMI_A03

T11

EMI_A04

U10

EMI_A05

R11

EMI_A06

R9

EMI_A07

N11

EMI_A08

U9

EMI_A09

P10

EMI_A10

U13

EMI_A11

T10

EMI_A12

U11

EMI_A13

T9

EMI_A14

N10

EMI_ODT1

T17

EMI_VREF1

K13

EMI_VREF0

R14

EMI_ODT0

R17

EMI_DQM1

F15

EMI_DQM0

M15

EMI_DQS1

J17

EMI_DQS1

J16

EMI_DQS0

K17

EMI_DQS0

K16

EMI_D00

N16

EMI_D01

M13

EMI_D02

P15

EMI_D03

N14

EMI_D04

P13

EMI_D05

P17

EMI_D06

L14

EMI_D07

M17

EMI_D08

G16

EMI_D09

H15

EMI_D10

G14

EMI_D11

J14

EMI_D12

H13

EMI_D13

H17

EMI_D14

F13

EMI_D15

F17

R12 0R12 0

LCD

U1D

PCIMX287DJM4A

LCD

U1D

PCIMX287DJM4A

LCD_D00/ETM_DA0/GPIO1_0

K2

LCD_D01/ETM_DA1/GPIO1_1

K3

LCD_D02/ETM_DA2/GPIO1_2

L2

LCD_D03/ETM_DA3/ETM_DA8/GPIO1_3

L3

LCD_D04/ETM_DA4/ETM_DA9/GPIO1_4

M2

LCD_D05/ETM_DA5/GPIO1_5

M3

LCD_D06/ETM_DA6/GPIO1_6

N2

LCD_D07/ETM_DA7/GPIO1_7

P1

LCD_D08/ETM_DA8/ETM_DA3/GPIO1_8

P2

LCD_D09/ETM_DA9/ETM_DA4/GPIO1_9

P3

LCD_D10/ETM_DA10/GPIO1_10

R1

LCD_D11/ETM_DA11/GPIO1_11

R2

LCD_D12/ETM_DA12/GPIO1_12

T1

LCD_D13/ETM_DA13/GPIO1_13

T2

LCD_D14/ETM_DA14/GPIO1_14

U2

LCD_D15/ETM_DA15/GPIO1_15

U3

LCD_D16/ETM_DA7/GPIO1_16

T3

LCD_D17/ETM_DA6/GPIO1_17

R3

LCD_D18/ETM_DA5/GPIO1_18

U4

LCD_D19/ETM_DA4/GPIO1_19

T4

LCD_D20/ENET1_1588_EVENT2_OUT/ETM_DA3/GPIO1_20

R4

LCD_D21/ENET1_1588_EVENT2_IN/ETM_DA2/GPIO1_21

U5

LCD_D22/ENET1_1588_EVENT3_OUT/ETM_DA1/GPIO1_22

T5

LCD_D23/ENET1_1588_EVENT3_IN/ETM_DA0/GPIO1_23

R5

LCD_RD_E/LCD_VSYNC/ETM_TCTL/GPIO1_24

P4

LCD_WR_RWN/LCD_HSYNC/ETM_TCLK/GPIO1_25

K1

LCD_RS/LCD_DOTCLK/GPIO1_26

M4

LCD_CS/LCD_ENABLE/GPIO1_27

P5

LCD_RESET/LCD_VSYNC/GPIO3_30

M6

LCD_VSYNC/SAIF1_SDATA0/GPIO1_28

L1

LCD_HSYNC/SAIF1_SDATA1/ETM_TCTL/GPIO1_29

M1

LCD_DOTCLK/SAIF1_MCLK /ETM_TCLK/GPIO1_30

N1

LCD_ENABLE/GPIO1_31

N5