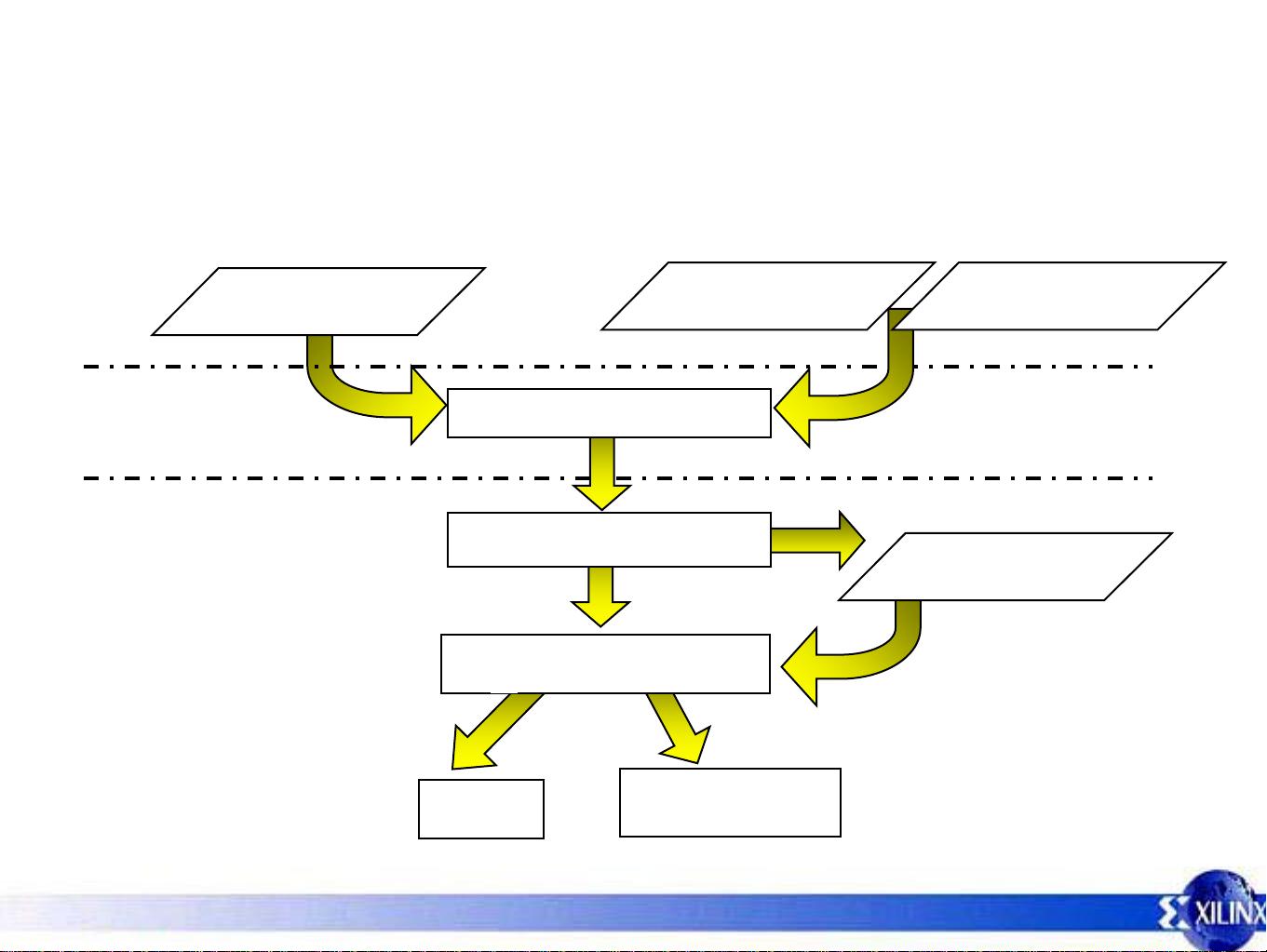

FPGA高级时序综合是数字电路设计中的一个重要环节,其目的是确保在目标设备上运行的电路能够满足其速度要求。时序综合涉及到建立时序约束,并且对电路的时序进行分析和优化,以确保数据在寄存器之间正确传输,并满足时钟频率的需求。 基本时序约束是整个时序综合的基础。这些约束包括定义时钟周期、时钟域、输入输出延迟、以及寄存器之间的建立和保持时间。在FPGA设计中,常用的是UCF文件(User Constraints File),通过Xilinx Constraints Editor GUI进行时序约束的编写和管理。时序约束使用特定的语法,例如PERIOD和OFFSET约束,指定时钟信号的有效时间和输入输出路径的延迟要求。 建立分组是时序约束中的一项重要技术,它允许我们将设计中的特定信号或逻辑块组成一个组,并对这个组施加时序约束。例如,使用TNM_NET声明的网络名称来创建一组,并通过PERIOD约束为这一组信号设置特定的时钟周期。 除了基本的时序约束之外,还有其他高级约束,比如设定最小脉宽(WIDTH)和多周期路径(MULTICYCLE_PATH)。这些约束对于处理复杂的时序问题和满足特殊的设计需求至关重要。 在进行时序综合时,要考虑到时钟偏移和时钟偏斜的影响。时钟偏移指的是时钟信号到达不同寄存器的延时差异,而时钟偏斜则是指在一个时钟周期内,时钟信号发生变化的时间差异。时钟偏斜会对电路的稳定性和性能产生影响,因此在约束中需要对它进行控制。 在时序综合流程中,首先在逻辑域进行设计,然后通过综合将设计转换为XNF/EDIF网表。接着是设计翻译阶段,生成NGDBuild文件,这是设计转换为可布局的逻辑单元的中间表示。然后是映射阶段,它将逻辑单元映射到FPGA的具体物理资源,这一阶段会生成PAR(布局布线)文件和PCF(物理约束)文件。最终阶段是物理域,FPGA编辑器根据物理约束对布局进行优化。 时序分析的一个重要方面是计算时钟周期。周期估计要综合考虑时钟到输出的延迟(Tcko)、网络延迟(Tnet1和Tnet2)、逻辑单元的处理延迟(Tlogic)以及时钟偏斜(Tclk_skew)等。时钟偏斜可能是正的也可能是负的,正偏斜表示数据到达稍早于时钟信号的上升沿,而负偏斜则相反。 时序约束的输入输出延时对于电路的稳定运行也是至关重要的。输入输出延时的设置必须考虑信号从FPGA的输入引脚到内部逻辑,以及从内部逻辑到输出引脚的传输时间。在设置延时时,必须考虑信号通过I/O引脚时的电气特性,以及信号在电路板上的传输特性。 时序报告提供了一个基本的时序分析结果概览,列出了时钟源、时钟信号上升沿的时间、以及时钟相位等信息。对于时序报告中的每个基本元素,如触发器,会显示时钟的名称和活跃边沿的时间点。 时序综合中的松弛度(Slack)是衡量时序裕度的一个重要指标。松弛度是可用时间与所需时间之差,表示电路中是否存在时间上的余地。松弛度为正值表示电路运行在安全裕度内,而松弛度为负值则意味着电路可能无法在规定时间内完成任务。 在进行时序约束时,Xilinx工具提供了一个高级界面用于输入和查看时序约束,包括时钟信号定义、时钟周期设置、偏移量、以及约束优先级等。约束的优先级决定了在发生冲突时哪个约束被优先考虑。这通常通过时序约束文件中的不同语句和它们的顺序来实现。 通过高级时序综合教程的学习,设计人员能够更加精确地控制FPGA的设计实现,以满足高速运行和高可靠性的要求。随着FPGA设计复杂性的增加,高级时序综合成为了不可或缺的一部分,对设计流程的优化起着至关重要的作用。

剩余83页未读,继续阅读

- 粉丝: 0

- 资源: 8

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功