没有合适的资源?快使用搜索试试~ 我知道了~

特权同学时序分析的笔记

温馨提示

试读

69页

该文档中包含了特权同学的绝大部分的时序分析的精华博文,对学习FPGA时序分析的同学有很大帮助。

资源推荐

资源详情

资源评论

Clock Specification —— Clock Groups 2011-09-24 09:50

Quartus II Handbook, Volume 3 6-37

时钟集合 Clock Groups

设计中存在着许多时钟 , 然而 , 并非所有时钟都相互关联 , 况且某些时钟间

相互关联是没有必要的 。 异步时钟就是不相关时钟 ( 异步时钟有不同的理想时钟

源 ) 。 专用时钟也不一定在同一时刻激活 ( 例如 , 多元时钟 ) 。 必须向 Quartus II

TimeQuest Timing Analyzer 指明相互排斥的时钟,从而阻止其把这些时钟作为

关联时钟进行分析。

使用 set_clock_groups 命令指明相互排斥或者异步的时钟 。 Example 6 – 12

展示了 set_clock_groups 命令及选项。

Example 6 – 12. set_clock_groups Command

set_clock_groups

[-asynchronous | -exclusive]

-group

[-group ]

[-group ] ...

Table 6 – 10 describes the options for the set_clock_groups command.

选项 描述

-asynchronous 异步时钟 —— 两个时钟没有相位关系并且不在同一时刻

激活

-exclusive 专有时钟 —— 两个时钟中仅有一个在特定时间激活。 2

选 1 时钟就是专有时钟的一个实例

-group 指定相互独有的时钟名。用于指定时钟名

Example 6 – 13 展示了 set_clock_groups 命令和等价命令 set_false_pat h

的用法。

Example 6 – 13. set_clock_groups Example

# Clocks A and C are never active when clocks B and D are active

set_clock_groups -exclusive -group {A C} -group {B D}

# Equivalent specification using false paths

set_false_path -from [get_clocks A] -to [get_clocks B]

set_false_path -from [get_clocks A] -to [get_clocks D]

set_false_path -from [get_clocks C] -to [get_clocks B]

set_false_path -from [get_clocks C] -to [get_clocks D]

set_false_path -from [get_clocks B] -to [get_clocks A]

set_false_path -from [get_clocks B] -to [get_clocks C]

set_false_path -from [get_clocks D] -to [get_clocks A]

set_false_path -from [get_clocks D] -to [get_clocks C]

Clock Specification —— Default Clock Constraints 2011-09-24 09:50

Quartus II Handbook, Volume 3 6-37

缺省时钟约束 Default Clock Constraints

为了提供彻底的时钟分析,如果你的设计中没有基本时钟约束, Quartus II

TimeQuest Timing Analyzer 在缺省时会自动的检测所有未被约束的时钟节点

。

Quartus II TimeQuest Timing Analyzer 使用以下命令产生 1GHz 的时钟约束你

的未约束时钟:

derive_clocks -period 1

独立的时钟约束(例如, create_clock, create_generated_clock )可能会

出现在设计中 。 这将导致不切实际的分析设计中的时序要求 。 derive_clocks 的

使用应该避免出现在最终的时序里。

缺省时钟约束仅仅被用于 Quartus II TimeQuest Timing Analyzer 检测所

有没有时钟连接的同步单元 。 例如 , 如果一个设计约束两个时钟 , 而仅有一个时

钟已经约束了,这将不会使用缺省时钟约束。然而,如果两个时钟都未被约束

,

那么会启动缺省时钟约束。

深入剖析 I/O 约束

题记 : 时序分析摸索了很久 , 看了很多资料 , 也反反复复的对比总结 , 然后思考

。

现在总算有点大彻大悟的感觉了 , 但是还不够有些东西理解的可能还不是那么深

入透彻 , 也喜欢把自己的思考过的东西拿出来和大家分享 , 更是希望大家能提出

一些看法,在不断的讨论总结中才会有进步。

Quartus II TimeQuest Timing Analyzer 综合设计约束支持设计管脚的约束

。

这些约束允许 Quartus II TimeQuest Timing Analyzer 执行系统静态时序分析

,

不仅包括 FPGA 的时序,而且包括了任何外部器件的时序以及板级时序参数。

输入输出延时 Input and Output Delay ( P57 )

使用输入输出延时约束来指定任何外部器件或者板级参数 。 当您应用这些约

束, Quartus II TimeQuest Timing Analyzer 将在整个系统执行静态时序分析 。

设置输入延时

Set Input Delay

set_input_delay 约束指定了某个管脚(器件 I/O )关于给定时钟的数据到

达时间。 Figure 6 – 26 展示了一个输入延时的路径。

使用 set_input_delay 命令来指定设计管脚的输入延时。 Example 6 – 18 展

示了 set_input_delay 命令及选项。

Example 6 – 18. set_input_delay Command

set_input_delay

-clock

[-clock_fall]

[-rise | -fall]

[-max | -min]

[-add_delay]

[-reference_pin ]

[-source_latency_included]

T

able 6 – 14. set_input_delay Command Options

选项 描述

-clock 指定时钟源

-clock_fall 指定数据到达时间为时钟下降沿

-rise | -fall 指定是时钟的上升沿或者下降沿延时

-max | -min 指定是数据的最大或者最小到达时间

-add_delay 另外增加一个延时,但是不会取代该管脚已经存在

的延时

-reference_pin 从设计中指定的管脚或节点确定源和网络潜伏期。

这有利于指定由某个时钟反馈的输出管脚相关的输

入延时。

-source_latency_

included

指定包括源潜伏延时值的输入延时值,因此任何分

配给时钟的源时钟潜伏期将被忽略。

指定延时值

指定目标管脚或者节点

如果您仅仅为输入延时值指定一个 -max 或者 -min 值,将会出现警告信息。

此时未设定的输入最小延时值或输入最大延时值的缺省值和另一方相同。同样

地,如果你仅仅为延时值指定一个 -rise 或者 -fall 值,也会出现警告信息。该

默认延时值也会以和输入最大和最小延时值一样的方式设置。

最大值被用于建立时间检测,而最小值被用于保持时间检测 。

默认情况下 , 输入延时 ( min/max, rise/fall ) 设置仅仅允许为一个 clock,

-clock_fall, -reference_pin 组合。为一个相同的管脚指定输入延时值,若不

想移除这些不同的 clock, -clock_fall, 或者 -reference_pin 原先的输入延时

设置,你必须指定 -add_delay 选项。当你指定了 -add_delay 选项,最坏的情况

值将被采用。

-rise 和 -fall 选项是相互排斥的, -min 和 -max 选项也是相互排斥的。

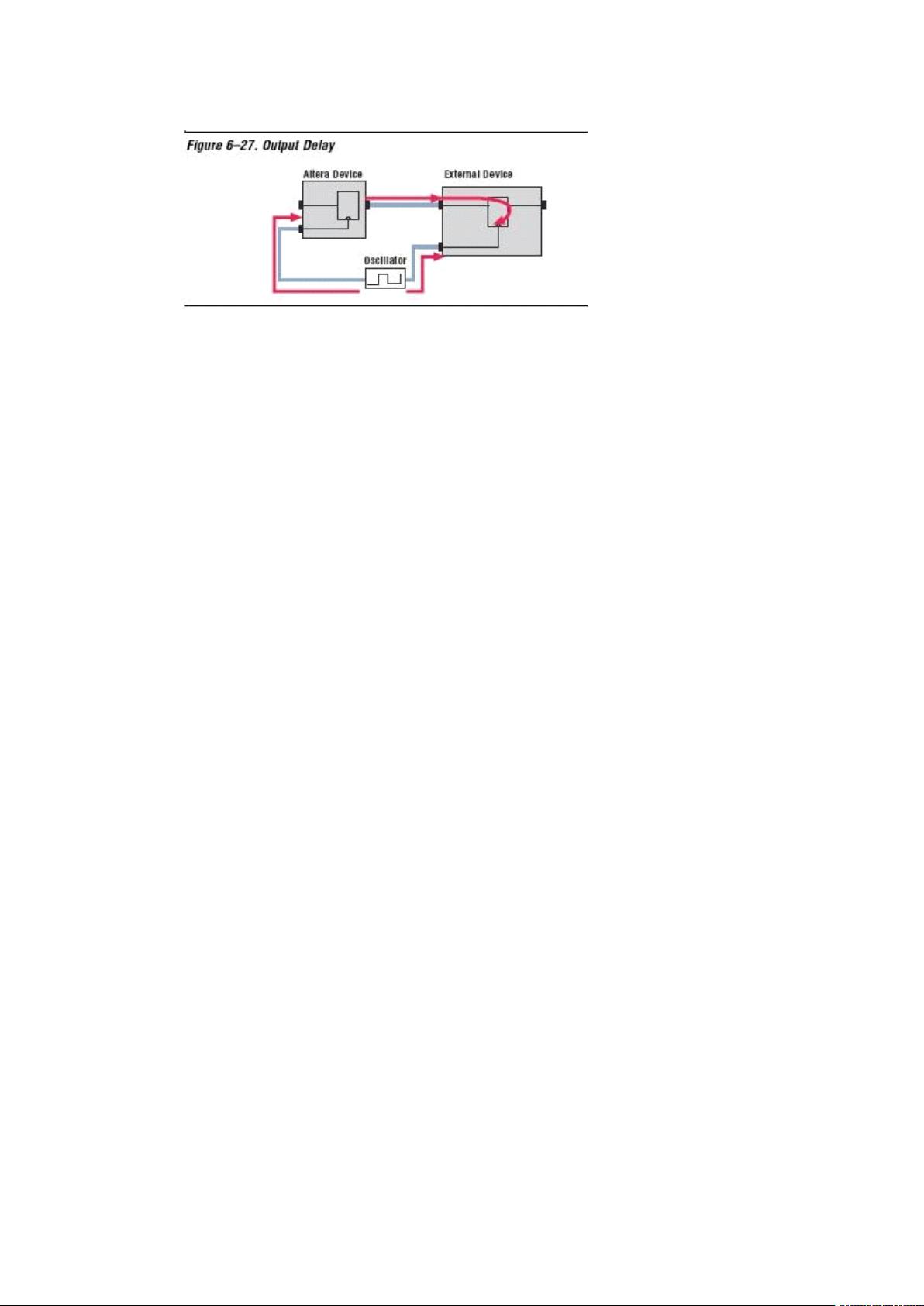

设置输出延时

Set Output Delay

set_output_delay 命令指定一个给定时钟相关管脚 ( 器件管脚 ) 的数据需要

时间。使用 set_output_delay 命令指定设计管脚的输出延时约束。 Figure 6 –

27 展示了一个输出延时路径。

剩余68页未读,继续阅读

资源评论

InvisiblehPerson2021-05-14感觉不错,试着看看

InvisiblehPerson2021-05-14感觉不错,试着看看 cocoshi122013-09-29好文章,不解释,而且很清晰

cocoshi122013-09-29好文章,不解释,而且很清晰

l941024324

- 粉丝: 0

- 资源: 9

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 二叉树7-1-1.cpp

- android 9.0 原生模拟器 签名文件

- 技术面试最后反问面试官的话 校招面试非技术问题有哪些 非技术问题如何回答.png

- NB-IOT-BC26全网通模块Altium+ CADENCE +PADS三种格式(原理图SCH+PCB封装库)文件.zip

- 基于微信小程序开发的校园失物招领系统源码毕业设计(优质项目源码).zip

- 词向量是一种将自然语言中的单词转换为数值向量的技术,它能够捕捉词义和上下文信息

- nmap与masscan的简单使用

- MyBatis动态SQL.pdf

- 基于stm32单片机protues仿真的温湿度控制系统设计(仿真图、源代码)

- 词向量:自然语言处理的基石

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功