SiT9102 LVPECL / HCSL / LVDS / CML 差分高速时钟

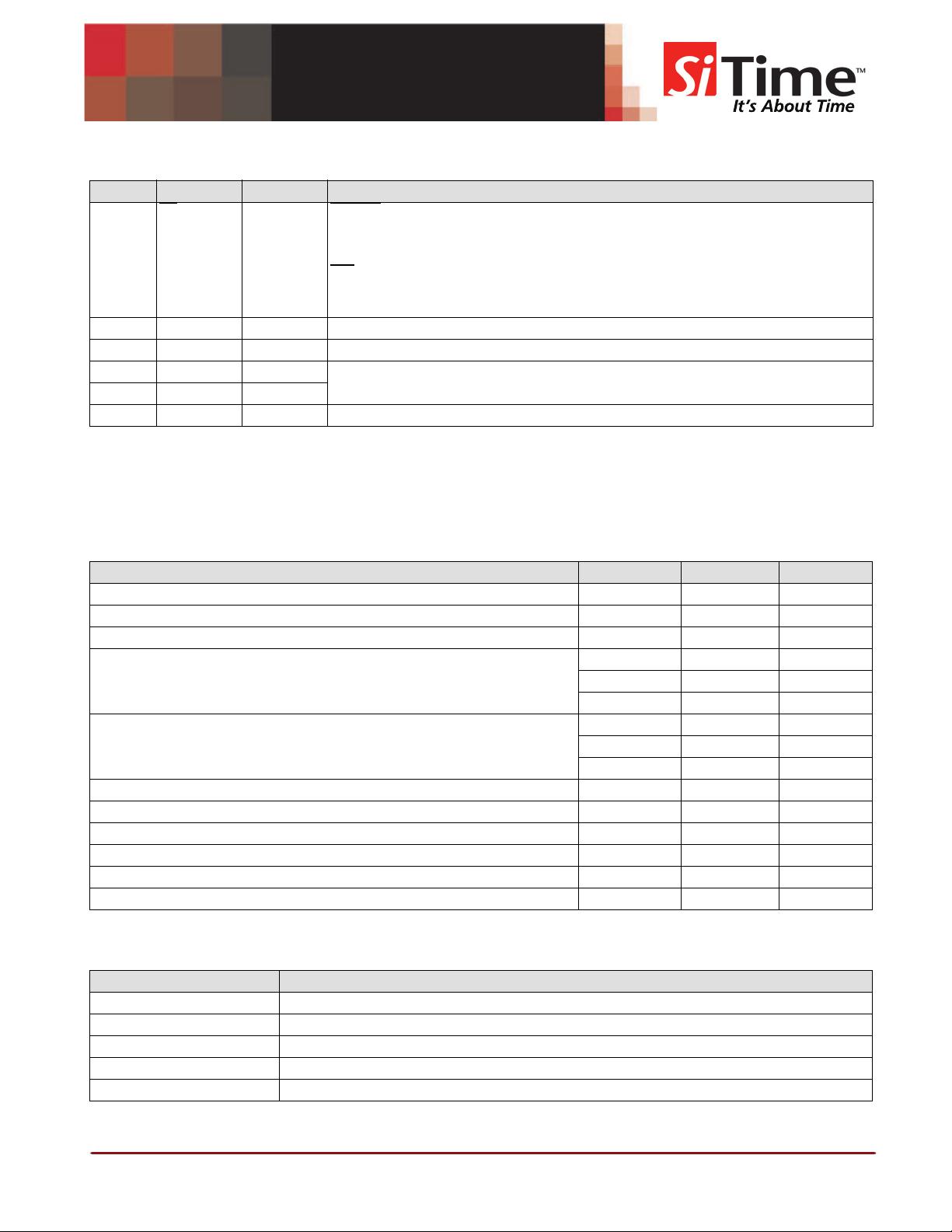

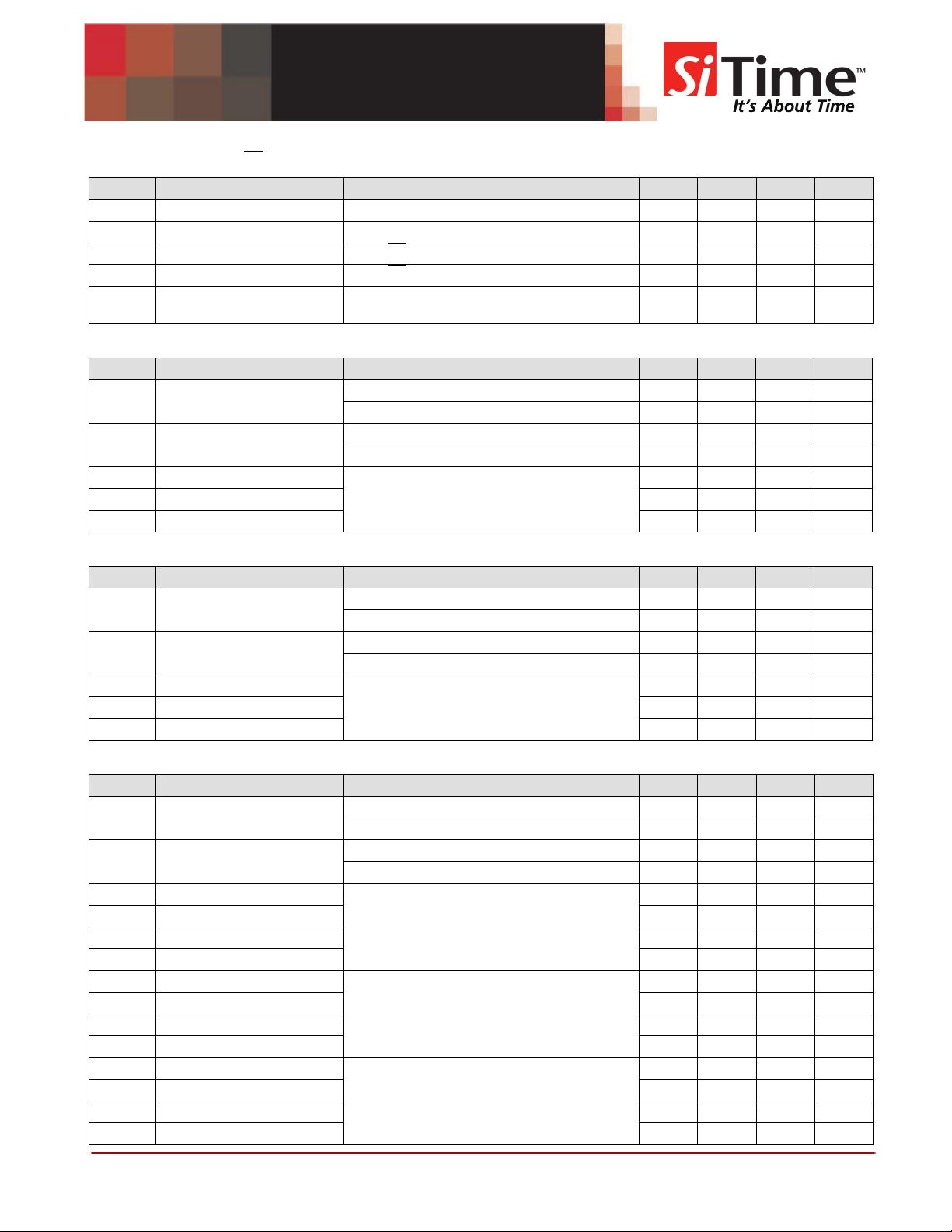

于传统石英、SAW和泛音谐振技术的传统差分振荡器在稳定度和可靠度上先天不足,SiT9121系列差分振荡器采用SiTime模拟CMOS和全硅MEMS技术研发,是唯一完美结合了超高性能和可编程功能的产品,其频率稳定度达10PPM、相位抖动低于0.6ps(femtosecond),市面上目前仅SiTime实现了这两项的完美结合。 SiT9121支持1-220Mhz之间任意频率,可精确到小数点后六位,确保发挥系统的最高性能。SiT9121同时输出支持 LVDS/LVPECL,经过50000G抗冲击及70G抗振测试,MTBF(平均无故障时间)达10亿小时。SiT9121和SiT9122系 列差分振荡器定位于高性能电信、存储和网络应用,如核心和边缘路由器,SATA、SAS、光纤通道主机总线适配器,云存储、服务器、无线基站和10G 以太网**机等。此外,每款产品都支持业界标准管脚配置,不需修改设计 或布板方式即可替换现有石英差分振荡器。 SiT9121差分振荡器具备下述功能及优点: . 仅500飞秒RMS相位抖动(12kHZ至20MHz),满足SONET等应用的苛刻要求 . 总频率稳定度达±10、±25及±50PPM,系统正时余量(timing margin)更佳 . 频率范围极广:SiT9121频率范围1至220MHz,SiT9122频率范围220至650MHz . 可编程频率精度达小数点后六位,确保发挥系统最高性能 . LVPECL及LVDS信号电平可调 . 通过50000G抗冲击及70G抗振测试,MTBF(平均无故障时间)达10亿小时,高稳定度应用首选 . 工作电压2.5V、3.3V均可 . 支持工业(-40至+85°C)及长时间商业(-20至+70°C)工作温度范围 . 业界标准针脚规格3.2×2.5mm,5.0×3.2mm,7.0×5.0mm封装 . 样品24小时内发货,生产前置时间仅2至4周 . FPGA产品首选高性能差分时钟振荡器 . 兼容工业标准封装: 3.2×2.5, 5.0×3.2 and 7.0×5.0 mmxmm . 超强抗震动、抗冲击能力,优异的温漂性能 . 如需220MHz以上频点的高性能差分晶振,推荐选择SiT9122系列

剩余12页未读,继续阅读

李诗旸2023-07-27这个文件描述了SiT9102 LVPECL / HCSL / LVDS / CML差分高速时钟的特性和性能,为人们在设计和测试中提供了很大的帮助。

李诗旸2023-07-27这个文件描述了SiT9102 LVPECL / HCSL / LVDS / CML差分高速时钟的特性和性能,为人们在设计和测试中提供了很大的帮助。 BellWang2023-07-27它提供了关于SiT9102 LVPECL / HCSL / LVDS / CML差分高速时钟的详细信息,让人们可以更好地了解和应用它们。

BellWang2023-07-27它提供了关于SiT9102 LVPECL / HCSL / LVDS / CML差分高速时钟的详细信息,让人们可以更好地了解和应用它们。 武藏美-伊雯2023-07-27这个文件对于需要使用高速时钟的人来说是一个非常有用的资源。

武藏美-伊雯2023-07-27这个文件对于需要使用高速时钟的人来说是一个非常有用的资源。 ShenPlanck2023-07-27这是一个优秀的文件,它为我们提供了关于SiT9102 LVPECL / HCSL / LVDS / CML差分高速时钟的全面信息,并以简单明了的方式向读者传达了这些信息。

ShenPlanck2023-07-27这是一个优秀的文件,它为我们提供了关于SiT9102 LVPECL / HCSL / LVDS / CML差分高速时钟的全面信息,并以简单明了的方式向读者传达了这些信息。 李多田2023-07-27它使用简洁的语言描述了SiT9102的功能和应用范围,让读者可以快速理解和应用这个产品。

李多田2023-07-27它使用简洁的语言描述了SiT9102的功能和应用范围,让读者可以快速理解和应用这个产品。

- 粉丝: 14

- 资源: 2

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜 信息提交成功

信息提交成功