没有合适的资源?快使用搜索试试~ 我知道了~

全相位频谱分析(apFFT)是传统FFT的一种改进算法,能改善FFT的栅栏效应和截断效应,具有频谱泄露少、相位不变的特性。介绍采用FPGA器件实现apFFT算法,精度高于模拟式测量,并且适用性强、成本低,所得到的QuratusII仿真结果与Matlab软件仿真结果一致。

资源推荐

资源详情

资源评论

基于基于FPGA的的apFFT算法实现算法实现

全相位频谱分析(apFFT)是传统FFT的一种改进算法,能改善FFT的栅栏效应和截断效应,具有频谱泄露少、相位

不变的特性。介绍采用FPGA器件实现apFFT算法,精度高于模拟式测量,并且适用性强、成本低,所得到的

QuratusII仿真结果与Matlab软件仿真结果一致。

摘摘 要:要: 全相位

关键词:关键词: 现场可编程门阵列;

全相位频谱分析apFFT(all phase FFT)是近几年提出的频谱分析方法,该方法具有比传统FFT更优良的频谱抑制性能;具有“

目前,通常采用两种途径通过硬件方式实现FFT算法:(1)使用DSP器件实现;(2)通过FPGA器件实现。一般来说,DSP器件

多用于数字信号处理领域,而且开发过程相对简单,易于实现,但速度较慢,无法完成对速度要求较高的算法。而FPGA器件

由于内部嵌入了硬件

1 全相位频谱分析全相位频谱分析

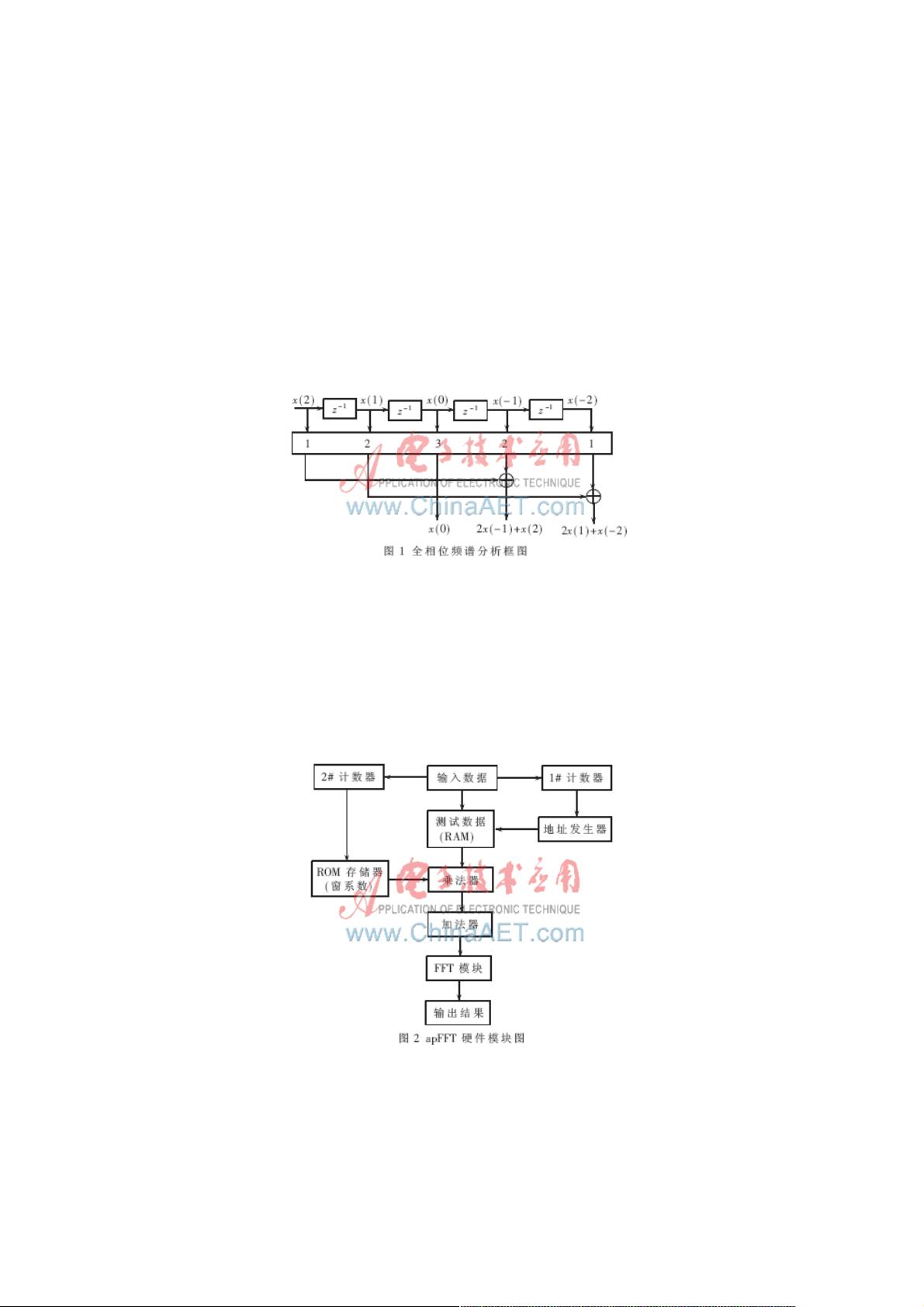

apFFT理论推导详见参考文献[1,2],本文以FFT点数N=3点为例简化此频谱分析图如图1。其中的卷积窗wc=[wc(-N+1),…,

wc(-1), wc(0), wc(1),…, wc(N-1) ] 由两个长度为N的对称窗卷积而来,用这个长为(2N-1)的卷积窗wc 对输入样本加窗后,再将

间隔为N的两数据平移相加生成N个数据y(n) (n=0,1,…,N-1),最后对y(n)进行FFT 即得谱分析结果。

2 软硬件简介软硬件简介

在FPGA开发过程中,常用的是VHDL和Verilog HDL语言。VHDL语言比较适合做大型的系统级设计,而Verilog HDL则适合

逻辑级、门级设计。所以,考虑到两种语言各自特点,本文选用VHDL语言完成设计。

采用FPGA实现apFFT算法,对硬件资源要求较高,故开发芯片选择Altera公司的

软件选用Altera公司开发的QuartusII平台。该软件提供了丰富的开发工具供用户使用,可以完成代码输入、编译、仿真以及

下载到芯片的全部功能。

3 apFFT模块设计模块设计

本文所设计的apFFT模块由三部分构成,分别为:地址发生模块、数据存储模块和FFT运算模块。各个模块间的关系如图2

所示。

3.1 地址发生模块地址发生模块

为了保证测试数据能够完整无误地输入到EP2C35F672C8,需要选择合适的存储地址来保存数据。本文以做8点FFT为例,

所涉及的所有数据总线宽度均为8 bit,序列长度取15 bit。为了保证15 bit的存储数据都能够及时存储到寄存器中,需要至少4 bit

的地址总线才能满足设计需求。

地址发生模块的结构体部分程序如图3所示。

资源评论

weixin_38654380

- 粉丝: 6

- 资源: 952

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功