没有合适的资源?快使用搜索试试~ 我知道了~

SRIO传输协议学习.docx

温馨提示

试读

25页

SRIO传输的技术协议和中文说明。RapidIO是一种非专有的高带宽系统级互连。它是一种分组交换互连,主要用作以每秒千兆字节性能级别进行芯片到芯片和板对板通信的系统内接口。该架构可用于连接的微处理器,内存和内存映射的I / O设备,这些设备在网络设备,内存子系统和通用计算中运行。

资源推荐

资源详情

资源评论

SRIO 传输协议学习

概述

SRIO KeyStone 设备中使用的 RapidIO 外设称为串行

RapidIO(SRIO)

RapidIO 是一种非专有的高带宽系统级互连。它是一种分组交换互连,主要用作以每秒千兆字节性

能级别进行芯片到芯片和板对板通信的系统内接口。该架构可用于连接的微处理器,内存和内存映

射的 I / O 设备,这些设备在网络设备,内存子系统和通用计算中运行。

RapidIO 被定义为三层架构层次结构。

•逻辑层:指定端点处理事务所需的协议,包括数据包格式。

•传输层:定义寻址方案以在系统内正确路由信息包。

•物理层:包含设备级接口信息,例如电气特性,错误管理数据和基本流量控制数据。

在 RapidIO 架构中,传输层的一个规范与逻辑层和物理层的不同规范兼容。

意指 SRIO 协议中,仅有传输层的协议时不变的,逻辑层与传输层的规范可以通过实际情况来做出

改变。

逻辑层: I/O SYSTEM、MessagePassing、Globally shared memory

物理层:8/16LP-LVDS、1x/4xLP Serial

笔者在此暂定使用 IO system 4x LP Serial 协议

SRIO 使用互连体系

独立于物理层实现的分组交换协议,类似于串行总线?

物理层接口协议

8/16 LP-LVDS 规范是点对点同步时钟源 DDR 接口

1x / 4x LP-Serial 规范是一种点对点交流耦合时钟恢复接口。(SerDes 串行器/解码器技术)

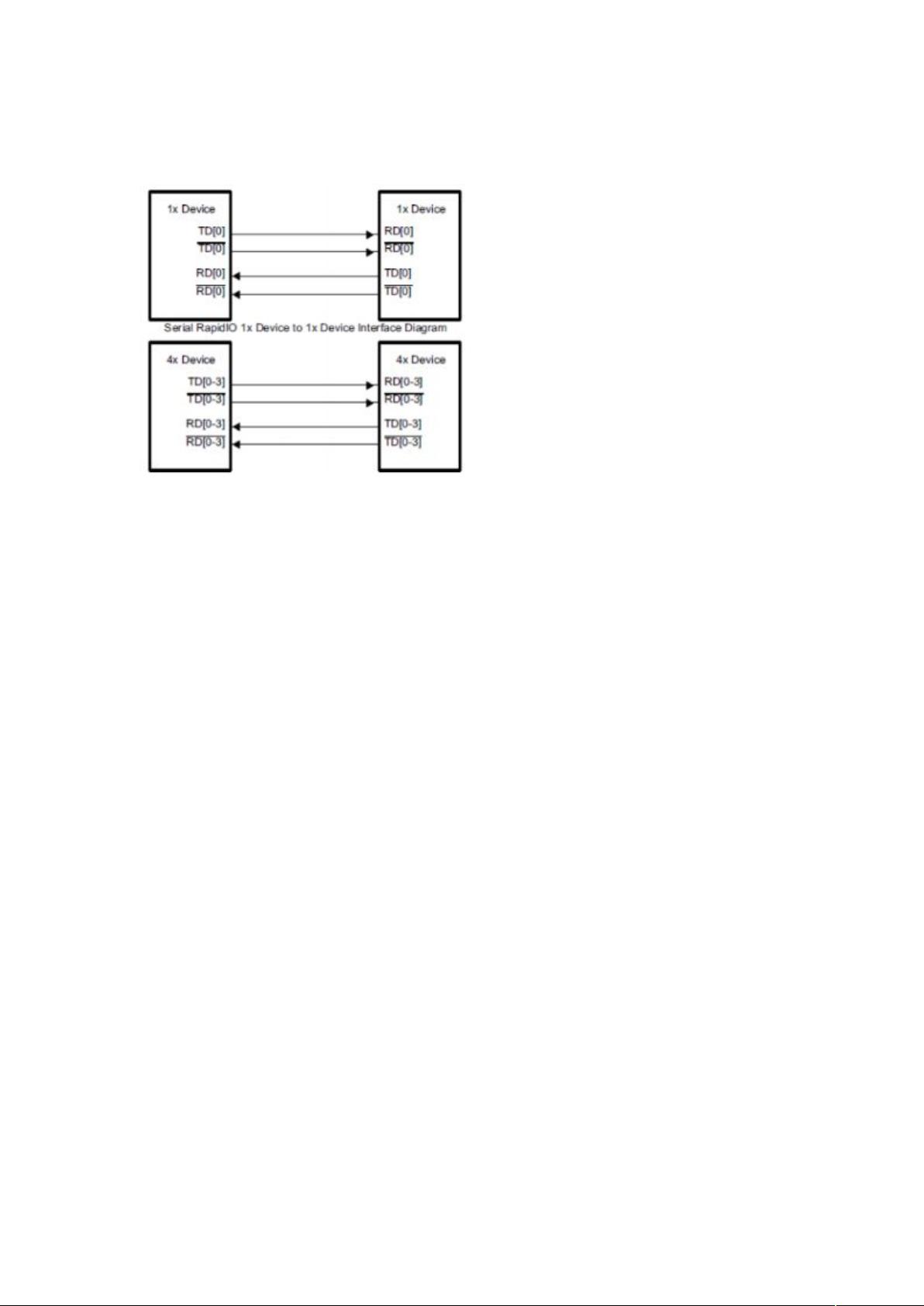

RapidIO 物理层 1x / 4x LP-Serial 规范目前涵盖四个频率点:1.25,2.5,3.125 和 5 Gbps。这定义了每

个差分对 I / O 信号的总带宽。一个 8 位/ 10 位编码方案确保时钟恢复电路有足够的数据转换。由于

8 位/ 10 位编码开销,每个差分对的有效数据带宽分别为 1.0,2.0,2.5 和 4 Gbps。串行 RapidIO 仅为

1x 和 4x 端口指定这些速率。1x 端口定义为一个 TX 和一个 RX 差分对。4x 端口是这些对中的四个的

组合。本文档描述了一个 4x RapidIO 端口,也可以配置为 4 个 1x 端口;这提供了一个可扩展的接口,

能够支持 1 到 16 Gbps 的数据带宽。

SRIO 功能支持

符合 LP-Serial 规范 REV2.1.1

•具有 4X Serial RapidIO

- 1X 端口,(4)1X 端口的可选操作

- 2X 端口,(2)2X 端口的可选操作

- 2X 端口和 1X 端口操作,(1)2X 端口和(2)1X 端口的可选操作

- 4 个端口,操作(1)4x 端口

•采用 TI SerDes 的集成时钟恢复 ?

•能够以不同的波特率运行不同的端口(仅支持整数倍速率:支持 2.5G 和 5G,不支持 3.125G 和

5G)

•硬件错误处理,包括 CRC

•支持 AC 和 DC 耦合的差分 CML 信号

•支持 1.25,2.5,3.125 和 5 Gbps 速率

•未使用端口的 Powerdown 选项

•读取,写入,写入响应,流式写入,外出的 Atomic ,维护操作 //Atomic??

•CPU 的中断生成(Doorbell 数据包和内部调度)

•支持 8b 和 16b 设备 ID

•支持接收 34b 地址

•支持生成 34b,50b 和 66b 地址

•支持数据大小:字节,半字,字,双字

•定义为 Big Endian

•直接 IO 传输

•消息传递传输

•数据有效负载为 256B

•单个消息生成最多 16 个数据包

•用于时钟域切换的弹性存储 FIFO

•符合短期运行和长期运行

•支持错误管理扩展

•支持拥塞控制扩展

•支持多播 ID

•支持短控制符号和长控制符号

•支持 IDLE1 序列,最大波特率为 5 Gbps

•基于优先级和 CRF,跨协议单元进行严格的优先级段交织

以下功能不支持

•符合全球共享内存规范(GSM)

•兼容 8/16 LP-LVDS

•RapidIO 原子操作的目标支持

Long run 和 Short run

长期规范适用于长背板应用,具有至少 50 厘米的迹线和两个或更多连接器。

短期规范专为低功耗应用而设计。它通常用于同一板上的链路或短背板连接。

两个类之间的区别是驱动程序的 Vod 。 //VOD??暂定硬件问题

Atomic operations

L2 存储器不满足

主要包括递增递减测试交换

DATA FLOW

SRIO 可以作为主机的接受端,外部设备可以突发写入 DSP,可以不必向 CPU 产生中断,不依赖与

EDMA

数据包的最大值为 256 字节,每条消息最多 16 个包,每个包产生一个请求(DMA 将数据传到

L2),但是只有消息发完才会产生中断。

SRIO 也可以作为端点设备,通过 DestID 与 DeviceID 匹配来接受包,也可以通过广播的形式

广播设置:使用 RapidIO Multicast ID 寄存器

数据流图

高速数据通过 SerDes 解码,SerDes 需要一个低频参考时钟,数据速率的 1/10 或 1/20,该时钟由

片上晶振提供

S2P 模块将数据分解服用为 10 位或 20 位字

20 位 SerDes 模块支持 5G

随后 数据进入 8b/10b 解码块,在此删除了 20%的编码,因此数据传输的速率为 80%

下一步是时钟同步和数据对齐。这些功能由 FIFO 和通道去偏移块处理。FIFO 提供弹性存储机制,

用于在恢复的时钟域和公共系统时钟之间进行切换,FIFO 深 8 字。

CRC 在此进行错误校验

在分组到达逻辑层之后,分组字段被解码并且有效载荷被缓冲。

根据接收数据包的类型,数据包路由由控制 DMA 访问的功能块处理。下图显示了这些块。

加载/存储单元(LSU)控制直接 I / O 数据包的传输,

存储器访问单元(MAU)控制直接 I / O 数据包的接收。

LSU 还控制维护包的传输。

消息包由 TXU 发送并由 RXU 接收。

这四个单元使用内部 DMA 与内部存储器通信,它们使用缓冲区和接收/发送端口与外部设备通信。

总配置时钟图

剩余24页未读,继续阅读

资源评论

kongsir2022-09-06图不清晰、基本没参考价值

kongsir2022-09-06图不清晰、基本没参考价值

不爱吃蘑菇的兔子

- 粉丝: 0

- 资源: 17

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功