XXXX 大学

《EDA 技术》课程设计

学院:信息科学与技术学院

专业:电子信息科学与技术

班级:

姓名:

学号:

指导教师:

年 月 日

一、设计内容

(利用 QuartusⅡ 软件,使用 VHDL 语言完成数字电子时钟的设计)

二、设计要求

1、具有时、分、秒的计数显示功能

2、具有清零功能,可对数字时钟的小时、分钟进行调整

3、12 小时制和 24 小时制均可

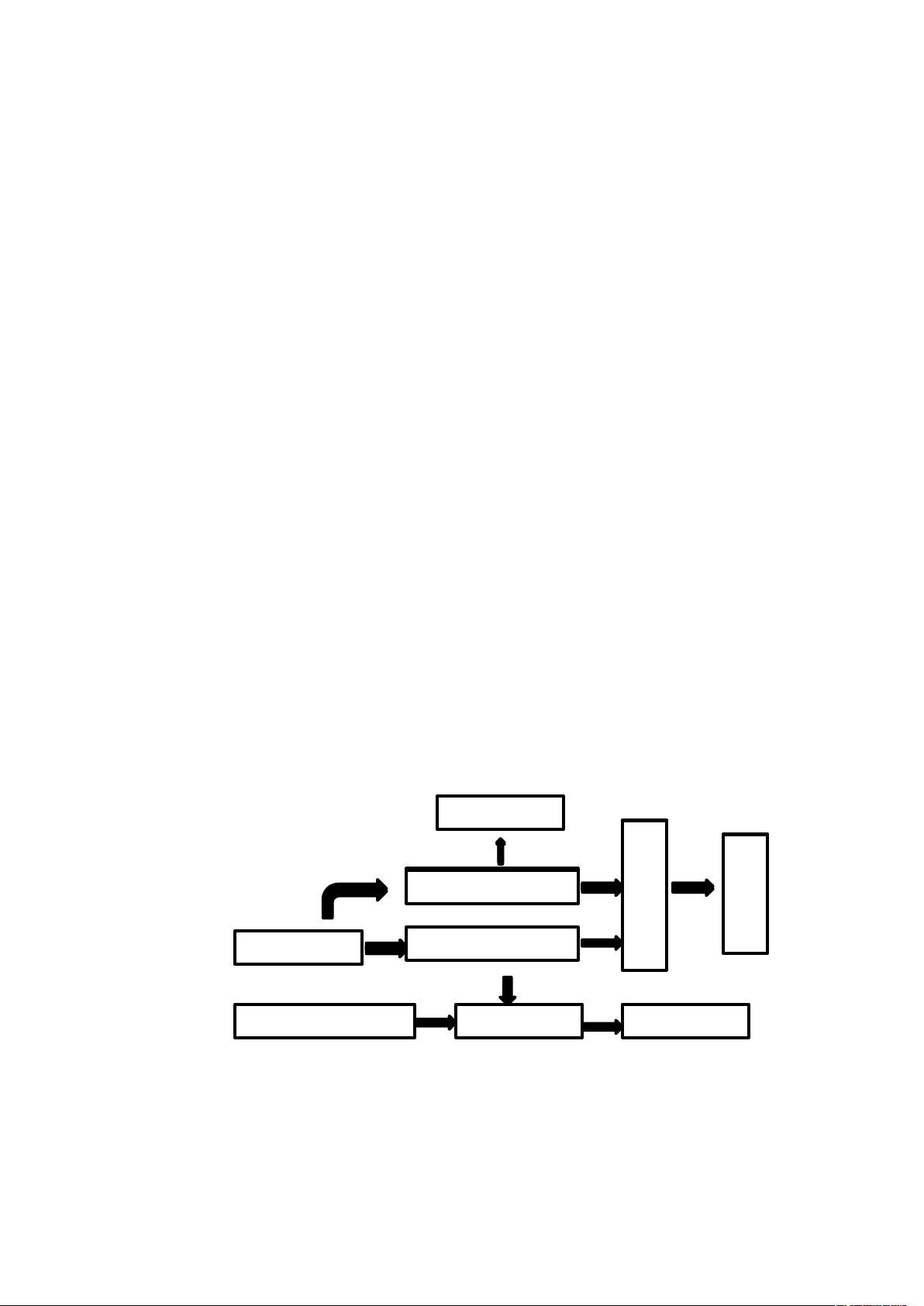

三、总体实现方案

1. 方案

(1).要实现一个数字时钟小系统,整个系统由主要模块电路模块和外部

输入输出以及显示模块组成。首先分别实现单个模块的功能,然后再通过级联

组合的方式实现对整个系统的设计。

系统框图如下:

2.基本功能介绍

(1).本数字时钟系统实现数字钟的基本功能为时间的计数显示,输入 8Hz

输

出

显

示

选

择

器

闹钟

扬声器比较器报时模块

设置时间

输

出

显

示

选

择

器

闹钟

扬声器

时钟

的时钟,通过分频产生 1Hz 的时钟信号,采用 24 小时制计时,60 进制记分、

秒,数码管显示显示 24 时、60 分、60 秒。

(2).系统还具有校正功能,可以进行小时与分钟的校时调整。

(3).整点报时功能,当计时器运行到 59 分 50 秒时,扬声器开始间断发出

响声 59 分 59 秒报时。

(4.)闹钟功能,通过手动设置时间,当系统时间与设置时间一致时,扬声

器发出声响,且需手动关闭,以达到闹钟的效果。

四、设计的详细步骤

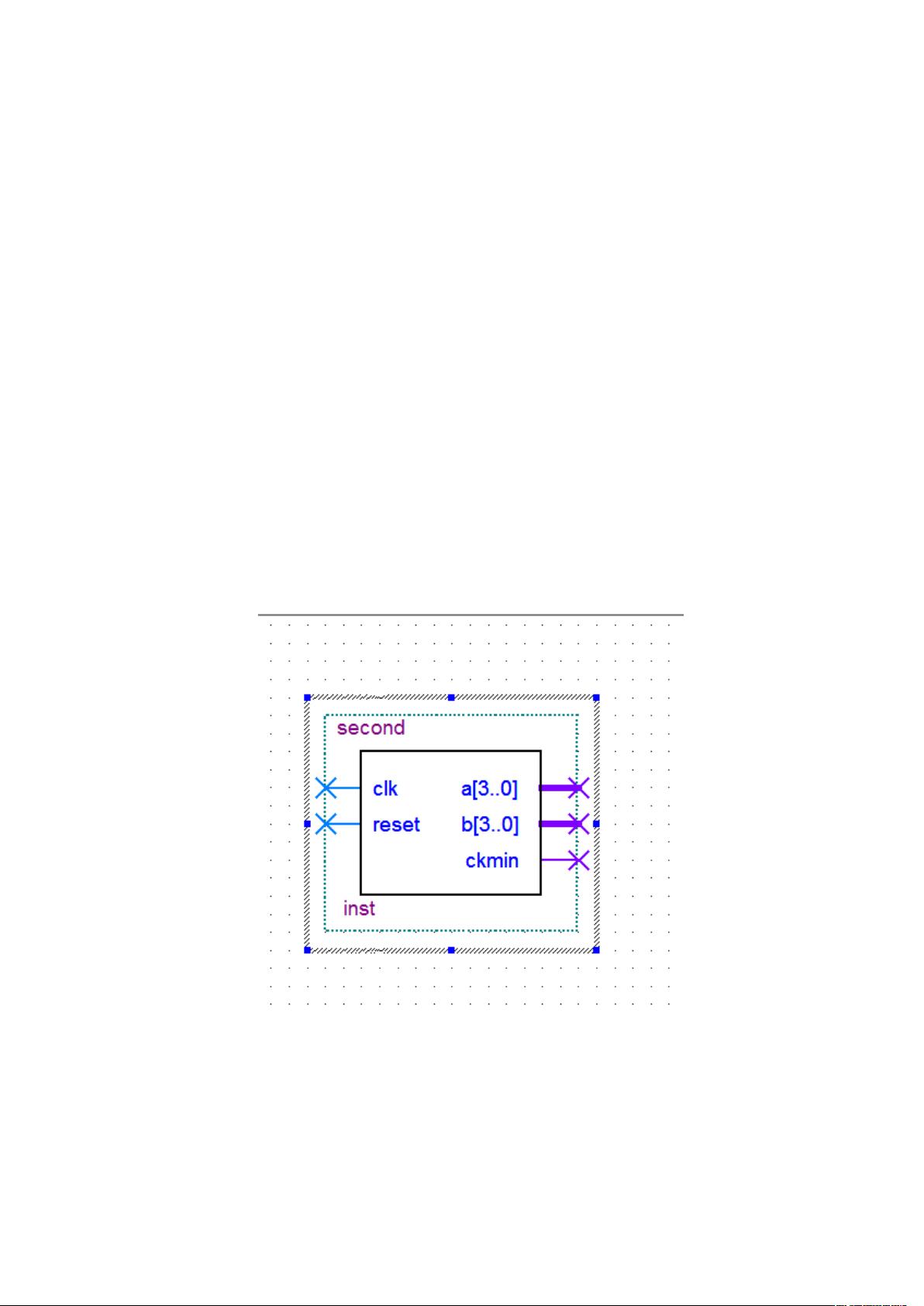

(1)秒计数模块:秒计数,在频率为 1Hz 的时钟下以 60 次为循环计数,

并产生进位信号影响分计数;

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYsecondIS

PORT(clk,reset:INSTD_LOGIC;

a:OUTSTD_LOGIC_VECTOR(3DOWNTO0);--个位数计数

b:OUTSTD_LOGIC_VECTOR(3DOWNTO0);--十位数计数

ckmin:OUTSTD_LOGIC);

ENDsecond;

ARCHITECTUREarc_secondOFsecondIS

BEGIN

PROCESS(clk,reset)

VARIABLEtma:STD_LOGIC_VECTOR(3DOWNTO0);

VARIABLEtmb:STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

IFreset='1'THEN--如果复位有效则

tma:="0000";tmb:="0000";ckmin<='0';--所有位清零

ElSIFreset='0'THEN--如果复位无效

IFclk'eventANDclk='1'THEN--如果有上升沿

IFtmb="0101"ANDtma="1001"THEN--达到 59 清零 分钟位加一

tma:="0000";tmb:="0000"; ckmin<='1';

ELSIFtma="1001"THEN--个位达到 9 十位加一

tma:="0000";tmb:=tmb+1;ckmin<='0';

ELSE

tma:=tma+1;ckmin<='0'; --各位加一

ENDIF;

ENDIF;

ENDIF;

a<=tma;--整体赋值给输出四位显示

b<=tmb;--整体赋值给输出四位显示

ENDPROCESS;

ENDarc_second;

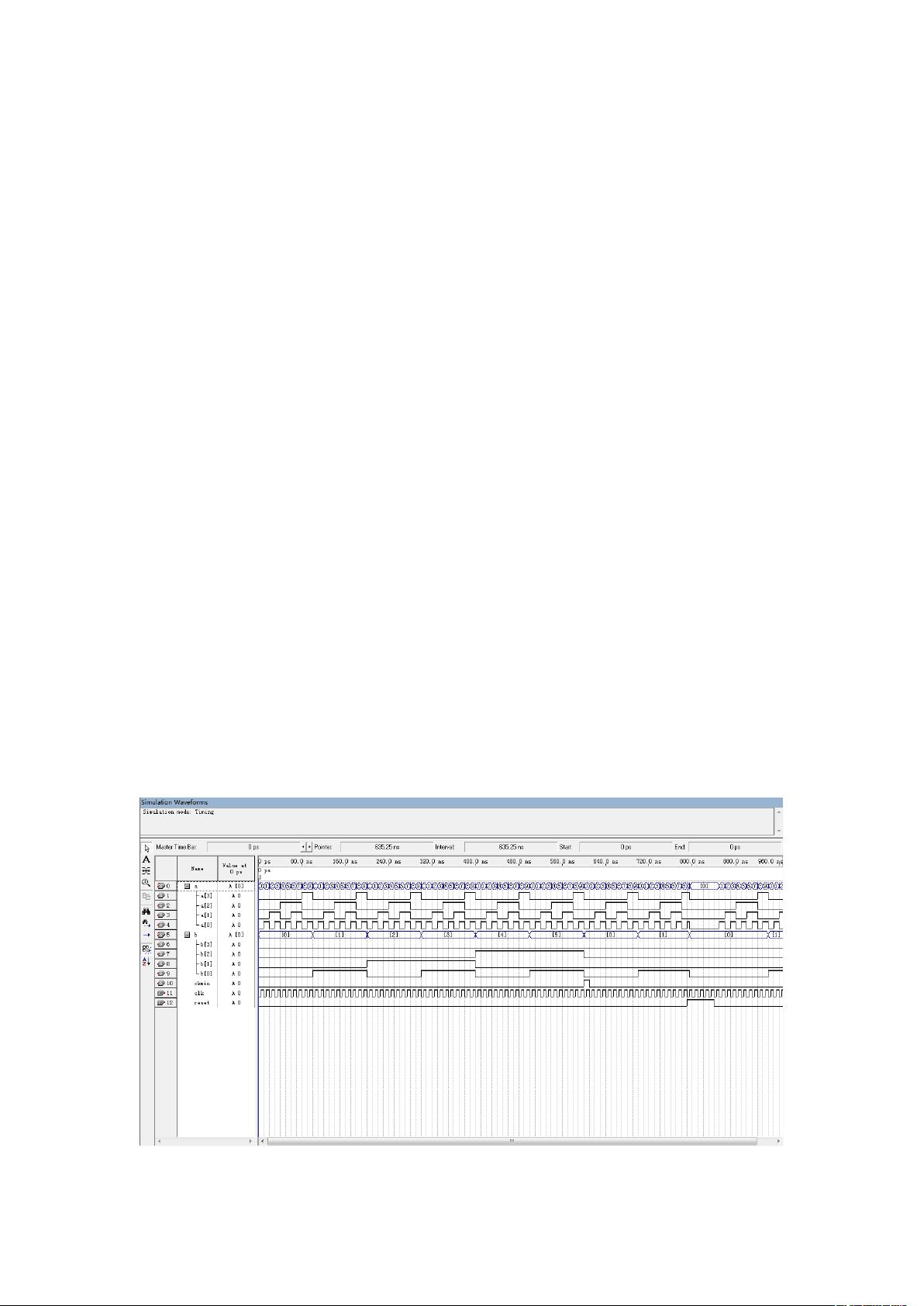

仿真图如下:

从图中可以看出,仿真结果正常,秒可以正常跳变。

如图所示与程序可得到,当秒计时模块的输入计数达到 60 时,则向分模块进

位。

(2)分计数模块:分计数,在秒进位信号为高电平时,计数一次,同样以

60 次为一个循环计数,同时产生分进位信号影响时计数;

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYminuteIS

PORT(clk,reset:INSTD_LOGIC;

a:OUTSTD_LOGIC_VECTOR(3DOWNTO0);--个位数计数

b:OUTSTD_LOGIC_VECTOR(3DOWNTO0);--十位数计数

ckhour:OUTSTD_LOGIC);

ENDminute;

ARCHITECTUREarc_minuteOFminuteIS

BEGIN