没有合适的资源?快使用搜索试试~ 我知道了~

ADF41513中文手册

资源详情

资源评论

资源推荐

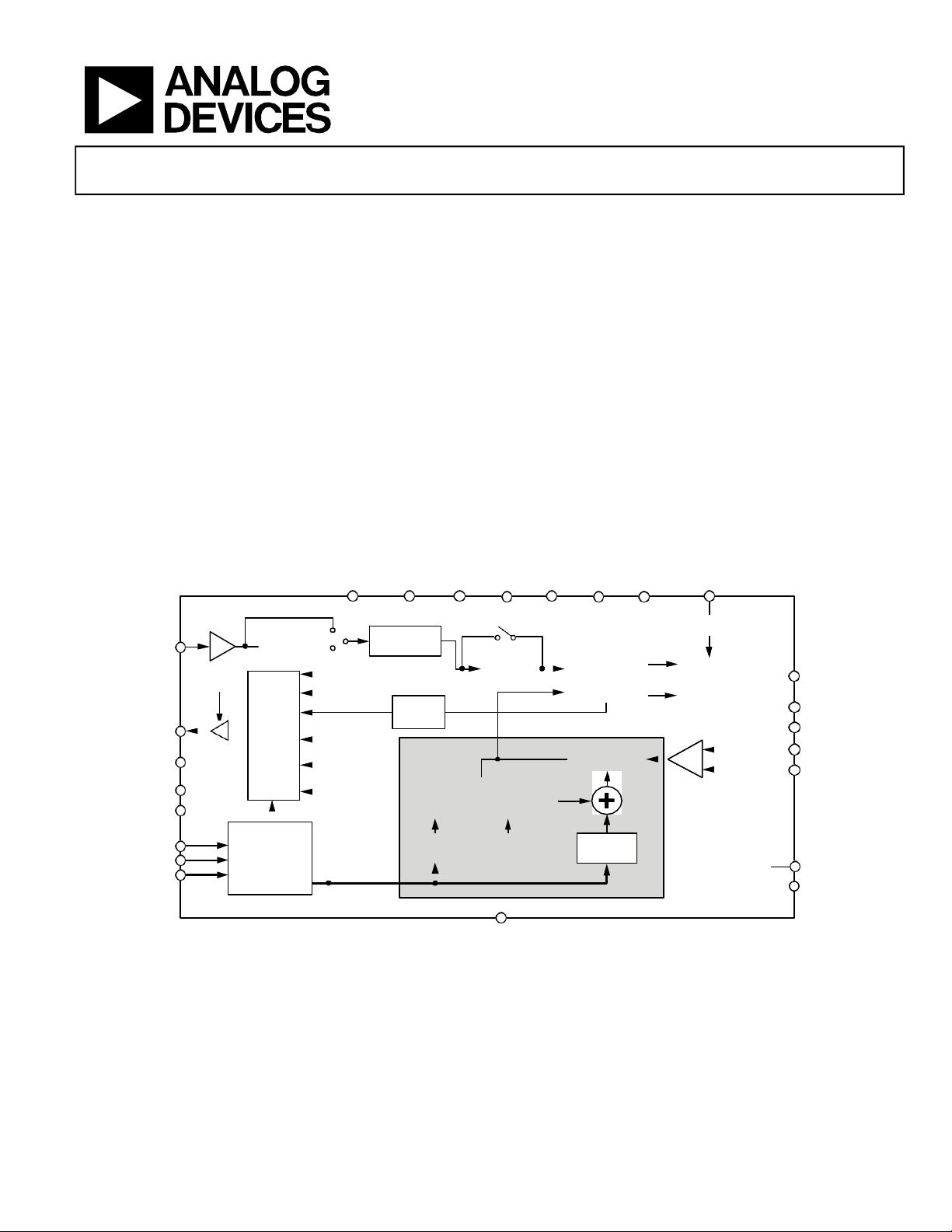

26.5 GHz, Integer N/Fractional-N,

记录表

ADF41513

5 位

r 计数器

高 Z 值

地线

输出复用器

模拟电源

参考时钟分频器

+

–

数据输出

32 位数据寄存器

整数值

1.8V 调节器

发现

锁

参考

25 位固定 /49 位可变小数插值器

充电泵

+ 相位频率

– 检测器

÷2

圆规

×2

加倍装置

模数 225 值分数值

计数器

PLL 频率合成器

特征

1 GHz 至 26.5 GHz 带宽超低噪

声 PLL

整数 N = 235 dBc/Hz,小数 N = 231 dBc/Hz 高最大 PFD

频率

整数 N = 250 MHz,小数 N = 125 MHz

25 位固定/49 位可变小数模数模式单端参考输入

3.3 V 电源、集成 1.8 V 逻辑功能的 3.3

V 电荷泵

相位再同步

可编程电荷泵电流:16 倍范围数字锁定检测

三线式串行接口,带寄存器回读选项硬件和软件掉电模

式,工作温度范围为 40°C 至+105°C

应用程序

测试设备和仪器仪表无线基础设施

微波点对点和多点无线电甚小孔径终端(VSAT)无线电航

空和国防

总体描述

ADF41513 是一款超低噪声频率合成器,可以用来实现高达

26.5 GHz,用于无线接收机和发射机的上变频和下变频部分。

ADF41513 采用高性能硅天竺葵(SiGe)、双极性互补金属氧化

物半导体(BiCMOS)工艺设计,归一化相位噪底为 235

dBc/Hz。鉴频鉴相器(PFD)的工作频率最高可达 250 MHz(整数

N 分频模式)/ 125 MHz(小数 N 分频模式),可改善相位噪声和

刺激性能。当使用 49 位分频值时,可变模数,∑-δ 调制器可以

实现极高的分辨率。ADF41513 可以用作整数 N 分频锁相环

(PLL ),也可以用作小数 N 分频锁相环(PLL ),其固定模数用于亚

赫兹频率分辨率,可变模数用于亚赫兹精确频率分辨率。

当频率合成器与外部环路滤波器和压控振荡器(VCO)一起使用时,

就实现了一个完整的 PLL。26.5 GHz 带宽无需倍频器或分频器级,

简化了系统架构,降低了成本。ADF41513 采用紧凑型 24 引脚 4 mm

× 4 mm LFCSP 封装。

功能框图

AVDD1 AVDD1 AVDD2 AVDD3 AVDD4 AVDD5

疏散时间

REFIN

大脑性麻痹

MUXOUT

数字生活设计论坛

CE

TXDATA

DC1

DC2

RFINA

RFINB

CLK

数据

报

CREG1

CREG2

地线

图一。

版本 0

文档反馈

ADI 公司提供的信息被认为是准确可靠的。然而,ADI 公司对其使用不承担任何责任,也不对因其

使用可能导致的任何专利或第三方权利的侵犯承担任何责任。规格如有变更,恕不另行通知。ADI

公司未以暗示或其他方式授予任何专利或专利权。商标和注册商标是各自所有者的财产。

美国马萨诸塞州诺伍德 9106 号邮政信箱 One Technology Way,邮编 02062-

9106,电话:781 . 329 . 4700 2019 ADI 公司。版权所有。

技术支持

www.analog.com

16805

Rev. 0 | Page

2

of

ADF4151

Data

目录

Features.........................................1

Applications.....................................1

General Description

Functional Block Diagram

Revision History

Specifications...................................3

Timing Characteristics

Absolute Maximum Ratings

Thermal Resistance

ESD Caution

Pin Configuration and Function Description

Typical Performance Characteristics

Theory of Operation

Reference Input

RF Input Stage

N Divider and R Counter

R Counter

PFD and Charge Pump

MUXOUT........................................12

Lock Detector

Readback......................................13

Input Shift Registers

Program Modes

Register Maps

Register 0 (R0) Map

Register 1 (R1) Map

Register 2 (R2) Map18

Register 3 (R3) Map18

Register 4 (R4) Map19

Register 5 (R5) Map19

Register 6 (R6) Map21

Register 7 (R7) Map23

Register 8 (R8) Map24

Register 9 (R9) Map24

Register 10 (R10) Map25

Register 11 (R11) Map25

Register 12 (R12) Map26

Register 13 (R13) Map27

Applications information28

Initialization Sequence28

RF Synthesizer: A Worked Example of 25-Bit Fixed

Modulus

Mode28..................................

RF Synthesizer: A Worked Example of Variable

Modulus

Mode28..................................

Modulus28......................................

Reference Doubler and Reference Divider28

Spur Mechanisms29

Phase Resync29

Outline Dimensions30

Ordering Guide30

修订历史

2019 年 1 月—修订版 0:初始版本

Data

ADF4151

Rev. 0 | Page

3

of

规范

AVDDx = avdd 1 = avdd 2 = avdd 3 = avdd 4 = avdd 5 = VP = 3.3V±5%,GND = 0 V,RSET = 1.8kω,dBm 折合到 50ω,TA =

TMIN(40°C)

至 TMAX(+105°C),除非另有说明。

表 1。

参数 福建话 典型 最大 单位

测试条件/注释

射频特性

8/9 预分频器

RF 输入频率(fRFIN)范围

RF 输入灵敏度 4/5

预分频器

fRFIN 范围

RF 输入灵敏度范围

һ

26.5

主频

推荐输入功率 5 dBm 至

+5 dBm,此频率范围内的工作为

限于 70°C 至 TMIN

һ

24

主频 工作在这个频率范围是 TMAX 到 TMIN

11− 功率

涉及 Figure 10 Figure 11

信息

һ

16

主频

对于较低频率,确保压摆率>

320 伏/秒

7− +5 功率

通过 1 pF 系列进行单端至 RFINA 测量

电容,1 pF 电容至 RFINB 上的 GND

输入参考频率(REFIN)特性

REFIN 输入频率电

压范围灵敏度范

围

电容电流

倍频器输入频率

10 800 兆赫

0

1.8

V

10−

8

功率

偏置 1 V(交流耦合确保 1 V 偏置),使用低功率和/或

低频率的方波

确保压摆率> 320V/s;最佳带内

相位噪声性能,确保压摆率>

500 伏/秒

10 性能因素

(Perform

ance

Factor)

150 A

225 兆赫

最大参考频率

倍频器已启用

最大 PFD 频率

整数 N 模式小数 N

模式

250

125

兆赫

兆赫

分频器范围

16 位 N 分频器范围整数

N 模式

小数 N 模式

20 511

4/5 预分频器

64 1023

8/9 预分频器

23 511

4/5 预分频器

75 1023

8/9 预分频器

电荷泵(CP)

CP 电流(ICP)吸电流和源电流高值

低值绝对精度 RSET

范围

ICP 三态泄漏

吸电流和源电流匹配 ICP 与 VCP 的

关系

ICP 与温度的关系

可编程的

7.2 妈

RSET = 1.8kω

0.45 妈

5

%

RSET = 1.8kω

1.8 2.7 10 kω

5%精度

2

钠

VCP = 0.9 V,TA = 25°C

5

%

0.7 V ≤ CP 电压(VCP)≤VP 0.7V

5

%

0.7V≤VCP≤VP 0.7V

5

%

VCP =副总统/2

ADF4151

Data

Rev. 0 | Page

4

of

参数 福建话 典型最大值 单位

测试条件/注释

逻辑输入

输入电压高(VIH)

低(VIL)

输入电流(IINH,IINL)输入

电容(CIN)

1.4

0.6

һ

10

安

一

个

pF

串行端口接口(SPI)模块可以接受 1.8 V 或 3.3 V

逻辑输入

逻辑输出

输出电压高

(VOH)

低(体积)

输出高电流,输出低电流

(IOH,IOL)

1.4

2.6

0.4

500

V

V

V

A

MUXOUT 电压= 1.8 V,DLD 电压= 1.8 V MUXOUT 电压=

3.3 V,DLD 电压= 3.3 V

电力供应

AVDD1、AVDD2、AVDD3、AVDD4、AVDD5

、VP IDD11

IDD 21

IDD 31

IDD 41

IDD 51

IP

total

省电模式

3.135 3.3 3.465

2 3.2

63.5 88

2.1 3.6

1.45 2

20 25

6 7

95.1 128.8

100

V

妈

妈

妈

妈

妈

妈

妈

妈

妈

妈

A

AVDD1 消耗的电流 AVDD2

消耗的电流 AVDD3 消耗

的电流 AVDD4 消耗的电

流 AVDD5 消耗的电流 VP

消耗的电流

AVDDx 和 VP 消耗的总电流

TA = 25°C,CE 为低电平,所有供电轨合计

噪声特性

归一化相位噪底(PNSYNTH)

在整数 N 模式 2 下

在小数 n 分频模式 3 下,归

一化 1∕f 噪声(PN1_f)3

235−

231−

128−

dBc/Hz

dBc/Hz

dBc/Hz

PLL 环路带宽(BW) = 1 MHz(整数 N 模式)

PLL 环路带宽= 1 MHz(小数 N 分频模式)10

kHz 偏移,归一化为 1 GHz

虚假信号

参考杂散 PFD 杂散

带内整数边界杂散

90−

87−

45−

dBc

dBc

dBc

参考= 100 MHz 时,PLL 环路带宽= 40 kHz,PFD

= 50 MHz 时,PLL 环路带宽= 40 kHz

10 kHz 偏移,PLL 环路带宽= 250 kHz

1 TA = 25°C,AVDDx = 3.3 V(其中 x = 1、2、3 或 4),预分频器(P) = 8/9,fRFIN = 26.5 GHz,REFIN = 124 MHz,PFD 频率输入(fPFD) = 124 MHz。

2 频率合成器的本底相位噪声通过测量 VCO 输出端的带内相位噪声并减去 20 log N(其中 N 为 N 分频器值)和 10 log fPFD 来估算。PNSYNTH 是在 VCO 输出(pn tot)10 log

fPFD 20 log n 处测得的总相位噪声。

3 PLL 相位噪声由 1/f(闪烁)噪声加上归一化 PLL 噪底组成。计算 RF 频率 fRF 和频率偏移 f 下 1/f 噪声贡献的公式为:相位噪声(PN)= P1 f+10 log(10 kHz/f)+20 log(fRF/1 GHz)。归一化相位噪底和闪烁噪声都在中建模

ADIsimPLL。

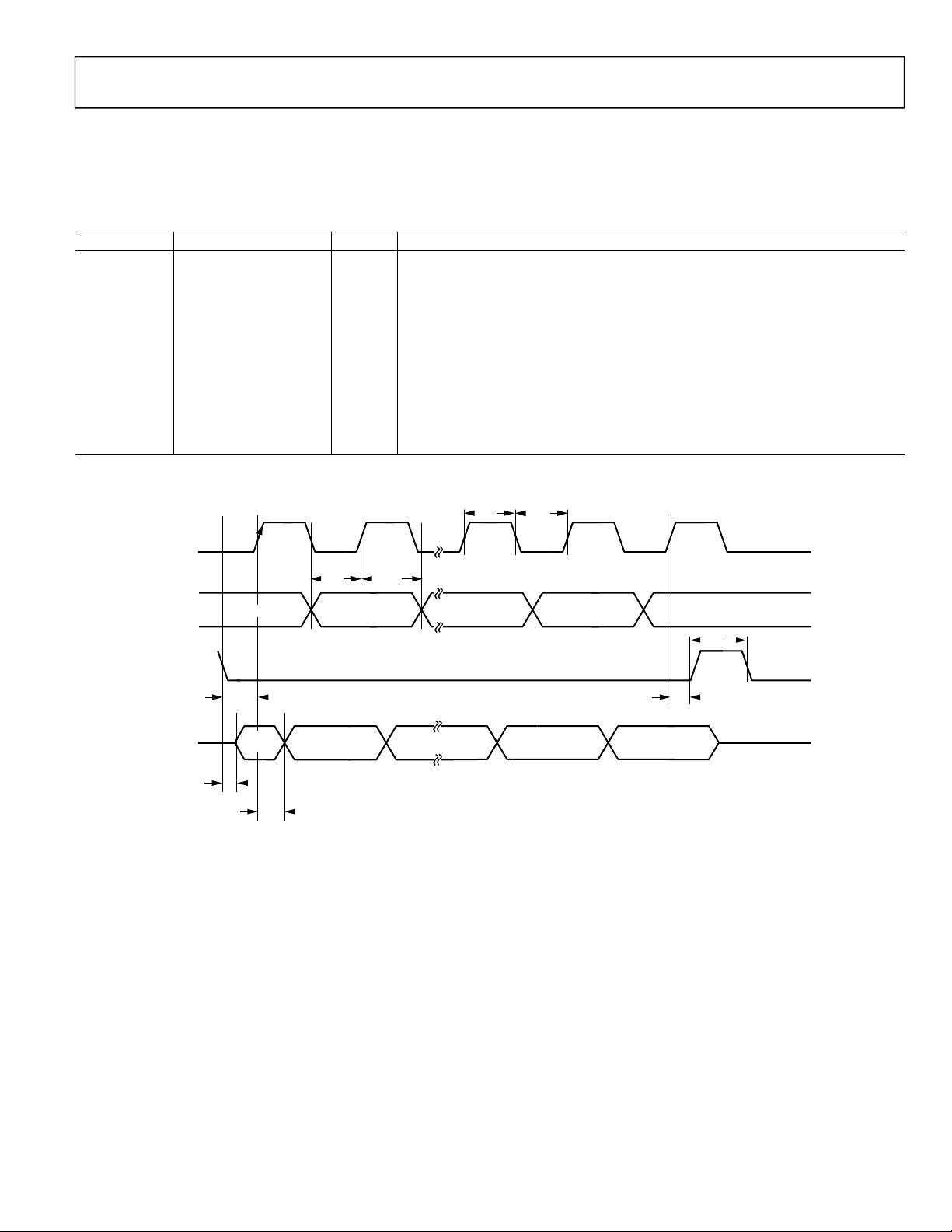

t4 t5

t2 t3

DB31( 最高有效位 )

DB30

DB2 DB1

( 控制位 C3)( 控制位 C2)

DB0 (LSB)( 控制位 C1)

t7

T1 级(一种通讯线路的名称)

t6

DB31( 最高有效位 )

DB30

DB1 DB0

t8

t9

Data

ADF4151

Rev. 0 | Page

5

of

时序特征

AVDDx = avdd 1 = avdd 2 = avdd 3 = avdd 4 = avdd 5 = VP = 3.3V±5%,GND = 0 V,RSET = 1.8kω,dBm 折合到 50ω,TA =

TMIN(40°C)

至 TMAX(+105°C),除非另有说明。

表二。读写时序

参数

限于 TMIN 至 TMAX

单位

测试条件/注释

T1 级(一种

通讯线路的名

称)

10

ns 最小值

LE 建立时间

t2

5

ns 最小值

数据到 CLK 建立时间

t3

5

ns 最小值

数据到 CLK 保持时间

t4

12.5

ns 最小值 CLK 高压持续时间

t5

12.5

ns 最小值 CLK 低持续时间

t6

5

ns 最小值

CLK 到乐设置时间

t7

10

ns 最小值 脉冲宽度

t8

20

ns 最大值 当 MUXOUT 配置为 SPI 输出时,MUXOUT 建立时间缩短

t9

20

ns 最大值 MUXOUT 配置为 SPI 输出时 MUXOUT 的 CLK 建立时间

时间图

时钟信号

数据

引线标注

MUXOUT

图二。读写时序

16805

剩余32页未读,继续阅读

莫语莫与

- 粉丝: 0

- 资源: 2

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0