没有合适的资源?快使用搜索试试~ 我知道了~

Features • Low-voltage and Standard-voltage Operation – 1.8 (V CC = 1.8V to 3.6V) • Internally Organized 65,536 x 8 • Two-wire Serial Interface • Schmitt Triggers, Filtered Inputs for Noise Suppression • Bidirectional Data Transfer Protocol • 1 MHz (3.6V), 400 kHz (1.8V) Compatibility • Write Protect Pin for Hardware and Software Data Protection • 128-byte Page Write Mode (Partial Page Writes Allowed) • Self-timed Write Cycle (5 ms Max) • High Reliability – Endurance: 1,000,000 Write Cycles – Data Retention: 40 Years • Lead-free/Halogen-free Devices Available • 8-lead PDIP, 8-lead JEDEC SOIC, 8-lead TSSOP, 8-lead LAP and 8-lead SAP Packages • Die Sales: Wafer Form, Waffle Pack and Bumped Die

资源推荐

资源详情

资源评论

1

Features

• Low-voltage and Standard-voltage Operation

– 1.8 (V

CC

= 1.8V to 3.6V)

• Internally Organized 65,536 x 8

• Two-wire Serial Interface

• Schmitt Triggers, Filtered Inputs for Noise Suppression

• Bidirectional Data Transfer Protocol

• 1 MHz (3.6V), 400 kHz (1.8V) Compatibility

• Write Protect Pin for Hardware and Software Data Protection

• 128-byte Page Write Mode (Partial Page Writes Allowed)

• Self-timed Write Cycle (5 ms Max)

• High Reliability

– Endurance: 1,000,000 Write Cycles

– Data Retention: 40 Years

• Lead-free/Halogen-free Devices Available

• 8-lead PDIP, 8-lead JEDEC SOIC, 8-lead TSSOP,

8-lead LAP and 8-lead SAP Packages

• Die Sales: Wafer Form, Waffle Pack and Bumped Die

Description

The AT24C512B provides 524,288 bits of serial electrically erasable and programma-

ble read only memory (EEPROM) organized as 65,536 words of 8 bits each. The

device’s cascadable feature allows up to four devices to share a common two-wire

bus. The device is optimized for use in many industrial and commercial applications

where low-power and low-voltage operation are essential. The devices are available in

space-saving 8-pin PDIP, 8-lead JEDEC SOIC, 8-lead TSSOP, 8-lead Leadless Array

(LAP), and 8-lead SAP packages. In addition, the entire family is available in a 1.8V

(1.8V to 3.6V) version.

Table 1. Pin Configurations

Pin Name Function

A0–A2 Address Inputs

SDA Serial Data

SCL Serial Clock Input

WP Write Protect

NC No Connect

Rev. 5112A–SEEPR–8/05

Two-wire Serial

EEPROM

512K (65,536 x 8)

AT24C512B

with Three Device

Address Inputs

Preliminary

8-lead PDIP

1

2

3

4

8

7

6

5

A0

A1

A2

GND

VCC

WP

SCL

SDA

8-lead Leadless Array

Bottom View

1

2

3

4

8

7

6

5

VCC

WP

SCL

SDA

A0

A1

A2

GND

8-lead TSSOP

1

2

3

4

8

7

6

5

A0

A1

A2

GND

VCC

WP

SCL

SDA

8-lead SAP

Bottom View

1

2

3

4

8

7

6

5

VCC

WP

SCL

SDA

A0

A1

A2

GND

8-lead SOIC

1

2

3

4

8

7

6

5

A0

A1

A2

GND

VCC

WP

SCL

SDA

2

AT24C512B [Preliminary]

5112A–SEEPR–8/05

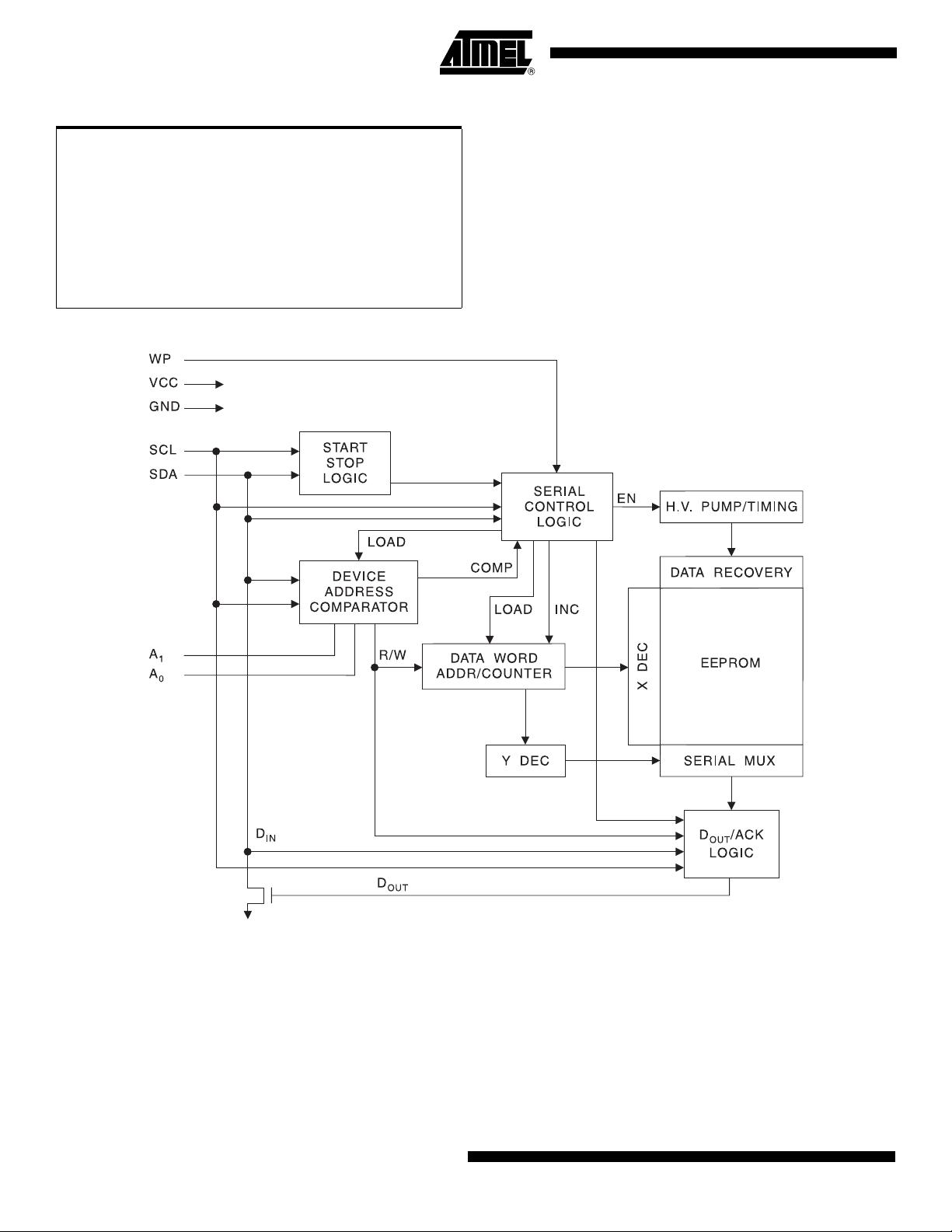

Figure 1. Block Diagram

Absolute Maximum Ratings*

Operating Temperature..................................–55°C to +125°C

*NOTICE: Stresses beyond those listed under “Absolute

Maximum Ratings” may cause permanent dam-

age to the device. This is a stress rating only and

functional operation of the device at these or any

other conditions beyond those indicated in the

operational sections of this specification is not

implied. Exposure to absolute maximum rating

conditions for extended periods may affect device

reliability.

Storage Temperature .....................................–65°C to +150°C

Voltage on Any Pin

with Respect to Ground .................................... –1.0V to +7.0V

Maximum Operating Voltage ............................................ 4.3V

DC Output Current........................................................ 3.0 mA

3

AT24C512B [Preliminary]

5112A–SEEPR–8/05

Pin Description SERIAL CLOCK (SCL): The SCL input is used to positive edge clock data into each

EEPROM device and negative edge clock data out of each device.

SERIAL DATA (SDA): The SDA pin is bidirectional for serial data transfer. This pin is

open-drain driven and may be wire-ORed with any number of other open-drain or open

collector devices.

DEVICE/PAGE ADDRESSES (A2, A1, A0): The A2, A1, and A0 pins are device

address inputs that are hardwired (directly to GND or to Vcc) for compatibility with other

AT24Cxx devices. When the pins are hardwired, as many as eight 512K devices may be

addressed on a single bus system. (Device addressing is discussed in detail under

“Device Addressing,” page 8.) A device is selected when a corresponding hardware and

software match is true. If these pins are left floating, the A2, A1, and A0 pins will be

internally pulled down to GND. However, due to capacitive coupling that may appear

during customer applications, Atmel recommends always connecting the address pins

to a known state. When using a pull-up resistor, Atmel recommends using 10kΩ or less.

WRITE PROTECT (WP): The write protect input, when connected to GND, allows nor-

mal write operations. When WP is connected directly to Vcc, all write operations to the

memory are inhibited. If the pin is left floating, the WP pin will be internally pulled down

to GND. However, due to capacitive coupling that may appear during customer applica-

tions, Atmel recommends always connecting the WP pins to a known state. When using

a pull-up resistor, Atmel recommends using 10kΩ or less.

Memory Organization AT24C512B, 512K SERIAL EEPROM: The 512K is internally organized as 512 pages

of 128-bytes each. Random word addressing requires a 16-bit data word address.

剩余17页未读,继续阅读

资源评论

MCU-X

- 粉丝: 3

- 资源: 49

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功