交通控制器VerilogHDL_3

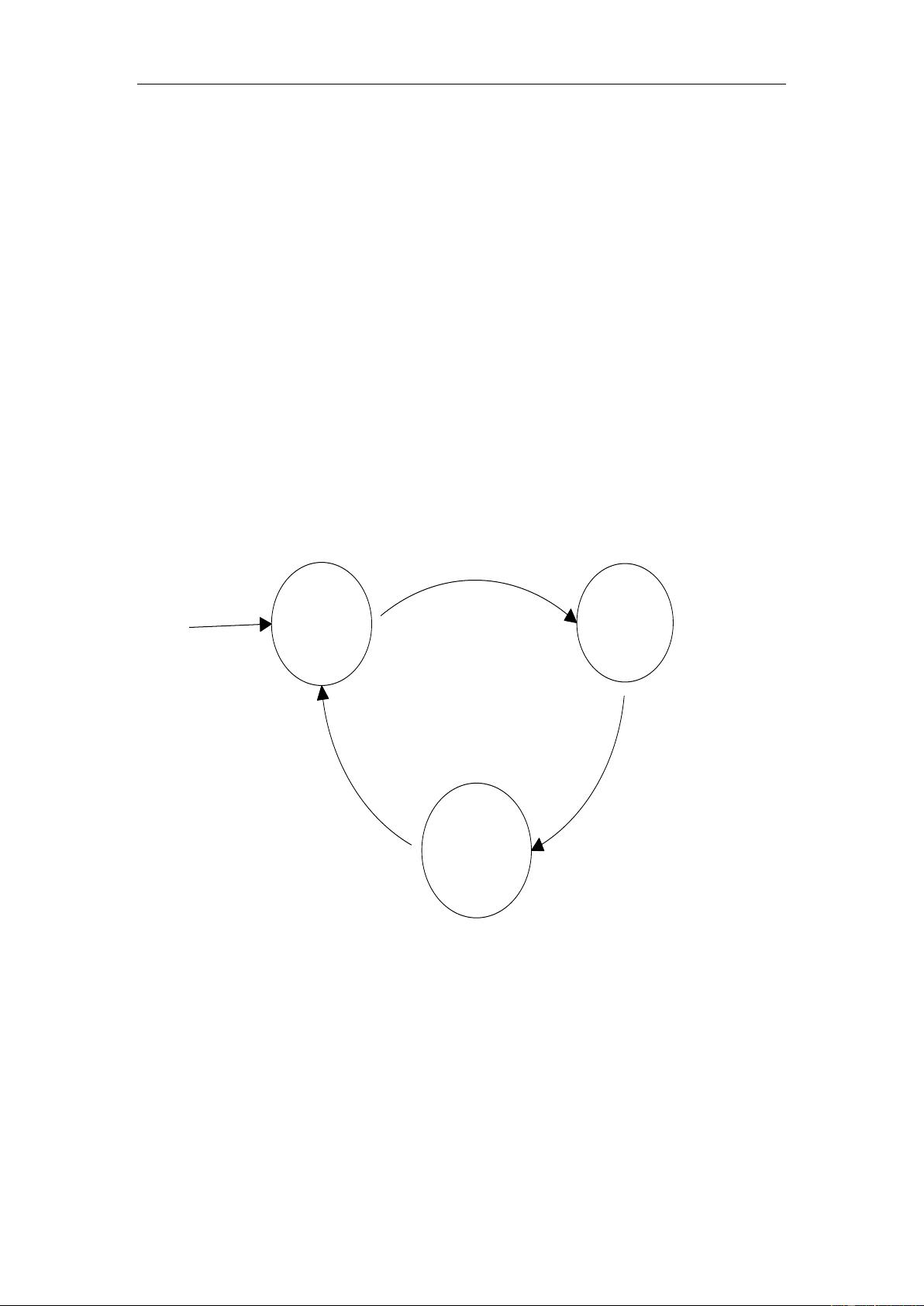

### 基于Verilog HDL的交通灯控制系统设计与实现 #### 实验背景与目的 交通信号灯作为城市交通管理的重要组成部分,在保障交通安全、提高通行效率方面发挥着至关重要的作用。随着电子技术的发展,利用硬件描述语言(Hardware Description Language, HDL)如Verilog HDL来设计和实现交通信号控制系统已经成为一种趋势。本实验旨在通过Verilog HDL设计一款简单的交通信号灯控制系统,以模拟实际道路中的交通灯控制逻辑,并深入理解Verilog HDL在数字电路设计中的应用。 #### 实验要求与系统设计 根据实验报告要求,需要设计并实现一个基于Verilog HDL的交通灯控制系统,该系统能够控制东西走向和南北走向的交通灯的状态转换。为简化起见,本次实验仅考虑单向交通灯的状态变化,包括红灯(RED)、绿灯(GREEN)和黄灯(YELLOW)三种状态。设计中需要关注以下关键点: 1. **状态迁移**:明确不同交通灯状态之间的转换顺序及条件。 2. **时间延迟**:实现不同状态下的时间计数,确保交通灯按照预设的时间间隔进行切换。 #### 设计实现 ##### 系统结构与模块划分 - **状态机模块**:采用有限状态机(Finite State Machine, FSM)的方式实现交通灯状态的自动转换。 - **计时器模块**:用于控制每种交通灯状态的持续时间。 - **外部接口**:定义系统与外界交互的输入/输出端口。 ##### 源码解析 ```verilog module jiaotongdeng(rst, clk, red_light, green_light, yellow_light); input clk, rst; output reg red_light, green_light, yellow_light; reg [1:0] currentstate, nextstate; reg [5:0] red_counter, green_counter; reg [3:0] yellow_counter; // 定义状态参数 parameter RED_S = 3'b000; parameter GREEN_S = 3'b001; parameter YELLOW_S = 3'b010; // 状态初始化 always @(posedge clk or posedge rst) if (rst) currentstate <= RED_S; else currentstate <= nextstate; // 状态转换逻辑 always @(rst or currentstate or green_counter or red_counter or yellow_counter) if (rst) nextstate = RED_S; else case (currentstate) RED_S: if (red_counter == 59) nextstate = GREEN_S; else nextstate = RED_S; GREEN_S: if (green_counter == 54) nextstate = YELLOW_S; else nextstate = GREEN_S; YELLOW_S: if (yellow_counter == 4) nextstate = RED_S; else nextstate = YELLOW_S; default: nextstate = RED_S; endcase // 计时器逻辑 always @(posedge clk or posedge rst) if (rst) red_counter <= 6'b0; else if (currentstate == RED_S) red_counter <= red_counter + 6'b1; else red_counter <= 6'b0; always @(posedge clk or posedge rst) if (rst) green_counter <= 6'b0; else if (currentstate == GREEN_S) green_counter <= green_counter + 6'b1; else green_counter <= 6'b0; always @(posedge clk or posedge rst) if (rst) yellow_counter <= 4'b0; else if (currentstate == YELLOW_S) yellow_counter <= yellow_counter + 4'b1; else yellow_counter <= 4'b0; // 灯光控制逻辑 always @(currentstate) if (currentstate == RED_S) red_light = 1'b1; else red_light = 1'b0; always @(currentstate) if (currentstate == GREEN_S) green_light = 1'b1; else green_light = 1'b0; always @(currentstate) if (currentstate == YELLOW_S) yellow_light = 1'b1; else yellow_light = 1'b0; endmodule ``` #### 测试代码与验证 为了验证所设计的交通灯控制系统是否符合预期,可以通过编写测试代码来模拟系统运行环境。测试代码通常会包括对系统输入信号的控制(如复位信号`rst`和时钟信号`clk`),以及对输出信号(交通灯状态)的监测。 ```verilog module jiaotongdeng_testbench; reg clk, rst; wire red_light, green_light, yellow_light; // 实例化交通灯模块 jiaotongdeng uut ( .clk(clk), .rst(rst), .red_light(red_light), .green_light(green_light), .yellow_light(yellow_light) ); initial begin clk = 0; rst = 1; #10; rst = 0; #200; $finish; end always #5 clk = ~clk; endmodule ``` #### 结论 本实验通过使用Verilog HDL成功设计了一个简单的交通灯控制系统。通过对系统架构的设计、源代码的编写及测试验证,不仅加深了对Verilog HDL语言的理解,还学习了如何运用有限状态机实现复杂的逻辑控制功能。此外,该实验还为今后进一步研究和开发更复杂的交通控制系统提供了基础。

- 粉丝: 1

- 资源: 62

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- NSKeyValueObservationException如何解决.md

- 基于Java的环境保护与宣传网站论文.doc

- 前端开发中的JS快速排序算法原理及实现方法

- 常见排序算法概述及其性能比较

- 形状分类31-YOLO(v5至v11)、COCO、CreateML、Darknet、Paligemma、VOC数据集合集.rar

- 2018年最新 ECshop母婴用品商城新版系统(微商城+微分销+微信支付)

- BookShopTuto.zip

- 论文复现:结合 CNN 和 LSTM 的滚动轴承剩余使用寿命预测方法

- MySQL中的数据库管理语句-ALTER USER.pdf

- 冒泡排序算法解析及优化.md

- 2024年智算云市场发展与生态分析报告

- qwewq23132131231

- 《木兰诗》教学设计.docx

- 《台阶》教学设计.docx

- 《卖油翁》文言文教学方案.docx

- 《老王》教学设计方案.docx

信息提交成功

信息提交成功