Preliminary Information

101 Innovation Drive

San Jose, CA 95134

www.altera.com

Quartus II Version 7.2 Handbook

Volume 1: Design and Synthesis

QII5V1-7.2

Copyright © 2007 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device des-

ignations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and

service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Al-

tera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants

performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make

changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the ap-

plication or use of any information, product, or service described herein except as expressly agreed to in writing by Altera

Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published in-

formation and before placing orders for products or services.

ii Altera Corporation

Preliminary

Altera Corporation iii

Preliminary

Contents

Chapter Revision Dates .......................................................................... xv

About this Handbook ............................................................................ xvii

How to Contact Altera ......................................................................................................................... xvii

Third-Party Software Product Information ...................................................................................... xvii

Typographic Conventions .................................................................................................................. xviii

Section I. Design Flows

Chapter 1. Design Planning with the Quartus II Software

Introduction ............................................................................................................................................ 1–1

Device and Programming/

Configuration Method Selection ......................................................................................................... 1–2

Device Selection ................................................................................................................................ 1–2

Device Migration Planning ............................................................................................................. 1–3

Programming/Configuration Method Selection ......................................................................... 1–4

Early Planning Tools for Power and I/O ........................................................................................... 1–5

Early Power Estimation ................................................................................................................... 1–5

Early Pin Planning and I/O Analysis ........................................................................................... 1–6

Selecting Third-Party EDA Tool Flows ................................................................................................1–9

Synthesis Tools ................................................................................................................................. 1–9

Simulation Tools ............................................................................................................................. 1–10

Formal Verification Tools .............................................................................................................. 1–10

Planning for On-Chip Debugging Options ...................................................................................... 1–11

Planning for an Incremental Compilation Flow ............................................................................. 1–13

Flat Compilation Flow with No Design Partitions .................................................................... 1–13

Incremental Compilation with Design Partitions ...................................................................... 1–14

Top-Down Versus Bottom-Up Incremental Flows .................................................................... 1–15

Planning Design Partitions ........................................................................................................... 1–17

Creating a Design Floorplan ......................................................................................................... 1–18

Early Timing Estimation ..................................................................................................................... 1–19

Conclusion ............................................................................................................................................ 1–20

Referenced Documents ....................................................................................................................... 1–20

Document Revision History ............................................................................................................... 1–21

Chapter 2. Quartus II Incremental Compilation for Hierarchical and Team-Based Design

Introduction ............................................................................................................................................ 2–1

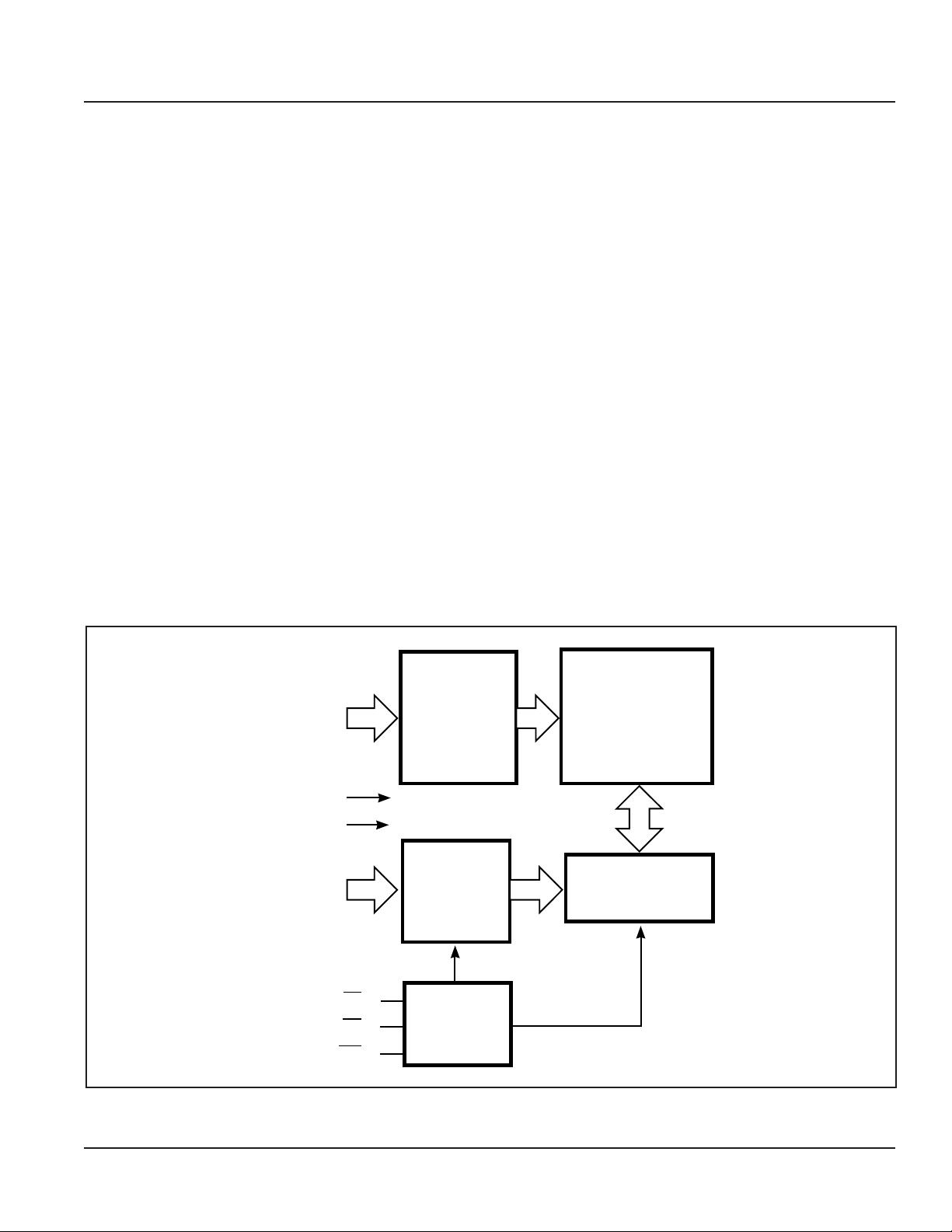

Choosing a Quartus II Compilation Flow .......................................................................................... 2–3

iv Altera Corporation

Preliminary

Quartus II Handbook, Volume 1

Flat Compilation Flow with No Design Partitions ...................................................................... 2–3

Incremental Compilation Flow with Design Partitions .............................................................. 2–5

Top-Down versus Bottom-Up Compilation Flows ..................................................................... 2–9

Quick Start Guide – Summary of Steps for an Incremental Compilation Flow ......................... 2–11

Top-Down Incremental Compilation Flow ................................................................................ 2–11

Bottom-Up Incremental Compilation .......................................................................................... 2–13

Design Partitions .................................................................................................................................. 2–17

Design Partition Assignments Compared to Physical Placement Assignments .................. 2–18

Creating Design Partitions ................................................................................................................. 2–19

Partition Name ................................................................................................................................ 2–21

Setting the Netlist Type for Design Partitions ................................................................................. 2–22

Fitter Preservation Level ............................................................................................................... 2–24

Empty Partitions ............................................................................................................................. 2–26

What Represents a Source Change for Incremental Compilation? ......................................... 2–27

Creating a Design Floorplan With LogicLock Location Assignments ......................................... 2–29

Taking Advantage of the Early Timing Estimator .................................................................... 2–31

Exporting and Importing Partitions for Bottom-Up Design Flows .............................................. 2–32

Quartus II Exported Partition File (.qxp) .................................................................................... 2–32

Exporting a Lower-Level Partition to be Used in a Top-Level Project ................................... 2–33

Exporting a Lower-Level Block within a Project ....................................................................... 2–35

Importing a Lower-Level Partition Into the Top-Level Project ............................................... 2–36

Importing Assignments and Advanced Import Settings ......................................................... 2–37

Generating Bottom-Up Design Partition Scripts for Project Management ............................ 2–40

Guidelines for Creating Good Design Partitions and LogicLock Regions .................................. 2–46

Creating Good Design Partitions .................................................................................................2–47

Partition Statistics Reports ............................................................................................................ 2–50

Resource Balancing ........................................................................................................................ 2–51

Timing Budgeting .......................................................................................................................... 2–53

Methodology to Check Partition Quality during Partition Planning ..................................... 2–54

The Importance of Floorplan Location Assignments in Incremental Compilation .............. 2–55

Creating Good Floorplan Location Assignments ...................................................................... 2–57

Incremental Compilation Advisor ............................................................................................... 2–60

Criteria for Successful Partition and Floorplan Schemes ......................................................... 2–61

Recommended Design Flows and Compilation Application Examples ..................................... 2–62

Top-Down Incremental Design Flows ........................................................................................ 2–62

Bottom-Up Incremental Design Flows ........................................................................................ 2–67

Incremental Compilation Restrictions .............................................................................................. 2–76

Using Incremental Synthesis Only Instead of Full Incremental Compilation ...................... 2–76

Preserving Exact Timing Performance ........................................................................................ 2–77

Using Incremental Compilation with Quartus II Archive Files .............................................. 2–77

Formal Verification Support ......................................................................................................... 2–78

OpenCore Plus MegaCore Functions in Bottom-Up Flows ..................................................... 2–78

Importing Encrypted IP Cores in Bottom-Up Flows ................................................................ 2–78

SignalProbe Pins and Engineering Change Management with the Chip Planner ............... 2–78

SignalTap II Embedded Logic Analyzer in Bottom-Up Compilation Flows ......................... 2–80

Logic Analyzer Interface in Bottom-Up Compilation Flows ................................................... 2–81

Migrating Projects with Design Partitions to Different Devices ............................................. 2–81

Altera Corporation v

Preliminary

Contents

HardCopy Compilation Flows ..................................................................................................... 2–82

Assignments Made in HDL Source Code in Bottom-Up Flows .............................................. 2–83

Compilation Time with Physical Synthesis Optimizations ..................................................... 2–83

Restrictions on Megafunction Partitions ..................................................................................... 2–84

Routing Preservation in Bottom-Up Compilation Flows ......................................................... 2–84

Bottom-Up Design Partition Script Limitations ......................................................................... 2–84

Register Packing and Partition Boundaries ................................................................................ 2–87

I/O Register Packing ..................................................................................................................... 2–87

Scripting Support ................................................................................................................................. 2–99

Generate Incremental Compilation Tcl Script Command ........................................................ 2–99

Preparing a Design for Incremental Compilation ................................................................... 2–100

Creating Design Partitions .......................................................................................................... 2–100

Setting Properties of Design Partitions ..................................................................................... 2–101

Creating Good Floorplan Location Assignments—Excluding or Filtering Certain Device

Elements (Such as RAM or DSP Blocks) ................................................................................... 2–102

Generating Bottom-Up Design Partition Scripts ..................................................................... 2–103

Exporting a Partition to be Used in a Top-Level Project ........................................................ 2–105

Importing a Lower-Level Partition into the Top-Level Project ............................................. 2–106

Makefiles ........................................................................................................................................ 2–106

Recommended Design Flows and Compilation Application Examples .............................. 2–107

Conclusion .......................................................................................................................................... 2–109

Referenced Documents ..................................................................................................................... 2–109

Document Revision History ............................................................................................................. 2–111

Chapter 3. Quartus II Design Flow for MAX+PLUS II Users

Introduction ............................................................................................................................................ 3–1

Chapter Overview ................................................................................................................................. 3–1

Typical Design Flow .............................................................................................................................. 3–2

Device Support ....................................................................................................................................... 3–3

Quartus II GUI Overview ..................................................................................................................... 3–4

Project Navigator .............................................................................................................................. 3–4

Node Finder ...................................................................................................................................... 3–4

Tcl Console ........................................................................................................................................ 3–4

Messages ............................................................................................................................................ 3–4

Status .................................................................................................................................................. 3–5

Setting Up MAX+PLUS II Look and Feel in Quartus II.....................................................................3–6

MAX+PLUS II Look and Feel ................................................................................................................3–7

Compiler Tool ..........................................................................................................................................3–9

Analysis and Synthesis .................................................................................................................. 3–10

Partition Merge ............................................................................................................................... 3–10

Fitter ................................................................................................................................................. 3–10

Assembler ........................................................................................................................................ 3–11

Timing Analyzer ............................................................................................................................. 3–11

EDA Netlist Writer ......................................................................................................................... 3–11

Design Assistant ............................................................................................................................. 3–11

MAX+PLUS II Design Conversion .....................................................................................................3–12

Converting an Existing MAX+PLUS II Design .......................................................................... 3–12