没有合适的资源?快使用搜索试试~ 我知道了~

时序分析快速入门,讲的很好,很细致,希望能够帮助到学习时序分析的初学者

资源推荐

资源详情

资源评论

1. 在 Quartus 中对设计进行时序分析

2.1 TimeQuest 工具

Quartus® II TimeQuest Timing Analyzer 是一个功能强大的 ASIC 型时序分析工具,能够以工业标准方法

论来约束,分析和报告用户设计中所有逻辑的时序性能。这个工具是一个严格的静态工具,使用时不

需要搭建硬件环境及进行调试。本节将介绍如何使用 Quartus II TimeQuest Timing Analyzer 工具的图形化

功能来约束,分析及报告设计中的时序结果。

使用这个工具,我们要指定初始时序信息,包括时钟,时序例外以及信号传输中的到达和要求的时

间。我们通过后缀名为 sdc(Synopsys Design Constraints)的文件来指定时序要求,然后 The Quartus II

Fier 将优化逻辑布局等来满足我们的时序要求。

在时序分析过程中,Quartus II TimeQuest Timing Analyzer 分析设计中的每一条时序路径,计算每条

路径的延迟,检查是否存在时序违例,并且报告时序结果。一旦发现时序违例,可以精确定位到违例

路径的时序细节,然后用户约束它以纠正违例。如果时序分析没有报告违例,那么恭喜你,在这个器

件中的逻辑行为将与你的设计意图一致。

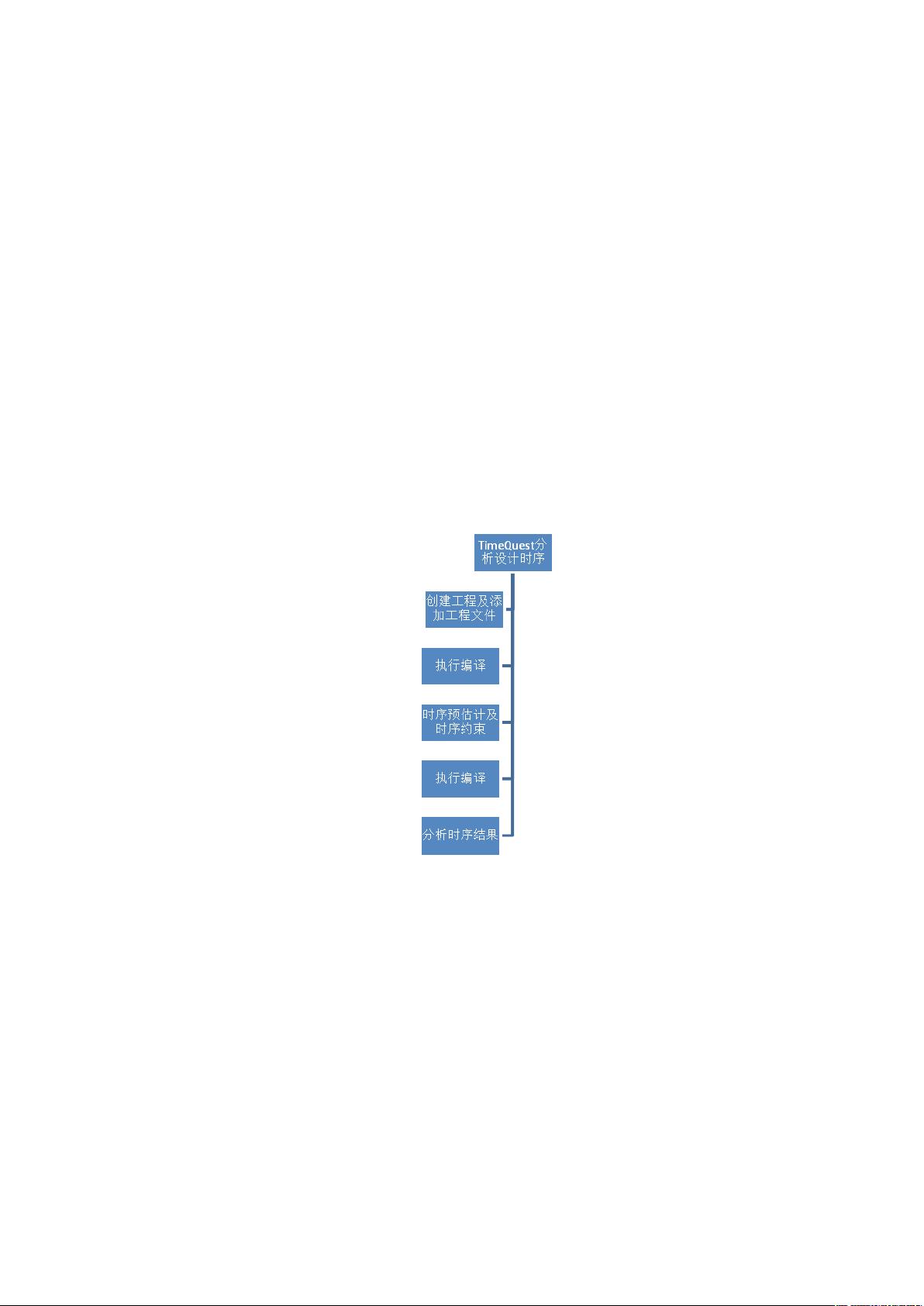

使用 TimeQuest 分析设计时序的一般步骤为:

图 使用 TimeQuest 分析设计时序的一般步骤

第一次编译时我们需要得到没有设置约束的时序结果,有助于我们给设计添加约束。第二次编译的

时序需要把包含指定时序要求的文件(后缀为 sdc 的文件)添加到工程文件中执行编译,这样工具就能

够按照我们的时序要求来进行映射了。

2.2 mequest 快速入门示例

下面我们按照 altera 公司所给的 mequest 快速入门教程示例来讲解该时序分析工具的大致用法。使

用的工具是目前使用最广泛的 quartusII9.1 版本提供的 TimeQuest 工具。

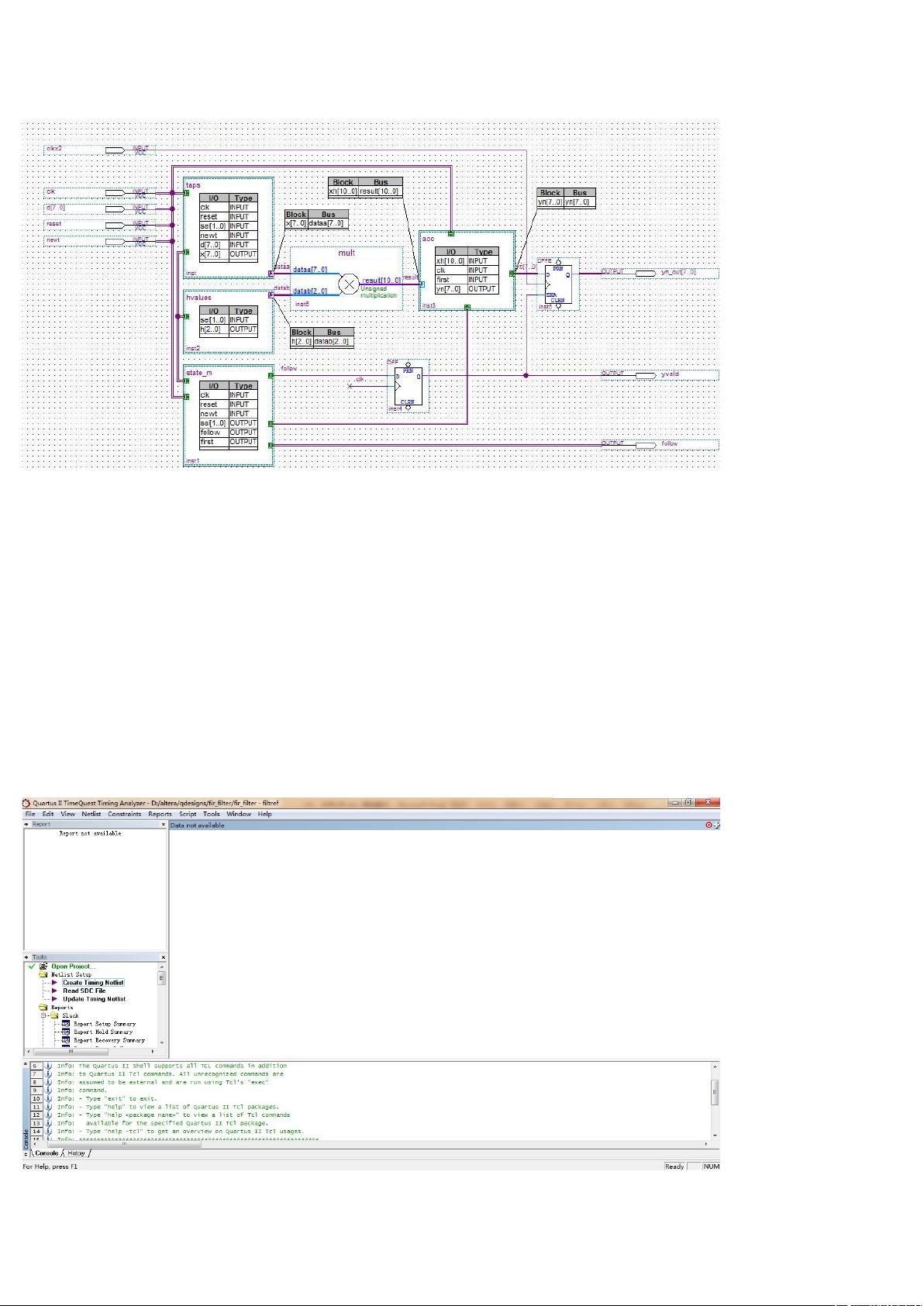

首先我们打开 quartus 工具的例程。在 quartus 工具中选择 File 下的 open project,选择 qdesigns 目录

下的 $r_$lter 工程。打开后我们能够看到如图示的模块结构图。

图 qdesigns 目录下的 FIR 例程

这个工程实现了一个 FIR 模块。其输入端口为 clk,clkx2,reset,newt,d[7:0];输出端口为

follow,yvalid,yn_out[7:0]。clkx2 这个时钟是乘法器输出数据的寄存器触发时钟,而 clk 是整个模块其余部

分的系统时钟。

对这个设计进行时序分析,首先需要在软件中设置mequest作为默认的时序分析工具。以下为设置方

法:在 Assignments 菜单中,点击Se3ngs, Se3ngs对话框出现后,在Category列表下选择Timing Analysis

Se3ngs,开启Use TimeQuest Timing Analyzer during compilaon,选择OK。

设置好后,执行Start Analysis & Synthesis,对项目进行编译。这一步建立了一个post-map的数据库,给

给时序分析工具使用。当然也可以给post-$t数据库,但是对于时序预估,post-map已经足够了,而且运行

的时间会更短。

在tools菜单下,选择TimeQuest Timing Analyzer,启动TimeQuest工具。此时自动打开的是当前的工程。

当出现"No SDC $les were found in the Quartus Se3ngs File and $ltref.sdc doesn't exist. Would you like to

generate an SDC $le from the Quartus Se3ngs File?" 对话框时,选择NO。

剩余7页未读,继续阅读

资源评论

zcl_33

- 粉丝: 16

- 资源: 61

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功