·电子技术及机械工程研究 ·

DDR SDRAM控制器的设计及 FPGA实现

李莺

1

罗毅

1

文广

2

张锋

1

(

1四川理工学院电子与信息工程系 ,四川 自贡 643000; 2攀枝花学院机电工程学院 ,四川 攀枝花 617000

)

摘 要 介绍了 DDR SDRAM控制器的系统命令和结构 ,设计了一种基于状态机的 DDR SDRAM控制器。利

用状态机对读写操作进行控制可提高系统性能 ,给出了基于 FPGA 的控制器的仿真结果。

关键词 DDR SDRAM控制器 ;状态机 ; FPGA

中图分类号 : TP303 文献标识码 : A

作者简介 李莺

(

1973———

)

,女 ,四川南部人 ,讲师 ,主要从事电子技术、智能控制的研究。

1 前言

随着各种处理器工作频率的加快 ,存储器的读写速度以及外围控制电路的性能也就愈加成为直接制

约系统性能的瓶颈。而 SDRAM是一种在外部同步时钟控制下完成数据读写的存储器 ,和一般的 DRAM

一样 , SDRAM需要周期性的刷新操作 ,访问前必须先给出行列地址。其输入信号都用系统时钟的上升沿

锁存 ,使器件可以与系统时钟完全同步操作而不需要握手逻辑。它内嵌了一个同步控制逻辑以支持突发

方式进行的连续读写访问 ,能够达到比传统异步 DRAM 快数倍的存取速度。而且只要给出首地址就可

以对一个存储块访问 ,不需要系统产生和维持后续的地址。另外 ,它具有的可编程同步时序模式和突发

长度使具体使用十分灵活

[ 1 ]

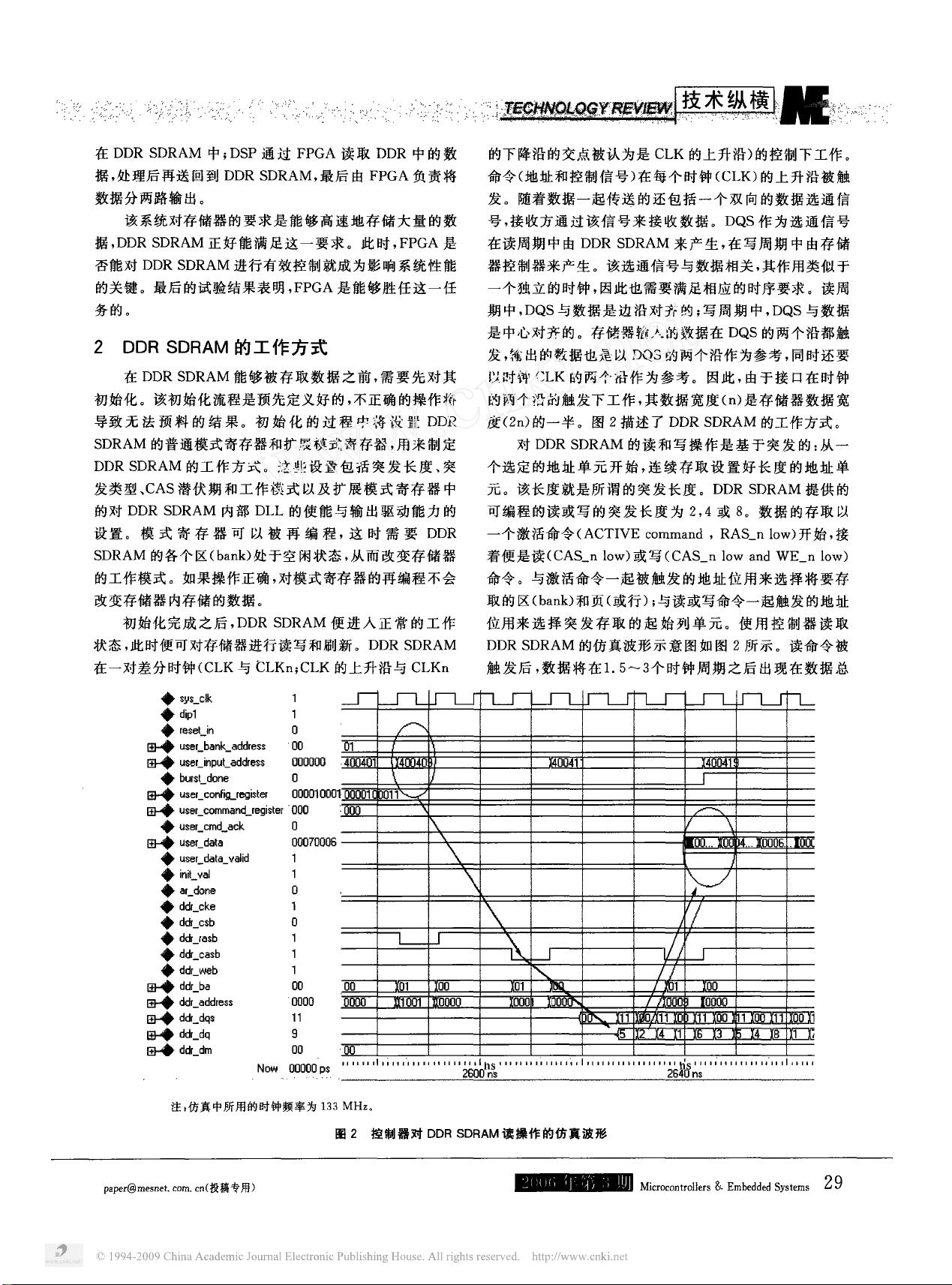

。因 DDR SDRAM允许在时钟脉冲的上升沿和下降沿读写数据 ,而在时钟的

上升沿传输地址和控制信号 ,这就使其能在每个时钟周期完成两次数据传输

[ 2 ]

。不需要提高时钟频率就

能加倍提高速度。

现场可编程门阵列内部逻辑功能能够根据需要进行配置 ,具有很强的灵活性 ,利用 FPGA实现控制

DDR SDRAM控制器不仅可以根据实际要求进行配置 ,充分利用系统资源 ,还可以作为 IP核应用于不同

的系统中 ,加快系统开发速度

[ 3 ]

。

因此 ,使用可编程逻辑器件平台和硬件描述语言 ,针对特定的系统定制自己需要的 DDR SDRAM 控

制器 ,不仅可以节省系统资源 ,而且可以最大限度地发挥 SDRAM 的作用 ,从而提升系统的性能

[ 4 ]

。本文

介绍了一种基于状态机的 DDR SDRAM控制器的设计 ,给出了控制器的系统结构 ,总体模块顶层设计 ,状

态机设计及仿真结果。

2 DDR SDRAM控制器的系统命令和结构

1

)

DDR SDRAM控制器的设计性能

可配置的数据突发长度 2、4、8;可配置的 CAS等待时间 1. 5、2、2. 5、3;支持的 DDR SDRAM命令 :设

置模式寄存器

(

LOAD_MR

)

、自动刷新

(

AUTO_REFRESH

)

、预充电

(

PRECHARGE

)

、激活

(

ACTIVE

)

、自动

预充读

(

READA

)

、自动预充写

(

WR ITEA

)

、突发停止

(

BURST_STOP

)

、空操作

(

NOP

)

;接口速率 100MHz,

双倍数据速率 ;采用片内 DLL s提供 FPGA和 DDR SDRAM之间的零时钟偏移 ;与 DDR SDRAM接口的 I/

O标准是 SSTL2。

2

)

DDR SDRAM控制器的命令及其编码

在具体操作 SDRAM时 ,首先必须通过 MRS命令设置模式寄存器 ,以便确定 SDRAM 的列地址延迟、

突发类型、突发长度等工作模式 ,再通过 ACT命令激活对应地址的组 ,同时输入行地址 ;然后通过 RD或

WR命令输入列地址。将相应数据读出或写入对应的地址 ;操作完成后用 PCH命令或 BS命令中止读或

·92·

第 24卷第 6期 攀枝花学院学报 2007年 12月

Vol. 24. No. 6 Journal of Panzhihua University Dec. 2007

评论2

最新资源