Altera的Standard SDRAM控制器是为使用Verilog HDL进行FPGA设计的工程师们提供的一种高效、可配置的解决方案。这个参考设计旨在帮助用户在Altera FPGA中实现高性能的同步动态随机存取内存(SDRAM)接口。下面将详细介绍这个设计的关键知识点。 1. **同步动态随机存取内存 (SDRAM)**:SDRAM是一种广泛用于计算机系统中的内存类型,它能以与系统时钟同步的方式读写数据,提供较高的数据传输速率。在FPGA设计中,SDRAM常被用来存储大量的中间计算结果或实现高速缓存。 2. **Altera FPGA**:Altera是一家知名的FPGA制造商,其产品广泛应用在通信、汽车、工业、航空等多个领域。FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,允许用户根据需求自定义硬件逻辑。 3. **Verilog HDL**:Verilog是一种硬件描述语言,用于编写数字系统的规范,既可以描述行为,也可以描述结构。在本设计中,Verilog用于描述SDRAM控制器的逻辑功能和时序特性。 4. **SDRAM控制器**:SDRAM控制器是FPGA设计中不可或缺的部分,负责管理与SDRAM芯片的通信,包括初始化、时序控制、地址译码、数据传输等。Altera的Standard SDRAM控制器参考设计提供了完整的解决方案,包括所有必要的控制逻辑和接口。 5. **配置与可定制性**:此参考设计允许用户根据实际应用的需求进行配置,比如支持不同类型的SDRAM芯片、设置不同的数据宽度、时钟频率等。这大大简化了设计流程并提高了设计效率。 6. **仿真与验证**:文件列表中的`simulation`目录可能包含了用于验证设计正确性的仿真模型和测试向量。这些仿真工具可以帮助工程师在实际硬件实现之前发现潜在问题,确保设计的可靠性。 7. **源代码 (`source`目录)**:在这个目录中,用户可以找到用Verilog编写的SDRAM控制器源代码,包括模块定义、例化模板和相关逻辑。通过分析源代码,用户可以理解设计的内部工作原理并进行必要的修改。 8. **文档 (`doc`目录)**:`sdr_sdram.pdf`和`readme_sdr_sdram.txt`可能包含设计概述、使用指南、配置参数说明以及操作步骤等内容。这些文档对理解和使用该参考设计至关重要。 9. **实施与综合**:在理解并配置好参考设计后,工程师需要将其综合进FPGA的逻辑资源,并进行布局布线,最终生成适配特定Altera FPGA的比特流文件。 通过深入学习和实践这个Altera Standard SDRAM控制器参考设计,开发者可以掌握在FPGA上实现高效SDRAM接口的技能,这对于构建高性能、实时处理的嵌入式系统具有重要意义。

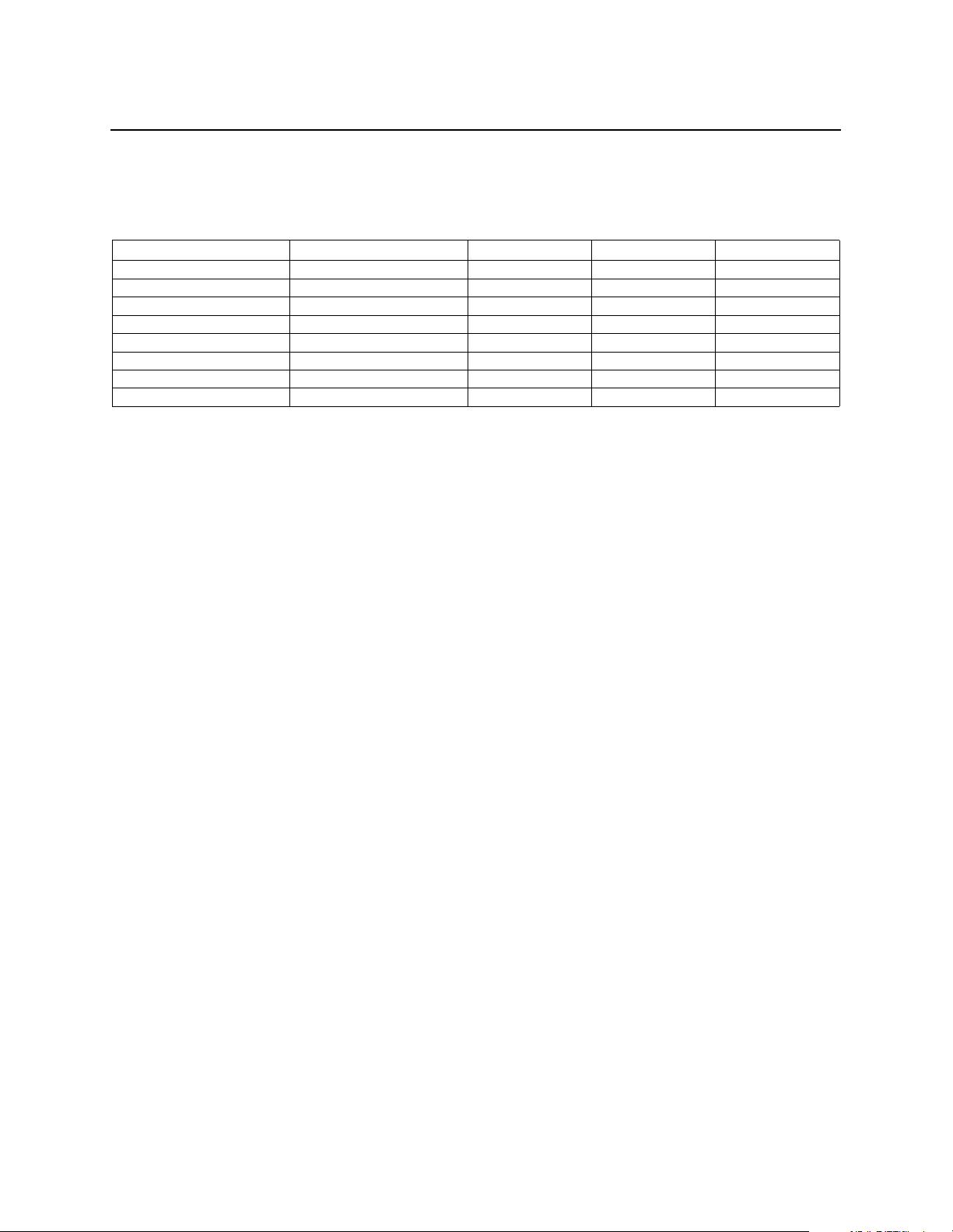

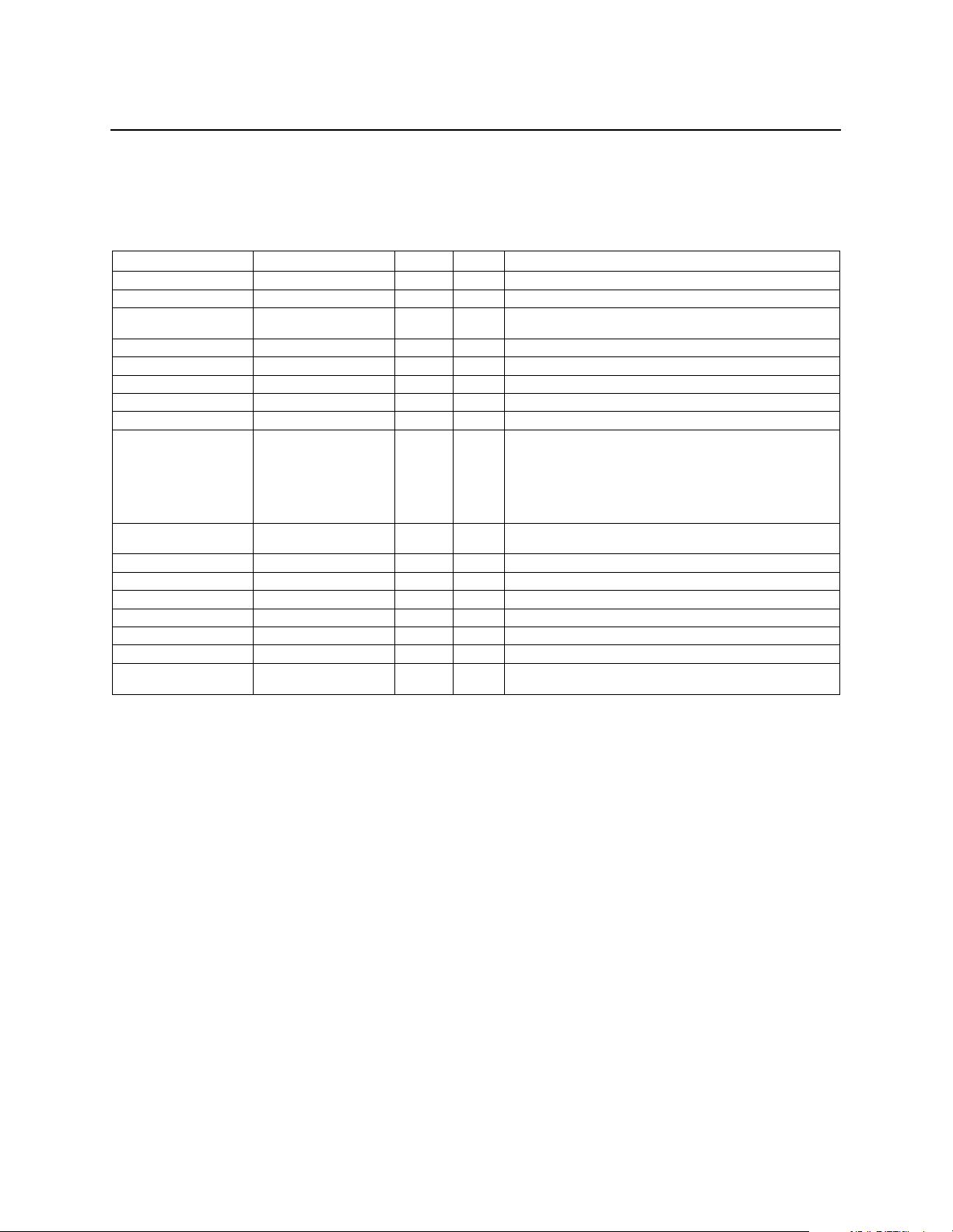

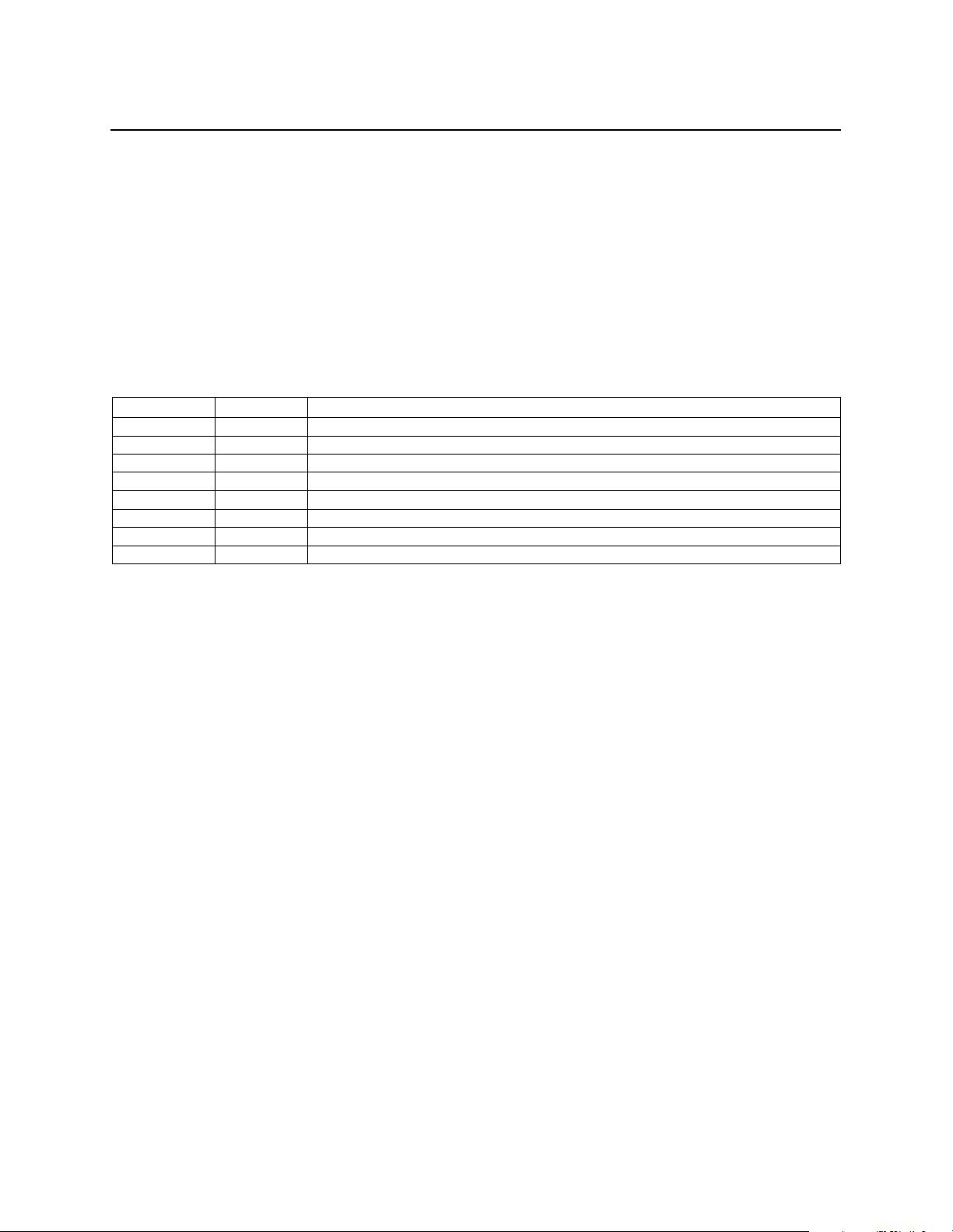

altera标准SRD SDRAM控制器参考设计-verilog.zip (11个子文件)

altera标准SRD SDRAM控制器参考设计-verilog.zip (11个子文件)  simulation

simulation  sdr_sdram_tb.v 22KB

sdr_sdram_tb.v 22KB sdr_sdram.pdf 896KB

sdr_sdram.pdf 896KB readme_sdr_sdram.txt 372B

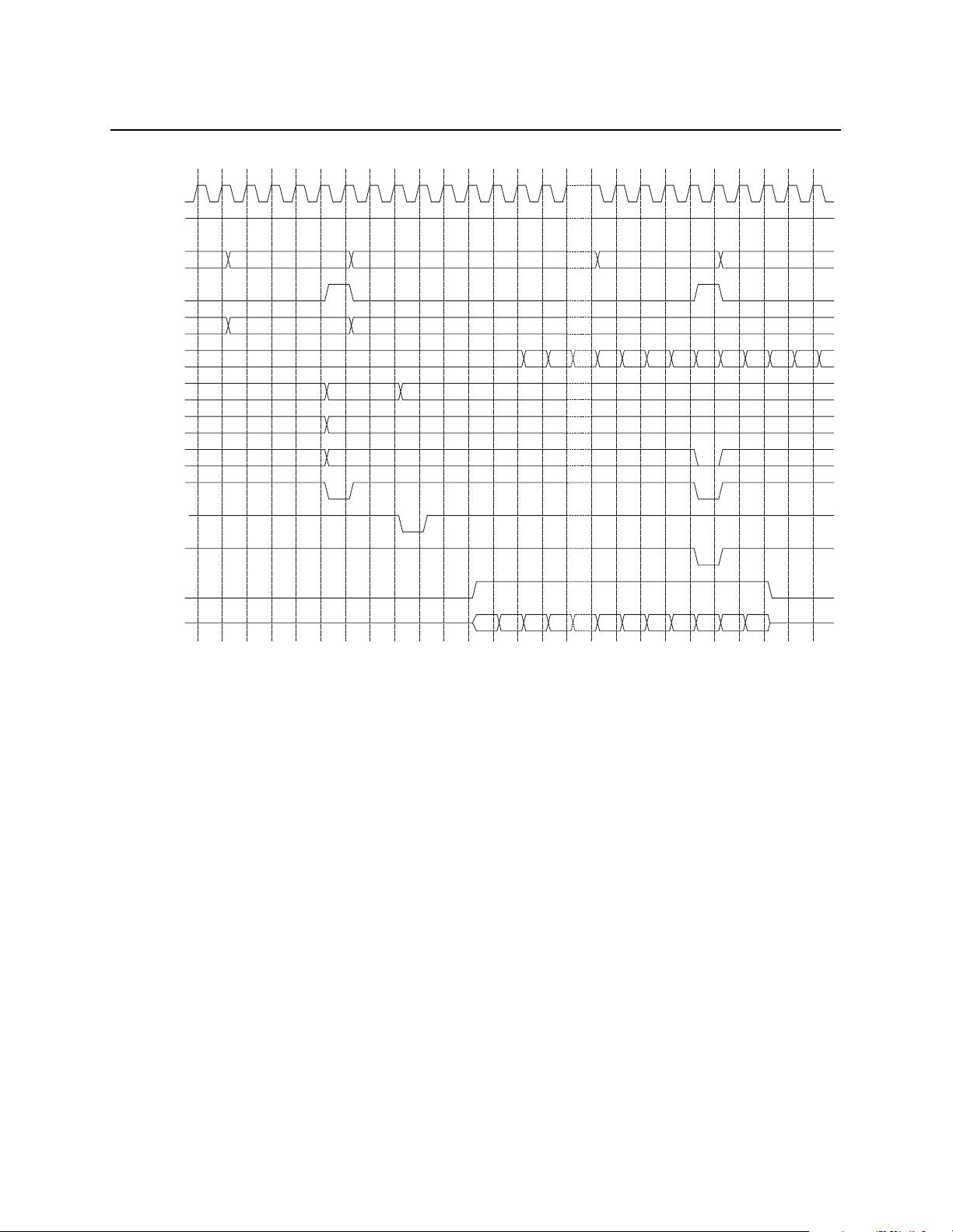

readme_sdr_sdram.txt 372B source

source  PLL1.v 5KB

PLL1.v 5KB sdr_data_path.v 3KB

sdr_data_path.v 3KB Params.v 935B

Params.v 935B Command.v 17KB

Command.v 17KB altclklock.v 8KB

altclklock.v 8KB sdr_sdram.v 7KB

sdr_sdram.v 7KB control_interface.v 8KB

control_interface.v 8KB compile_all.v 206B

compile_all.v 206B doc

doc - 1

- 粉丝: 0

- 资源: 5

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 质量安全排查报告.docx

- 职业中专技工学校专业评估表.docx

- 质量控制资料核查表:建筑保温工程.docx

- 质量目标统计数据表.docx

- 质量内审方案.docx

- 中国古今地名对照表.docx

- 智力残疾评定标准一览表.docx

- 中央造林补助实施方案小班一览表.docx

- 肘关节功能丧失程度评定表.docx

- 重要神经及血管损伤评定.docx

- 自建房安全整治和农村住房建设考评内容和评分标准.docx

- 走访服务企业登记表.doc

- 智能车开发技术的多领域深度解析及应用

- 西红柿叶片图像目标检测数据【已标注,约700张数据,YOLO 标注格式】

- 蓝桥杯开发技术的全面解析与备赛建议

- 相当于去中心化的QQ版本了

信息提交成功

信息提交成功

- 1

- 2

- 3

前往页