没有合适的资源?快使用搜索试试~ 我知道了~

关于SDRAM原理的文章,人个感觉很不错。DRAM 的逻辑 BANK 概念是针对内存颗粒内部的。大家都知道 DRAM 内部的存储单元是以阵列形式 排列的。如下图所示。行列地址总线分别经过行列地址译码器译码后分别指向一行和一列,行列重 叠的单元就是我们所寻找的存储单元,这就是内存芯片寻址的基本原理。对于内存颗粒来说,这个 阵列就是逻辑 Bank(Logical Bank,简称 L-Bank)。

资源推荐

资源详情

资源评论

提到内存,相信大家都不陌生,几乎所有的计算机系统中都有它的身影,按照内存的工作原理

划分,可将内存分为 RAM 和 ROM 两大类。

RAM(Random Access Memory)存储器又称随机存取存储器,存储的内容可通过指令随机读

写访问,RAM 中的数据在掉电时会丢失;

ROM(Read Only Memory)存储器又称只读存储器,只能从中读取信息而不能任意写信息。ROM 具

有掉电后数据可保持不变的优点。

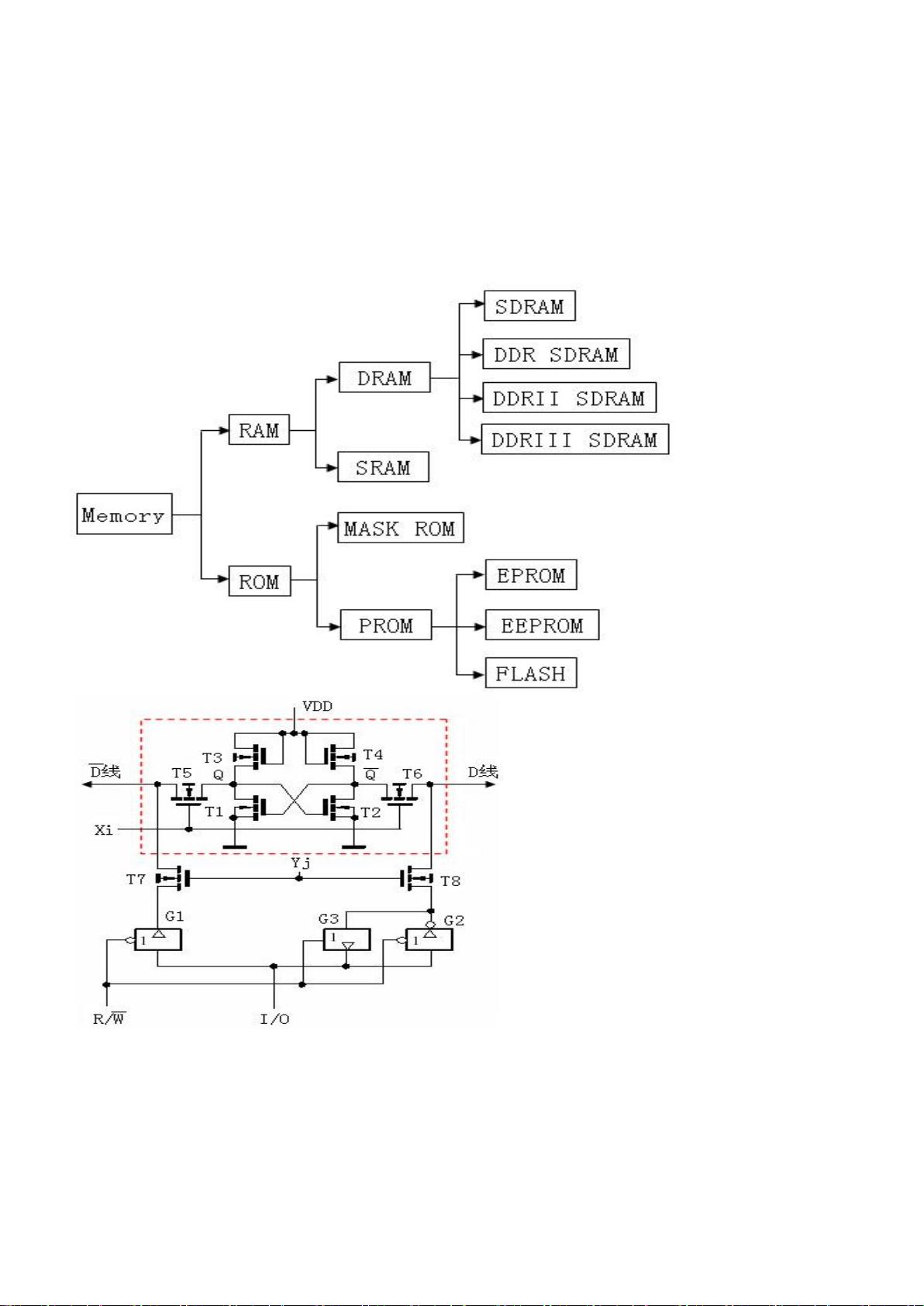

RAM 和 ROM 两大类下面又可分很多小类,如下图所示:

♦SRAM 简介 SRAM 即 Static RAM,也就是静态随机存取存储器,按照制造工艺可分为 NMOS

SRAM、CMOS SRAM 和双极型 SRAM(用的是 TFT)。

SRAM 的基本存储单元是数字锁存器,只要系统不掉电,它就会无限期地保持记忆状态。掉

电时,存储数据会丢失。并且 SRAM 的行列地址线是分开的(DRAM 的行列地址线是复用的)。

SRAM 地特点是读写速度极快,在快速读取和刷新时能够保持数据地完整性,并且

非常省电。所以在一些高速和高可靠性要求电路中,基本上是 SRAM 地天下,如 CPU 的 Cache。但是

SRAM 的存储单元电路结构非常复杂,它内部采用的是双稳态电路的形式来存储数据,制作一个 bit

存储位通常需要 6 个 MOS 管(4 个 MOS 管组成两个交叉耦合反相器,用来锁存数据,另外 2 个用于对

读写操作过程的控制)。由于 SRAM 的复杂电路结构,使得成本要比 DRAM 高很多,而且其集成度低,

很难做成大容量,一般只有几十 KByte 到几百 KByte 的容量,最大也就几 MByte。

上图为 6 个 NMOS 构成的基本 SRAM 存储单元,Xi 和 Yj 为字线;I/O 为数据输入/输出端;

R/W 为读/写控制端。当 R/W=0 时,进行写操作;当 R/W=1 时,进行读操作。图中红色虚线框中的

T1、T2、T3、T4、T5、T6 六个 NMOS 管构成一个基本的存储单元。T1、T3 和 T2、T4 两个反相器交

叉耦合构成触发器。电路采用二元寻址,当字线 Xi 和 Yj 均为高电平时,T5-T8 均导通,则该单元

被选中,若此时 R/W 为 1 的读操作,三态门 G1、G2 关闭,G3 打开,存储的数据从数据线 D,经过

G3,然后从 I/O 输出。若 R/W 为 0 的写操作,则 G1、G2 打开,G3 关闭,I/O 上的数据经 G1、G2 写

入存储单元。

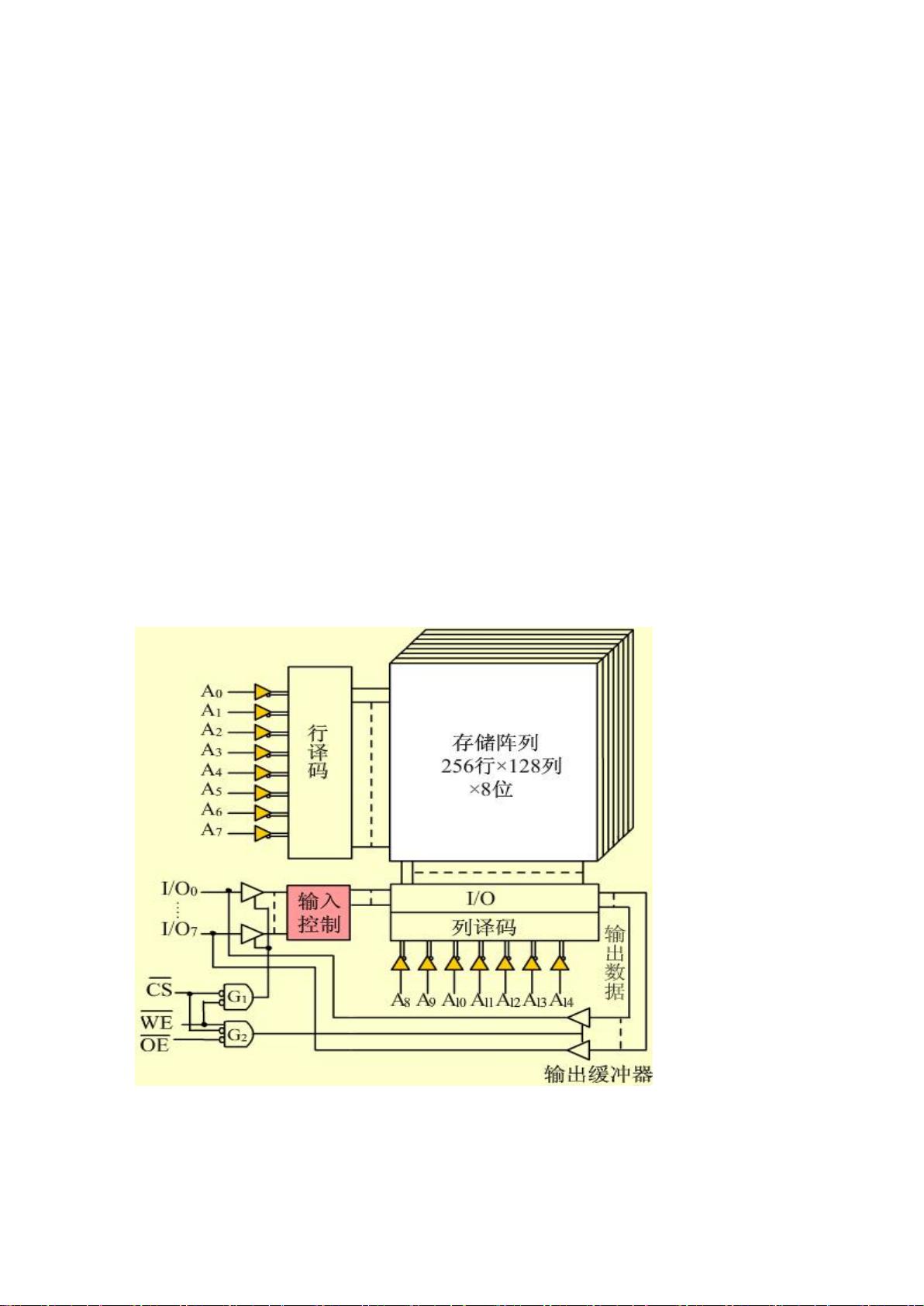

下图为 32KByte 容量的 SRAM 结构示意图,该 SRAM 有 8 位行地址,译码后生成 256 根行

地址线;列地址线为 7 位,译码后生成 128 根列地址线。对 SRAM 进行读操作时,OE#和 CS#为低电

平,WE#为高电平,G1 输出低电平将输入控缓冲器关闭,G2 输出高电平将输出缓冲器打开,通过行

列地址线选中的存储单元数据经 I/O 和输出缓冲器,最后从 I/O[0:7]输出;写操作时,WE#和 CS#

为低电平,OE#为高电平,G1 输出高电平将输入缓冲器打开,G2 输出低电平将输出缓冲器关闭,

I/O[0:7]上的输出经输出缓冲器和内部 I/O 总线,最后写入行列地址选中的存储空间中。

♦DRAM 介绍 DRAM 即 Dynamic RAM,动态随机存取存储器的意思,DRAM 的种类有很多,常用的有:

1).SDRAM:Synchronous Dynamic Random Access Memory,即同步动态随机存取存储器。“同步”

是指其时钟频率与 CPU 前端总线的系统时钟频率相同,并且内部命令的发送与数据的传输都以此频

率为基准;“动态”是指存储阵列需要不断的刷新来保证所存储数据不丢失;“随机”是指数据不

是线性一次存储,而是自由指定地址进行数据的读写。

2).DDR SDRAM:Double Data Rate SDRAM,即双倍速率 SDRAM,普通 SDRAM 只在时钟信号的

上升沿采样数据,而 DDR SDRAM 在时钟信号的上升沿和下降沿都采样数据,这样,在时钟频率不变

的情况下,DDR SDRAM 的数据存取速度提高了一倍,所以叫双倍速率 SDRAM。

DDR SDRAM 最早由三星公司于 1996 年提出,之后与日本电气、三菱、富士通、东芝、日立、

TI、现代等 8 家公司协议制定规格,并得到 AMD、VIA、SIS 等公司的支持,并最终于 2005 年形成

JEDEC 标准 ESD79E。(JEDEC 即 Joint Electron Device Engineering Council,电子器件工程联合

理事会)

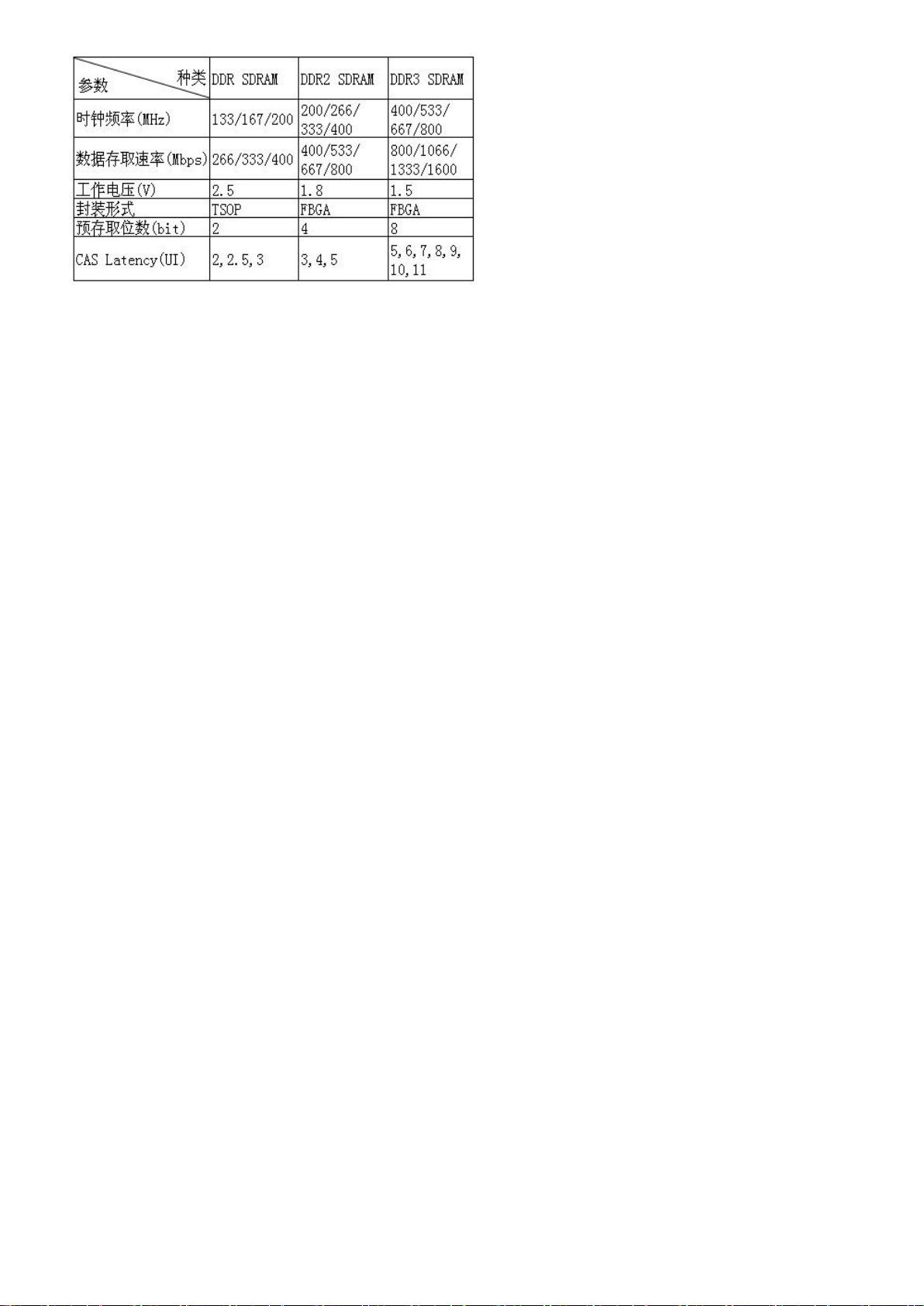

DDR SDRAM 在其短暂的发展史中,先后经历了 DDR SDRAM(也叫 DDR1 SDRAM)、DDR2 SDRAM、DDR3

SDRAM 三个阶段,技术越来越先进。上面是 DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM 三种内存芯片的

参数对比表:

3).RDRAM:Rambus DRAM,是美国的 RAMBUS 公司开发的一种内存。与 DDR 和 SDRAM 不同,

它采用了串行的数据传输模式。RDRAM 的数据存储位宽是 16 位,远低于 DDR 和 SDRAM 的 64 位。但

在频率方面则远远高于前者,可以达到 400MHz 乃至更高。同样也是在一个时钟周期内传输两次次

数据,能够在时钟的上升期和下降期各传输一次数据,内存带宽能达到 1.6Gbyte/s。普通的 DRAM

行缓冲器的信息在写回存储器后便不再保留,而 RDRAM 则具有继续保持这一信息的特性,于是在进

行存储器访问时,如行缓冲器中已经有目标数据,则可利用,因而实现了高速访问。另外其可把数

据集中起来以分组的形式传送,所以只要最初用 24 个时钟,以后便可每 1 时钟读出 1 个字节。一

次访问所能读出的数据长度可以达到 256 字节。下图为 SDRAM 与 RDRAM 系统结构对比。

DRAM 的存储单元结构与 SRAM 的锁存器存储结构不同,DRAM 是利用电容来存储数据信息的,

电容中有电荷代表逻辑“1”,没有电荷代表逻辑“0”,如下图所示。DRAM 进行读/写操作时,行

选信号与列选信号将使存储电容与外界的传输电路导通,从而可进行放电(读取)或充电(写入)。目

前的主流设计中,刷新放大器功能已经被并入读出放大器(Sense Amplifier,简称 S-AMP)中。

剩余17页未读,继续阅读

资源评论

小鹰电子

- 粉丝: 1

- 资源: 7

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功