USER'S MANUAL

S3C2416

16/32-Bit RISC Microprocessor

October 2008

REV 1.10

Confidential Proprietary of Samsung Electronics Co., Ltd

Copyright © 2008 Samsung Electronics, Inc. All Rights Reserved

Important Notice

The information in this publication has been carefully

checked and is believed to be entirely accurate at

the time of publication. Samsung assumes no

responsibility, however, for possible errors or

omissions, or for any consequences resulting from

the use of the information contained herein.

Samsung reserves the right to make changes in its

products or product specifications with the intent to

improve function or design at any time and without

notice and is not required to update this

documentation to reflect such changes.

This publication does not convey to a purchaser of

semiconductor devices described herein any license

under the patent rights of Samsung or others.

Samsung makes no warranty, representation, or

guarantee regarding the suitability of its products for

any particular purpose, nor does Samsung assume

any liability arising out of the application or use of

any product or circuit and specifically disclaims any

and all liability, including without limitation any

consequential or incidental damages.

"Typical" parameters can and do vary in different

applications. All operating parameters, including

"Typicals" must be validated for each customer

application by the customer's technical experts.

Samsung products are not designed, intended, or

authorized for use as components in systems

intended for surgical implant into the body, for other

applications intended to support or sustain life, or for

any other application in which the failure of the

Samsung product could create a situation where

personal injury or death may occur.

Should the Buyer purchase or use a Samsung

product for any such unintended or unauthorized

application, the Buyer shall indemnify and hold

Samsung and its officers, employees, subsidiaries,

affiliates, and distributors harmless against all

claims, costs, damages, expenses, and reasonable

attorney fees arising out of, either directly or

indirectly, any claim of personal injury or death that

may be associated with such unintended or

unauthorized use, even if such claim alleges that

Samsung was negligent regarding the design or

manufacture of said product.

S3C2416 16/32-Bit RISC Microprocessor

User's Manual, Revision 1.10

Publication Number: 21.10-S3-C2416- 082008

Copyright © 2008 Samsung Electronics Co.,Ltd.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in

any form or by any means, electric or mechanical, by photocopying, recording, or otherwise, without the prior

written consent of Samsung Electronics.

Samsung Electronics' microcontroller business has been awarded full ISO-14001

certification (BSI Certificate No. FM24653). All semiconductor products are

designed and manufactured in accordance with the highest quality standards and

objectives.

Samsung Electronics Co., Ltd.

San #24 Nongseo-Dong, Giheung-Gu

Yongin-City, Gyeonggi-Do, Korea

C.P.O. Box #37, Suwon 446-711

TEL: (82)-(31)-209-4593

FAX: (82)-(31)-209-5324

Home Page: http://www.samsungsemi.com

Printed in the Republic of Korea

E-Mail: mobilesol.cs@samsung.com

NOTIFICATION OF REVISIONS

ORIGINATOR: Samsung Electronics, LSI Development Group, Gi-Heung, South Korea

PRODUCT NAME: S3C2416 RISC Microprocessor

DOCUMENT NAME: S3C2416 User's Manual, Revision 1.10

DOCUMENT NUMBER: 21.10-S3-C2416-082008

EFFECTIVE DATE: October, 2008

DIRECTIONS: Revision 1.10

REVISION HISTORY

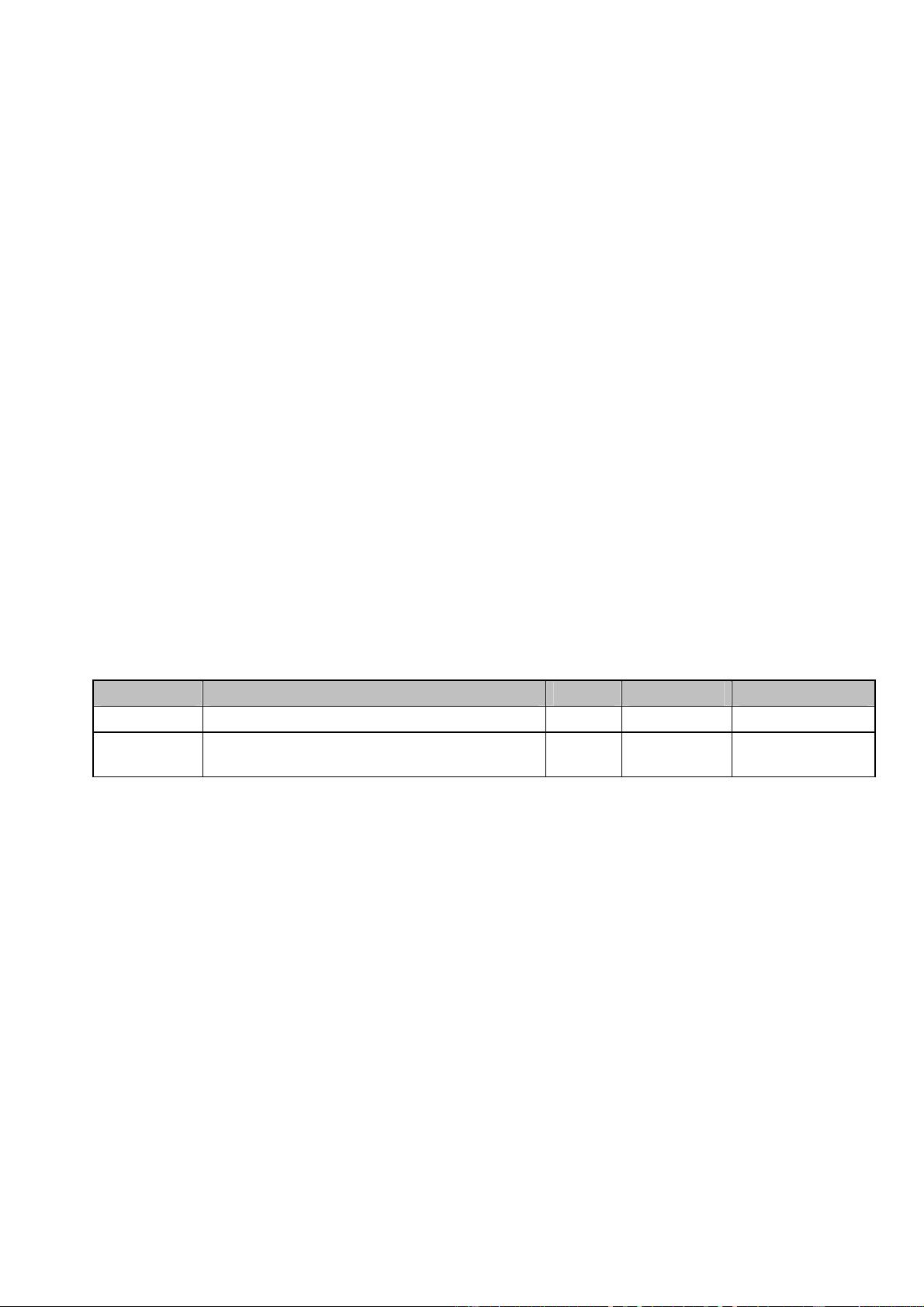

Revision No Description of Change Refer to Author(s) Date

1.00 Initial release - AP app part. August 27, 2008

1.10 Overview, System controller, DMA controller,

I/O ports, LCD controller are updated.

- AP app part. October 06, 2008

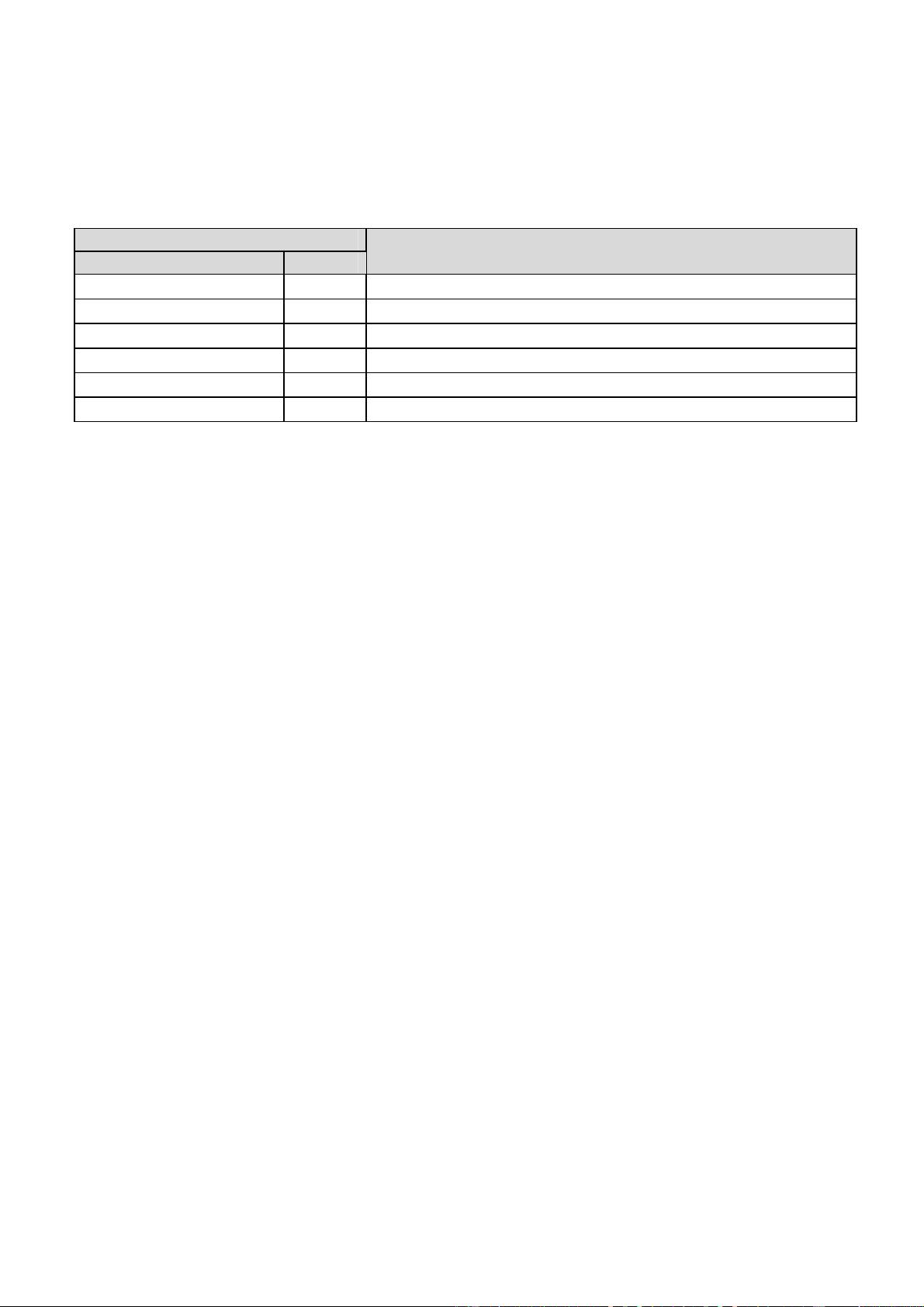

REVISION DESCRIPTIONS FOR REVISION 1.10

Chapter

Chapter Name Page

Subjects (Major changes comparing with last version)

1. Overview 1-2

Way number of Cache Memory is corrected.

2. System controller 2-1,6,8,9

Camera related explanation is removed.

8. DMA controller 8-2

DMA request sources are corrected.

8. DMA controller 8-16,17

Referred Register name, bit and pages are corrected.

10. I/O ports 10-37

CF related description is removed.

21. LCD controller 21-23

Camera related explanation is removed.

S3C2416X RISC MICROPROCESSOR i

Table of Contents

Chapter 1 Product Overview

1 Introduction ...............................................................................................................................................1-1

2 Features....................................................................................................................................................1-2

3 Block Diagram...........................................................................................................................................1-5

4 Pin Assignments .......................................................................................................................................1-6

4.1 Signal Descriptions..........................................................................................................................1-24

4.2 S3C2416 Operation Mode Description ...........................................................................................1-31

4.3 S3C2416 Memory MAP and Base Address of Special Registers...................................................1-32

Chapter 2 System Controller

1 Overview ...................................................................................................................................................2-1

2 Feature......................................................................................................................................................2-1

3 Block Diagram...........................................................................................................................................2-2

4 Functional Descriptions.............................................................................................................................2-3

4.1 Reset Management and Types .......................................................................................................2-3

4.2 Hardware Reset...............................................................................................................................2-3

4.3 Watchdog Reset..............................................................................................................................2-4

4.4 Software Reset ................................................................................................................................2-5

4.5 Wakeup Reset.................................................................................................................................2-5

5 Clock Management...................................................................................................................................2-6

5.1 Clock Generation Overview.............................................................................................................2-6

5.2 Clock Source Selection ...................................................................................................................2-6

5.3 PLL (Phase-Locked-Loop) .............................................................................................................. 2-8

5.4 Change PLL Settings In Normal Operation.....................................................................................2-8

5.5 System Clock Control......................................................................................................................2-9

5.6 ARM & BUS Clock Divide Ratio ......................................................................................................2-10

5.7 Examples for configuring clock regiter to produce specific frequency of AMBA clocks..................2-11

5.8 ESYSCLK Control ...........................................................................................................................2-12

6 Power Management..................................................................................................................................2-13

6.1 Power Mode State Diagram ............................................................................................................2-13

6.2 Power Saving Modes.......................................................................................................................2-14

6.3 Wake-Up Event

...............................................................................................................................2-19

6.4 Output Port State and STOP and SLEEP Mode .............................................................................2-19

6.5 Power Saving Mode Entering/Exiting Condition..............................................................................2-20

7 Register Descriptions................................................................................................................................2-21

7.1 Address Map ...................................................................................................................................2-21