精简8位CPU电路设计

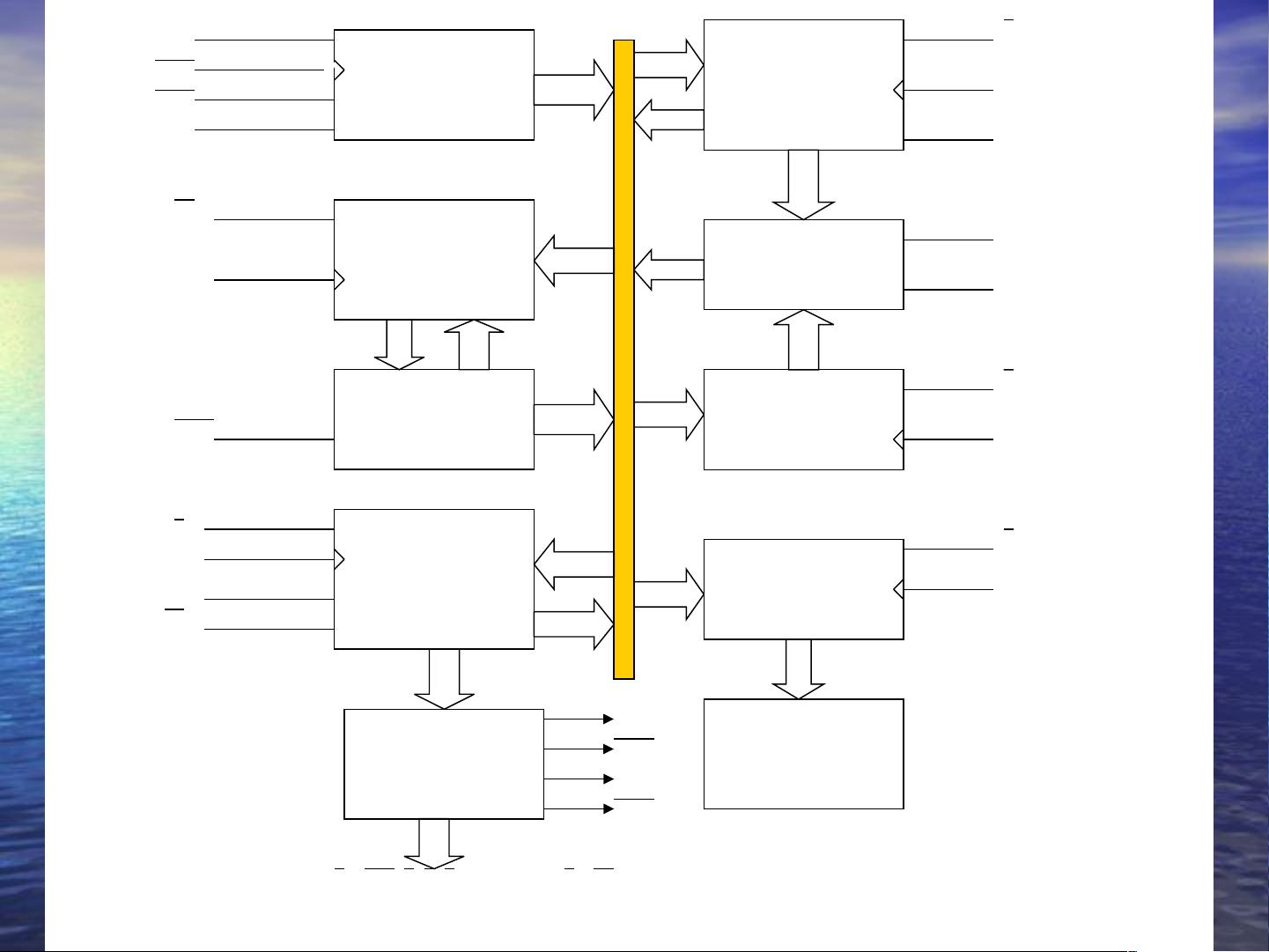

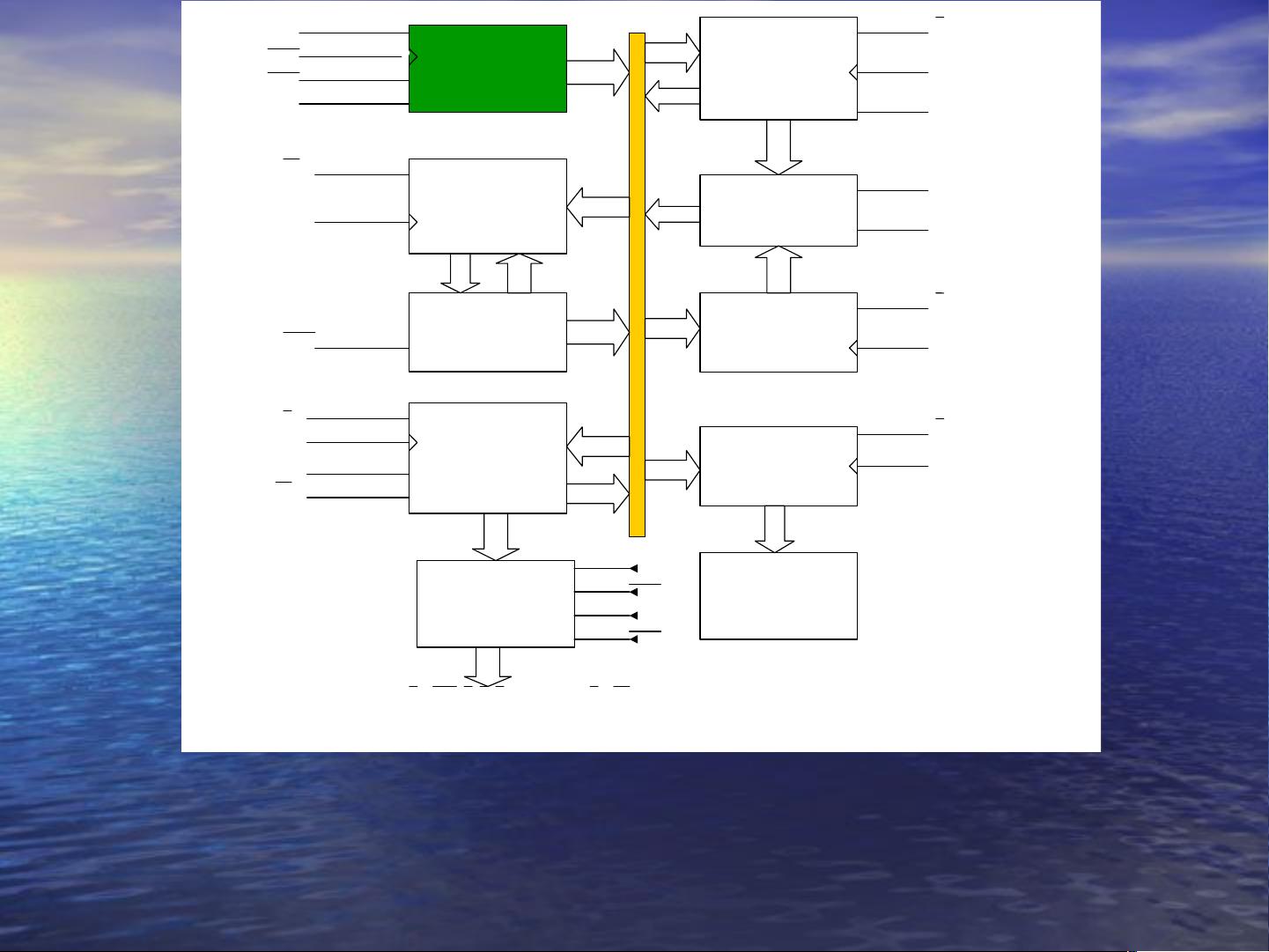

8位CPU电路设计涉及到计算机硬件的基本构建,特别是微处理器的核心组成部分。SAP-1 CPU是一个典型的8位CPU模型,用于教学和理解计算机体系结构。在这个设计中,我们关注的主要组件包括程序计数器、内存访问寄存器(MAR)、16*8 ROM以及控制器/顺序器等。 1. **程序计数器**(Program Counter, PC) 程序计数器是一个4位的计数器,能存储从0到15的16个地址。在CPU执行指令时,它负责存储当前要执行指令的地址,并在每次执行完一条指令后自动递增,以便指向下一条指令的地址。这个过程使得程序能够按照一定的顺序执行。 2. **内存访问寄存器**(Memory Access Register, MAR) MAR分为两部分,一个接收来自输入的数据,这部分用于存取内存中的程序和数据;另一个部分则在CPU执行指令时,临时存储即将执行的下一条指令的地址。MAR与程序计数器协同工作,确保了指令的正确获取和执行。 3. **16*8 ROM** ROM(Read-Only Memory)是一种非易失性存储器,其中的数据在断电后仍能保留。在SAP-1 CPU中,使用了一个16行*8列的ROM,总共可以存储128个8位的指令或数据。ROM的地址总线为4位,允许从0000到1111共16个地址进行选择,每个地址对应8位的数据。这使得CPU能够访问并执行预定义的程序。 4. **控制器/顺序器** 控制器/顺序器负责解析从ROM中读取的指令,并生成必要的控制信号,以协调CPU内部各个部件的操作,如累加器、算术逻辑单元(Adder/Subtractor)、输出寄存器等。这些部件共同参与运算、数据处理和结果输出。 5. **体系结构** SAP-1 CPU遵循的是经典的冯·诺依曼结构,其中程序和数据共享同一内存空间。冯·诺依曼结构的特点是程序存储在内存中,通过程序计数器来顺序执行指令。对比之下,哈佛结构则是程序和数据使用独立的存储系统。x86和51系列处理器属于冯·诺依曼结构,而ARM架构则是改进型的哈佛结构,即数据和指令虽然有各自的总线,但在物理上可以重叠。 在设计8位CPU电路时,除了上述组件,还需要考虑地址总线、数据总线、控制总线的交互,以及各种时钟信号(如CLK)的同步。此外,还需要处理诸如清除(CLR)、使能(EN)和读写(R/W)等控制信号,确保CPU的正常操作。仿真环节则用于验证设计的正确性,通过模拟实际运行过程来检查硬件是否按预期工作。8位CPU电路设计是一个复杂而精细的过程,涵盖了计算机科学的基础原理和技术实现。

剩余51页未读,继续阅读

simymo22013-09-28可以用, 十分好

simymo22013-09-28可以用, 十分好

- 粉丝: 0

- 资源: 4

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- VB+ACCESS宾馆客房管理系统(系统+论文+封面)(2024y3).7z

- VB+access成绩分析统计系统(论文+源代码)(2024tz).7z

- vb+access大气污染模型(系统+翻译+论文+开题)(2024wa).7z

- vb+access抽奖系统(系统+论文+开题报告+外文翻译+封面+中英摘要+任务书+中期检查表)(2024ou).7z

- VB+ACCESS大型机房学生上机管理系统(源代码+系统)(2024n5).7z

- VB+ACCESSVCD租借管理系统(系统+论文+需要分析)(20248q).7z

- php学籍管理系统pc-毕业设计(2024bt).7z

- wangfang1.pdf

- wangfang.pdf

- 《Qt5开发实战》书+源码.zip

- 数学计算中的平方表与圆周率π的应用

- 圣诞树网页的HTML与CSS代码实例

- Java商城-商城演示和商城项目

- 改进的大规模语音合成模型CosyVoice 2: 统一流式与非流式合成

- 全平台数据库管理工具MySQL

- 开源源码分享动态圣诞树

信息提交成功

信息提交成功