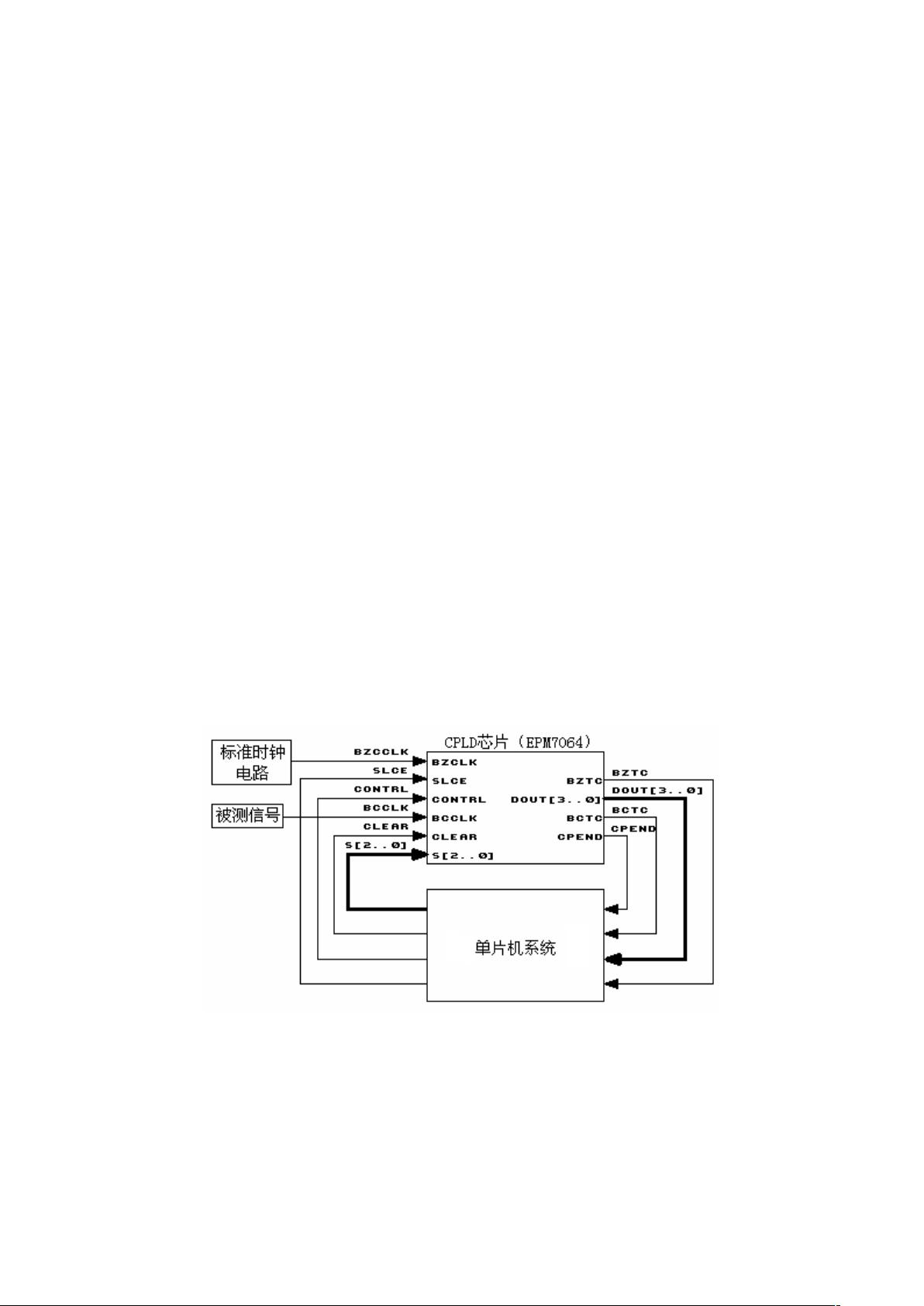

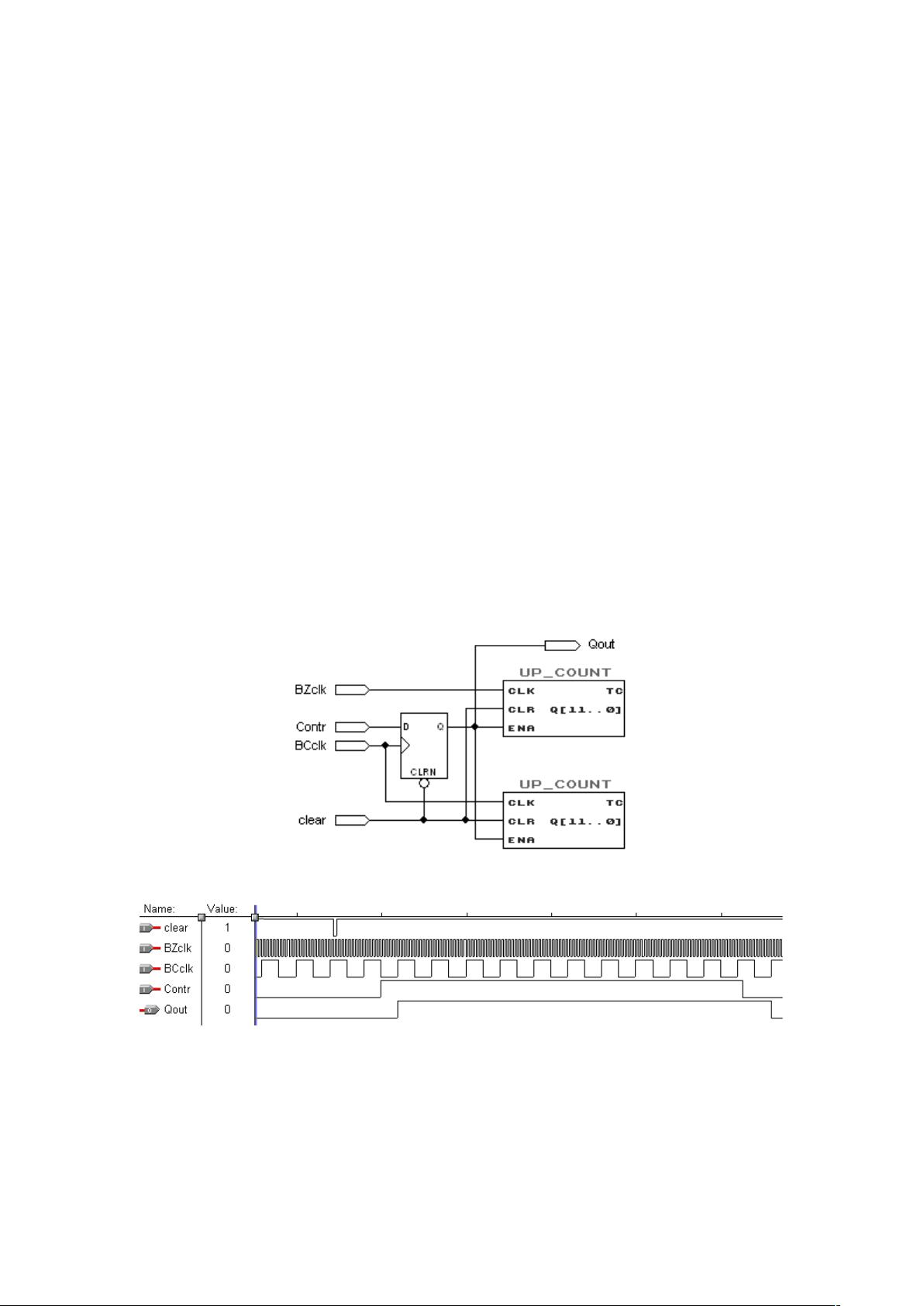

设计与实现等精度测频方法 等精度测频法是一种高精度的频率测量方法,旨在消除传统频率测量方法中的两个主要误差因素,即闸门时间的准确度和对低频信号的取整误差。本文将详细介绍等精度测频法的设计与实现原理、工作原理和功能设计。 设计原理: 传统频率测量方法是对设定的闸门时间内脉冲进行计数,但这种方法存在两个主要误差因素:闸门时间的准确度和对低频信号的取整误差。为了消除这些误差,等精度测频法选择了复杂可编程逻辑器件(CPLD)与低功耗单片机相结合,CPLD 完成高频信号计数,单片机完成低频信号计数、频率和占空比计算和显示控制等功能。 工作原理: 等精度测频工作原理如图 8-2 所示。闸门时间控制信号 Contr 并不直接作用于计数器计数使能端 ENA,而是经 D 触发器再作用于 ENA,D 触发器的触发信号为被测频率信号 BCclk,通过此 D 触发器消除了被测频率信号取整误差。被测频率信号 BCclk 计数值 NC 与标准频率信号 BZclk 计数值 NB 是同一时间计数值,通过关系式(1)即可计算出被测频率。 功能设计: 基于等精度测频法的设计原理和工作原理,采用图形法与 VHDL 语言混合设计方法对 CPLD 进行功能设计,整体功能图如图 8-4 所示。其中各单元模块功能、内部结构分别介绍如下: (1)UP_COUNT 单元:带进位、使能和清零端 16 位加计数器。 (2)DOWN_COUNT 单元:带进位、使能和清零端 16 位减计数器。 (3)COMPARATOR 单元:比较器,用于比较被测频率信号计数值和标准频率信号计数值。 (4)CONTROL 单元:控制单元,用于控制计数器的使能和清零。 (5)INTERFACE 单元:接口单元,用于接收和发送控制信号和数据信号。 等精度测频法是一种高精度的频率测量方法,通过选择合适的闸门时间和提高标准频率信号频率可以加以抑制取整误差,实现高精度的频率测量。

剩余7页未读,继续阅读

- 粉丝: 4

- 资源: 4

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 嵌入式开发_ARM_入门_STM32迁移学习_1741139876.zip

- 嵌入式系统_STM32_自定义Bootloader_教程_1741142157.zip

- 文章上所说的串口助手,工程文件

- 斑马打印机zpl官方指令集

- 《实验二 面向对象编程》

- 《JavaScript项目式实例教程》项目五多窗体注册页面窗口对象.ppt

- Web前端开发中Vue.js组件化的应用详解

- labelme已打包EXE文件

- 一文读懂Redis之单机模式搭建

- Vue综合案例:组件化开发

- 《SolidWorks建模实例教程》第6章工程图及实例详解.ppt

- C语言基础试题.pdf

- Go语言、数据库、缓存与分布式系统核心技术要点及面试问答详解

- 7天精通DeepSeek实操手册.pdf

- DeepSeek R1 Distill 全版本安全评估.pdf

- DeepSeek 零基础入门手册.pdf

信息提交成功

信息提交成功