基于FPGA分布式算法的FIR滤波器的设计

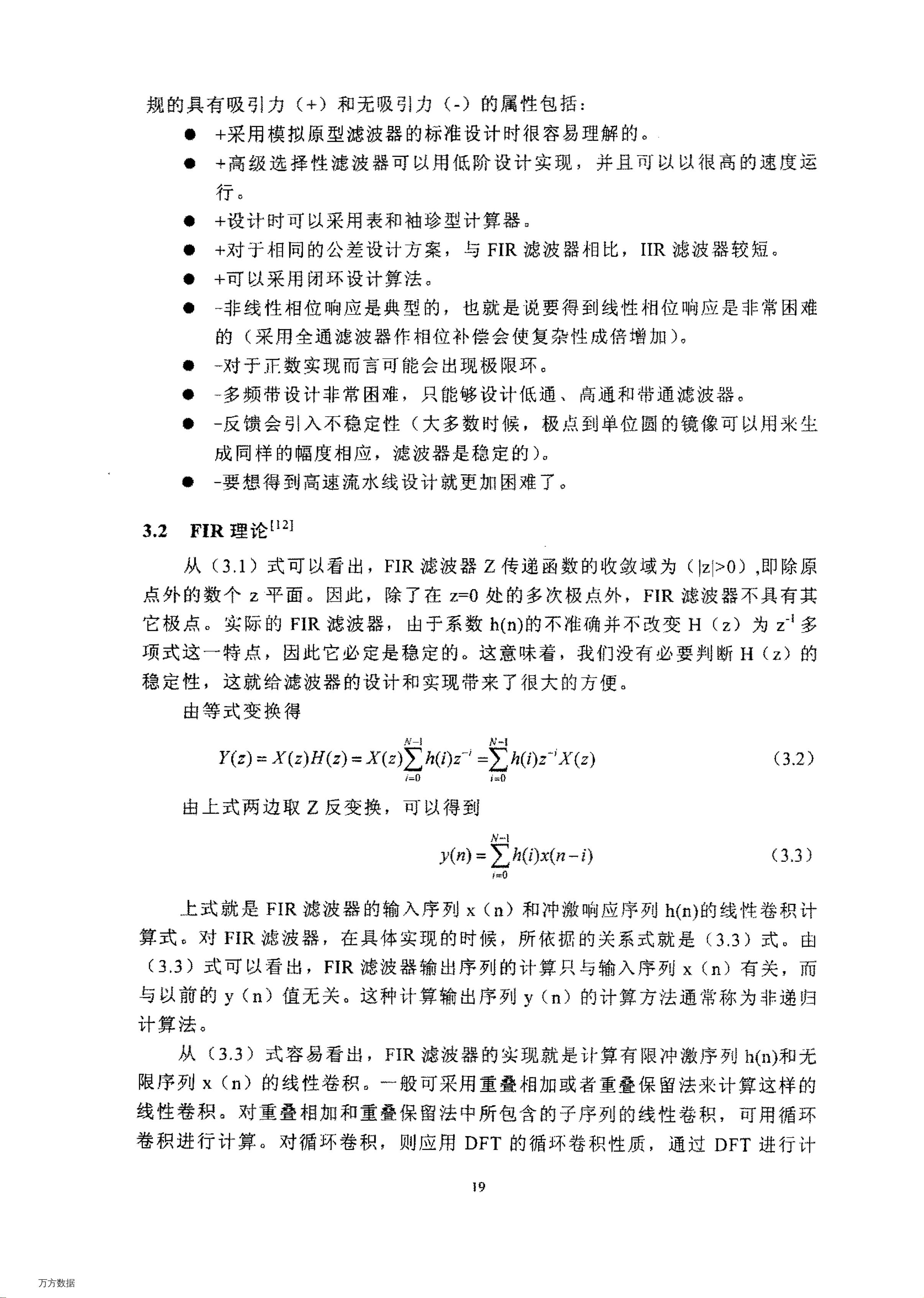

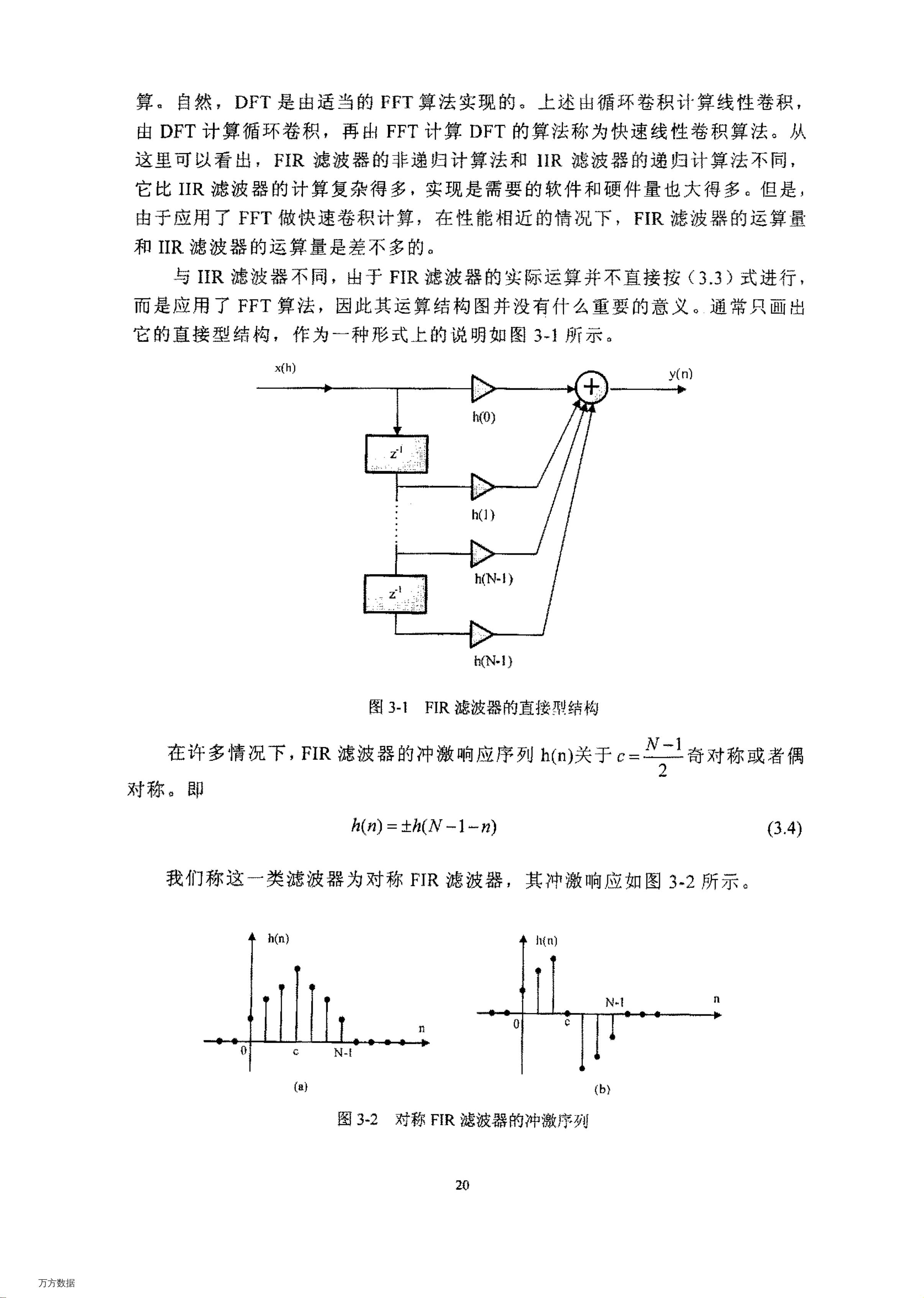

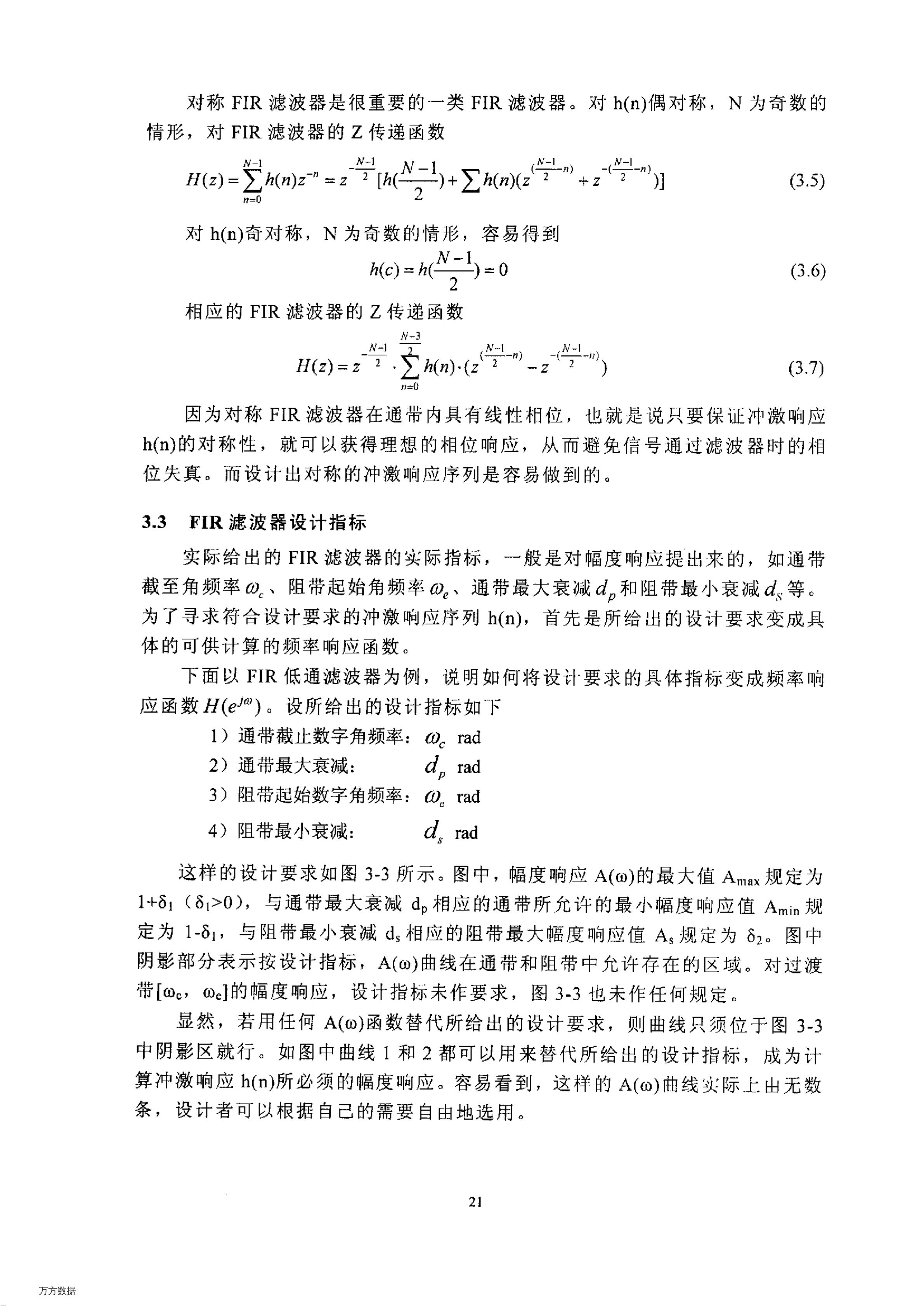

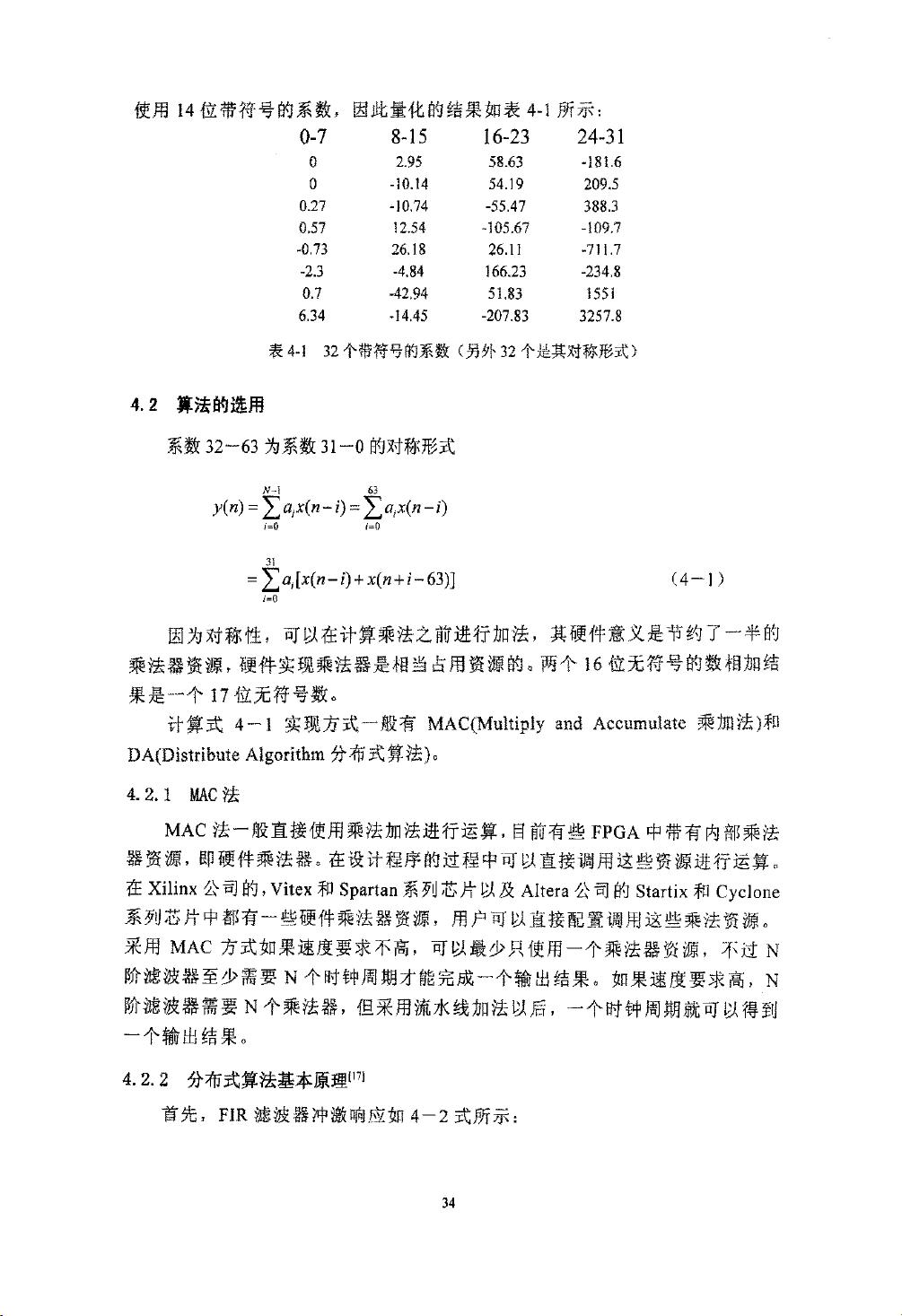

标题中的“基于FPGA分布式算法的FIR滤波器的设计”揭示了本次讨论的核心主题,即如何使用Field Programmable Gate Array(FPGA)的分布式算法实现Finite Impulse Response(FIR)滤波器。FIR滤波器是一种广泛应用在信号处理中的数字滤波器,它通过计算输入信号与一组预定义系数的卷积来产生输出信号,从而实现对信号的平滑、降噪或频谱选择性增强。 分布式算法,也称为FPDA(Fixed-Point Distributed Arithmetic),是FPGA设计中优化计算资源利用的一种策略。这种算法将复杂的乘法运算分解为一系列加法和移位操作,显著降低了硬件需求,提高了计算效率,特别适合在资源有限的FPGA平台上实现高性能的FIR滤波器。 Quartus II是Altera公司(现Intel FPGA部门)开发的一款综合工具,用于FPGA设计、仿真、编程和调试。在这个项目中,Quartus II将被用来实现FIR滤波器的逻辑设计,编译和下载到目标FPGA设备中。 设计FPGA上的分布式FIR滤波器,首先需要理解滤波器的结构。FIR滤波器通常由多个延迟线和加权单元组成,每个延迟线存储一个采样值,加权单元则对应滤波器系数,对延迟线中的采样值进行加权求和。分布式算法可以将乘法器分解为多个部分,这些部分在FPGA的不同逻辑块中实现,使得设计更易于并行化。 在Quartus II中,设计流程通常包括以下步骤: 1. **设计输入**:编写滤波器的算法描述,例如使用VHDL或Verilog硬件描述语言。 2. **逻辑综合**:使用Quartus II的综合工具将高级语言描述转化为逻辑门级表示,优化资源利用率。 3. **适配和布局布线**:Quartus II自动将逻辑门分配到FPGA的物理资源,并进行布线以确保信号传输。 4. **时序分析**:检查设计是否满足速度要求,如最大时钟频率。 5. **编程和验证**:将编译后的比特流文件下载到FPGA中,并通过硬件接口验证滤波器的功能和性能。 在实际应用中,还需要考虑滤波器的性能指标,如通带纹波、阻带衰减、过渡带宽度等,以及FPGA资源的利用率和功耗。对于FPGA的分布式算法实现,还需要关注数据路径的固定点表示,以保证精度和效率之间的平衡。 压缩包内的“基于FPGA分布式算法的FIR滤波器的设计”可能是详细的设计报告、源代码文件或相关的实验数据。通过深入研究这些内容,可以进一步了解具体的设计细节和技术实现。

FPGA分布式算法的FIR滤波器的设计.rar (26个子文件)

FPGA分布式算法的FIR滤波器的设计.rar (26个子文件)  基于FPGA分布式算法的FIR滤波器的设计

基于FPGA分布式算法的FIR滤波器的设计  default.htm 294B

default.htm 294B Paper

Paper  pdf

pdf  y86976401.pdf 59KB

y86976401.pdf 59KB fm.htm 2KB

fm.htm 2KB y869764wz.pdf 43KB

y869764wz.pdf 43KB left.htm 5KB

left.htm 5KB y8697640005.pdf 393KB

y8697640005.pdf 393KB y8697640009.pdf 42KB

y8697640009.pdf 42KB y8697640008.pdf 1.09MB

y8697640008.pdf 1.09MB y86976403.pdf 25KB

y86976403.pdf 25KB y869764zye.pdf 51KB

y869764zye.pdf 51KB ml.htm 4KB

ml.htm 4KB y8697640006.pdf 508KB

y8697640006.pdf 508KB y86976402.pdf 27KB

y86976402.pdf 27KB y8697640007.pdf 430KB

y8697640007.pdf 430KB index.htm 428B

index.htm 428B y8697640010.pdf 51KB

y8697640010.pdf 51KB y8697640004.pdf 50KB

y8697640004.pdf 50KB Images

Images  bg.gif 2KB

bg.gif 2KB T.gif 61B

T.gif 61B I.gif 61B

I.gif 61B H.gif 62B

H.gif 62B ball.gif 841B

ball.gif 841B L.gif 60B

L.gif 60B nfolder.gif 86B

nfolder.gif 86B ofolder.gif 92B

ofolder.gif 92B folder.gif 95B

folder.gif 95B- 1

brwex2014-05-01这个里边就是复制的论文

brwex2014-05-01这个里边就是复制的论文 shujinyu2012-04-18不错 但有些地方讲的不是很清楚哦 还得自己查些资料

shujinyu2012-04-18不错 但有些地方讲的不是很清楚哦 还得自己查些资料 freedomfox2012-06-04感谢分享,这应该是论文,没有附源程序。第四章是设计流程,前三章论文凑字数。

freedomfox2012-06-04感谢分享,这应该是论文,没有附源程序。第四章是设计流程,前三章论文凑字数。

- 粉丝: 207

- 资源: 265

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功