没有合适的资源?快使用搜索试试~ 我知道了~

AD6636数据手册 很细致的英文 可以看看研究研究

资源推荐

资源详情

资源评论

150 MSPS, Wideband,

Digital Downconverter (DDC)

AD6636

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable.

However, no responsibility is assumed by Analog Devices for its use, nor for any

infringements of patents or other rights of third parties that may result from its use.

Specifications subject to change without notice. No license is granted by implication

or otherwise under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 www.analog.com

Fax: 781.461.3113 © 2005 Analog Devices, Inc. All rights reserved.

FEATURES

4/6 independent wideband processing channels

Processes 6 wideband carriers (UMTS, CDMA2000)

4 single-ended or 2 LVDS parallel input ports

(16 linear bit plus 3-bit exponent) running at 150 MHz

Supports 300 MSPS input using external interface logic

Three 16-bit parallel output ports operating up to 200 MHz

Real or complex input ports

Quadrature correction and dc correction for complex inputs

Supports output rate up to 34 MSPS per channel

RMS/peak power monitoring of input ports

Programmable attenuator control for external gain ranging

3 programmable coefficient FIR filters per channel

2 decimating half-band filters per channel

6 programmable digital AGC loops with 96 dB range

Synchronous serial I/O operation (SPI®-, SPORT-compatible)

Supports 8-bit or 16-bit microport modes

3.3 V I/O, 1.8 V CMOS core

User-configurable, built-in, self-test (BIST) capability

JTAG boundary scan

APPLICATIONS

Multicarrier, multimode digital receivers

GSM, EDGE, PHS, UMTS, WCDMA, CDMA2000, TD-SCDMA,

WiMAX

Micro and pico cell systems, software radios

Broadband data applications

Instrumentation and test equipment

Wireless local loops

In-building wireless telephony

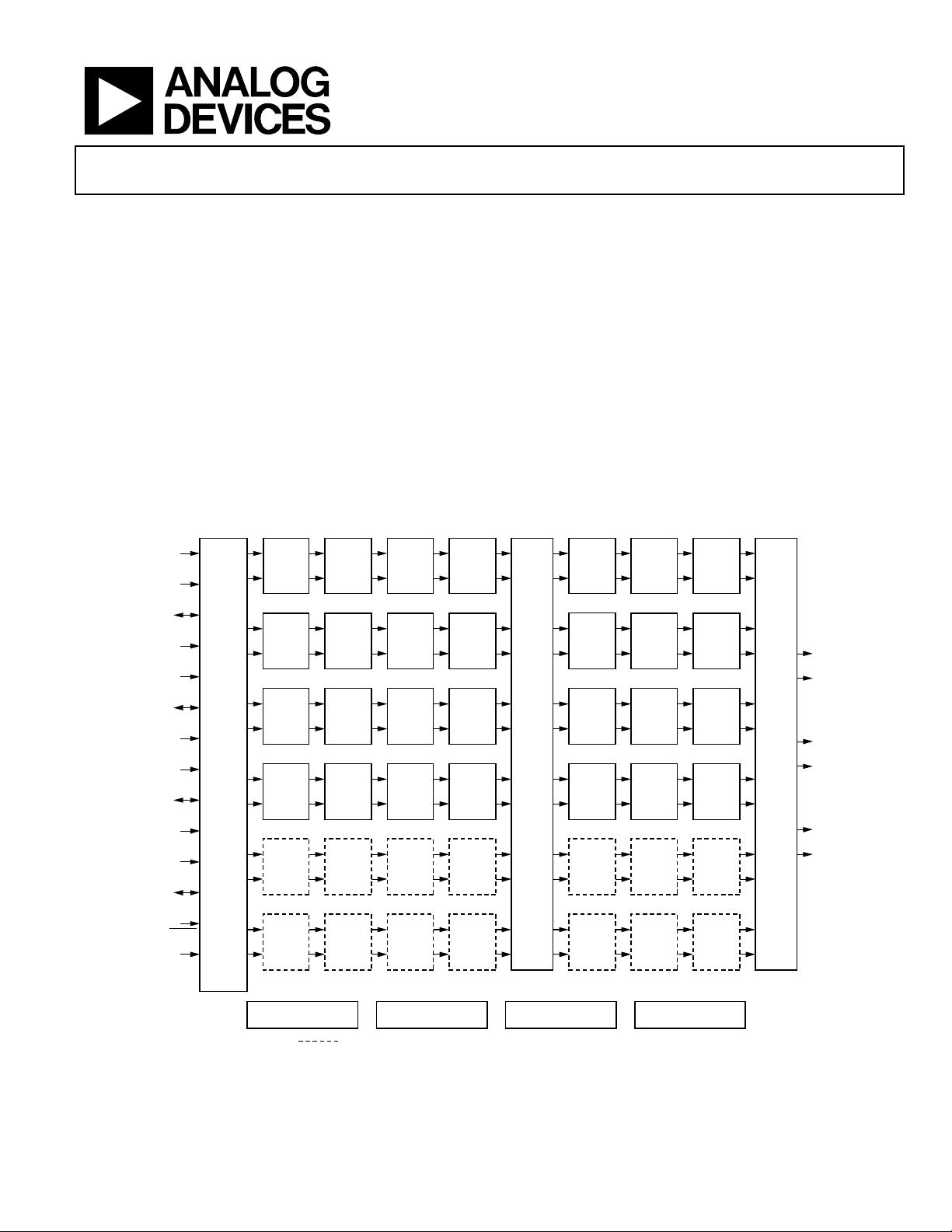

FUNCTIONAL BLOCK DIAGRAM

INPUT MATRIX

CMOS

REAL

PORTS

A, B,

C, D

CMOS

COMPLEX

PORTS

(AI, AQ)

(BI, BQ)

LVDS

PORTS

AB, CD

PEAK/

RMS

MEAS.

I,Q

CORR.

PRN GEN

SYNC [3:0]

RESET

DATA ROUTER MATRIX

DATA ROUTING

AGC

PARALLEL PORTS

FIR2

HB2

M = Byp, 2

CIC5

M = 1-32

NCO

FIR1

HB1

M = Byp, 2

CRCF

M = 1-16

MRCF

DRCF

M = 1-16

LHB

L = Byp, 2

FIR2

HB2

M = Byp, 2

CIC5

M = 1-32

NCO

FIR1

HB1

M = Byp, 2

CRCF

M = 1-16

MRCF

DRCF

M = 1-16

LHB

L = Byp, 2

FIR2

HB2

M = Byp, 2

CIC5

M = 1-32

NCO

FIR1

HB1

M = Byp, 2

CRCF

M = 1-16

MRCF

DRCF

M = 1-16

LHB

L = Byp, 2

FIR2

HB2

M = Byp, 2

CIC5

M = 1-32

NCO

FIR1

HB1

M = Byp, 2

CRCF

M = 1-16

MRCF

DRCF

M = 1-16

LHB

L = Byp, 2

FIR2

HB2

M = Byp, 2

CIC5

M = 1-32

NCO

FIR1

HB1

M = Byp, 2

CRCF

M = 1-16

MRCF

DRCF

M = 1-16

LHB

L = Byp, 2

FIR2

HB2

M = Byp, 2

CIC5

M = 1-32

NCO

FIR1

HB1

M = Byp, 2

CRCF

M = 1-16

MRCF

DRCF

M = 1-16

LHB

L = Byp, 2

PA

PB

PC

ADC B/AQ

CLKB

EXPB [2:0]

ADC A/AI

CLKA

EXPA [2:0]

ADC D/CQ

CLKD

EXPD [2:0]

ADC C/CI

CLKC

EXPC [2:0]

16-BIT

MICROPORT INTERFACE

SPORT/SPI INTERFACE JTAG

PLL CLOCK

MULTIPLIER

M = DECIMATION L = INTERPOLATIONARE AVAILABLE ONLY IN 6-CHANNEL PART

04998-0-001

NOTE: CHANNELS RENDERED A

S

Figure 1.

AD6636

Rev. A | Page 2 of 80

TABLE OF CONTENTS

General Description......................................................................... 4

Specifications..................................................................................... 6

Recommended Operating Conditions ...................................... 6

Electrical Characteristics............................................................. 6

General Timing Characteristics

,

................................................ 7

Microport Timing Characteristics

,

............................................ 8

Serial Port Timing Characteristics

, ,

........................................... 9

Explanation of Test Levels for Specifications............................ 9

Absolute Maximum Ratings.......................................................... 10

Thermal Characteristics ............................................................ 10

ESD Caution................................................................................ 10

Pin Configuration and Function Descriptions........................... 11

Pin Listing for Power, Ground, Data, and Address Buses..... 13

Timing Diagrams............................................................................ 14

Theory of Operation ...................................................................... 20

ADC Input Port .......................................................................... 20

PLL Clock Multiplier ................................................................. 21

ADC Gain Control..................................................................... 22

ADC Input Port Monitor Function.......................................... 23

Quadrature I/Q Correction Block............................................ 25

Input Crossbar Matrix ............................................................... 27

Numerically Controlled Oscillator (NCO)............................. 27

Fifth-Order CIC Filter ............................................................... 29

FIR Half-Band Block.................................................................. 30

Intermediate Data Router ......................................................... 33

MonoRate RAM Coefficient Filter (MRCF)........................... 33

Decimating RAM Coefficient Filter (DRCF) ......................... 34

Channel RAM Coefficient Filter (CRCF) ............................... 36

Interpolating Half-Band Filter.................................................. 38

Output Data Router ................................................................... 38

Automatic Gain Control............................................................ 40

Parallel Port Output ................................................................... 44

User-Configurable, Built-In Self-Test (BIST)......................... 48

Chip Synchronization................................................................ 48

Serial Port Control ..................................................................... 49

Microport .................................................................................... 58

Memory Map .................................................................................. 60

Reading the Memory Map Table.............................................. 60

Global Register Map .................................................................. 62

Input Port Register Map ............................................................ 65

Channel Register Map ............................................................... 68

Output Port Register Map ......................................................... 73

Design Notes ................................................................................... 77

Outline Dimensions ....................................................................... 79

Ordering Guide .......................................................................... 79

AD6636

Rev. A | Page 3 of 80

REVISION HISTORY

6/05—Rev. 0 to Rev. A

Changes to Format............................................................. Universal

Changes to Figure 1...........................................................................1

Changes to Applications...................................................................1

Changes to General Description.....................................................4

Changes to Table 3 ............................................................................7

Changes to Table 5 ............................................................................9

Changes to Table 8 ..........................................................................11

Changes to Figure 17 ......................................................................18

Changes to Figure 18 and Figure 19 .............................................19

Changes to Figure 25 ......................................................................23

Changes to Mean Power Mode (Control Bits 01) Section.........24

Changes to NCO Frequency Section............................................27

Changes to Figure 30 ......................................................................28

Changes to 6-Tap Fixed Coefficient Filter (FIR2) Section ........32

Changes to Decimate-by-2, Half-Band Filter (HB2) Section....32

Changes to Table 17 ........................................................................32

Changes to Clock Rate Section......................................................34

Changes to Programming DRCF Register for a Symmetric

Filter Section ...................................................................................35

Changes to Channel RAM Coefficient Filter (CRCF)

Section ..............................................................................................36

Changes to Programming CRCF Register for a Symmetrical

Filter Section ....................................................................................37

Changes to Desired Signal Level Mode Section..........................41

Changes to Figure 41 ......................................................................45

Changes to Figure 42 and Figure 43 .............................................46

Changes to Start with Soft Sync Section ......................................48

Changes to Hop with Soft Sync Section.......................................49

Changes to Hop with Pin Sync Section........................................49

Replaced Serial Control Port Section ...........................................49

Changes to Intel (INM) Mode Section.........................................58

Changes to Motorola (MNM) Mode Section..............................59

Changes to Table 30 ........................................................................61

Changes to Channel Register Map Section .................................68

Changes to AGC Control Register <10:0> Section ....................71

Changes to BIST Control <15:0> Section....................................73

Changes to Parallel Port Output Control <23:0> .......................73

Changes to Table 44 ........................................................................74

Changes to Design Notes ...............................................................77

Changes to Figure 59 ......................................................................77

8/04—Revision 0: Initial Version

AD6636

Rev. A | Page 4 of 80

GENERAL DESCRIPTION

The AD6636 is a digital downconverter intended for IF

sampling or oversampled baseband radios requiring wide

bandwidth input signals. The AD6636 has been optimized for

the demanding filtering requirements of wideband standards,

such as CDMA2000, UMTS, and TD-SCDMA, but is flexible

enough to support wider standards such as WiMAX. The

AD6636 is designed for radio systems that use either an IF

sampling ADC or a baseband sampling ADC.

The AD6636 channels have the following signal processing

stages: a frequency translator, a fifth-order cascaded integrated

comb filter, two sets of cascaded fixed-coefficient FIR and half-

band filters, three cascaded programmable coefficient sum-of-

product FIR filters, an interpolating half-band filter (IHB), and

a digital automatic gain control (AGC) block. Multiple modes

are supported for clocking data into and out of the chip and

provide flexibility for interfacing to a wide variety of digitizers.

Programming and control are accomplished via serial or

microport interfaces.

Input ports can take input data at up to 150 MSPS. Up to

300 MSPS input data can be supported using two input ports

(some external interface logic is required) and two internal

channels processing in tandem. Biphase filtering in the output

data router is selected to complete the combined filtering mode.

The four input ports can operate in CMOS mode, or two ports

can be combined for LVDS input mode. The maximum input

data rate for each input port is 150 MHz.

Frequency translation is accomplished with a 32-bit complex

numerically controlled oscillator (NCO). It has greater than

110 dBc SFDR. This stage translates either a real or complex

input signal from intermediate frequency (IF) to a baseband

complex digital output. Phase and amplitude dither can be

enabled on-chip to improve spurious performance of the NCO.

A 16-bit phase-offset word is available to create a known phase

relationship between multiple AD6636 chips or channels. The

NCO can also be bypassed so that baseband I and Q inputs can

be provided directly from baseband sampling ADCs through

input ports.

Following frequency translation is a fifth-order CIC filter with a

programmable decimation between 1 and 32. This filter is used

to lower the sample rate efficiently, while providing sufficient

alias rejection at frequencies with higher frequency offsets from

the signal of interest.

Following the CIC5 are two sets of filters. Each set has a non-

decimating FIR filter and a decimate-by-2 half-band filter. The

FIR1 filter provides about 30 dB of rejection, while the HB1

filter provides about 77 dB of rejection. They can be used

together to achieve a 107 dB stop band alias rejection, or they

can be individually bypassed to save power. The FIR2 filter

provides about 30 dB of rejection, while the HB2 filter provides

about 65 dB of rejection. The filters can be used either together

to achieve more than 95 dB stop band alias rejection, or can be

individually bypassed to save power. FIR1 and HB1 filters can

run with a maximum input rate of 150 MSPS. In contrast, FIR2

and HB2 can run with a maximum input rate of 75 MSPS (input

rate to FIR2 and HB2 filters).

The programmable filtering is divided into three cascaded RAM

coefficient filters (RCFs) for flexible and power efficient

filtering. The first filter in the cascade is the MRCF, consisting

of a programmable nondecimating FIR. It is followed by

programmable FIR filters (DRCF) with decimation from 1 to

16. They can be used either together to provide high rejection

filters, or independently to save power. The maximum input

rate to the MRCF is one-fourth of the PLL clock rate.

The channel RCF (CRCF) is the last programmable FIR filter

with programmable decimation from 1 to 16. It typically is used

to meet the spectral mask requirements for the air standard of

interest. This could be an RRC, antialiasing filter or any other

real data filter. Decimation in preceding blocks is used to keep

the input rate of this stage as low as possible for the best filter

performance.

The last filter stage in the chain is an interpolate-by-2 half-band

filter, which is used to up-sample the CRCF output to produce

higher output oversampling. Signal rejection requirements for

this stage are relaxed because preceding filters have filtered the

blockers and adjacent carriers already.

Each input port of the AD6636 has its own clock used for

latching onto the input data, but the Input Port A clock (CLKA)

is also used as the input for an on-board PLL clock multiplier.

The output of the PLL clock is used for processing all filters and

processing blocks beyond the data router following the CIC

filter. The PLL clock can be programmed to have a maximum

clock rate of 200 MHz.

A data routing block (DR) is used to distribute data from the

CICs to the various channel filters. This block allows multiple

back-end filter chains to work together to process high

bandwidth signals or to make even sharper filter transitions

than a single channel can perform. It can also allow complex

filtering operations to be achieved in the programmable filters.

The digital AGC provides the user with scaled digital outputs

based on the rms level of the signal present at the output of the

digital filters. The user can set the requested level and time

constant of the AGC loop for optimum performance of the

postprocessor. This is a critical function in the base station for

CDMA applications where the power level must be well

controlled going into the RAKE receivers. It has programmable

clipping and rounding control to provide different output

resolutions.

AD6636

Rev. A | Page 5 of 80

The overall filter response for the AD6636 is the composite of

all the combined filter stages. Each successive filter stage is

capable of narrower transition bandwidths but requires a

greater number of CLK cycles to calculate the output. More

decimation in the first filter stage minimizes overall power

consumption. Data from the device is interfaced to a

DSP/FPGA/baseband processor via either high speed parallel

ports (preferred) or a DSP-compatible microprocessor interface.

The AD6636 is available both in 4-channel and 6-channel

versions. The data sheet primarily discusses the 6-channel part.

The only difference between the 6-channel and 4-channel

devices is that Channel 4 and Channel 5 are not available on the

4-channel version, (see

Figure 1). The 4-channel device still has

the same input ports, output ports, and memory map. The

memory map section for Channel 4 and Channel 5 can be

programmed and read back, but it serves no purpose.

PRODUCT HIGHLIGHTS

• Six independent digital filtering channels

• 101 dB SNR noise performance, 110 dB spurious

performance

• Four input ports capable of 150 MSPS input data rates

• RMS/peak power monitoring of input ports and 96 dB

range AGCs before the output ports

• Three programmable RAM coefficient filters, three half-

band filters, two fixed coefficient filters, and one fifth-

order CIC filter per channel

• Complex filtering and biphase filtering (300 MSPS ADC

input) by combining filtering capability of multiple

channels

• Three 16-bit parallel output ports operating at up to a

200 MHz clock

• Blackfin®-compatible and TigerSHARC®-compatible 16-bit

microprocessor port

• Synchronous serial communications port is compatible

with most serial interface standards, SPORT, SPI, and SSR

剩余79页未读,继续阅读

资源评论

yeeryy

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 包装设计公司黑色简洁风格的模板下载.zip

- 宝宝类企业蓝色风格的模板下载.rar

- 包装设计公司白色简洁的模板下载.rar

- 保护地球的环保企业网站模板下载.zip

- 保洁公司蓝色宽屏的网站模板html下载.rar

- 北大青鸟总部招生官网全站模板.rar

- 背景动画简洁大气常用后台登录版面.zip

- 背景简洁的企业博客网站模板下载.rar

- 北欧宜家风的建材家居官网商城网站模板下载.zip

- 背景自动变换炫酷的后台登录网页模板下载.zip

- 背景切换搞怪的个性万圣节网站模板下载.zip

- 背景切换的网站改版临时网站模板下载.zip

- 毕业生网上报到系统蓝色前台模板.zip

- 毕业学习资讯绿色风格的模板下载.rar

- 背景自动切换的网站倒计时模板下载.zip

- 边角简洁效果的企业网站模板下载.zip

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功