基于FPGA的数字锁相环的设计.pdf

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

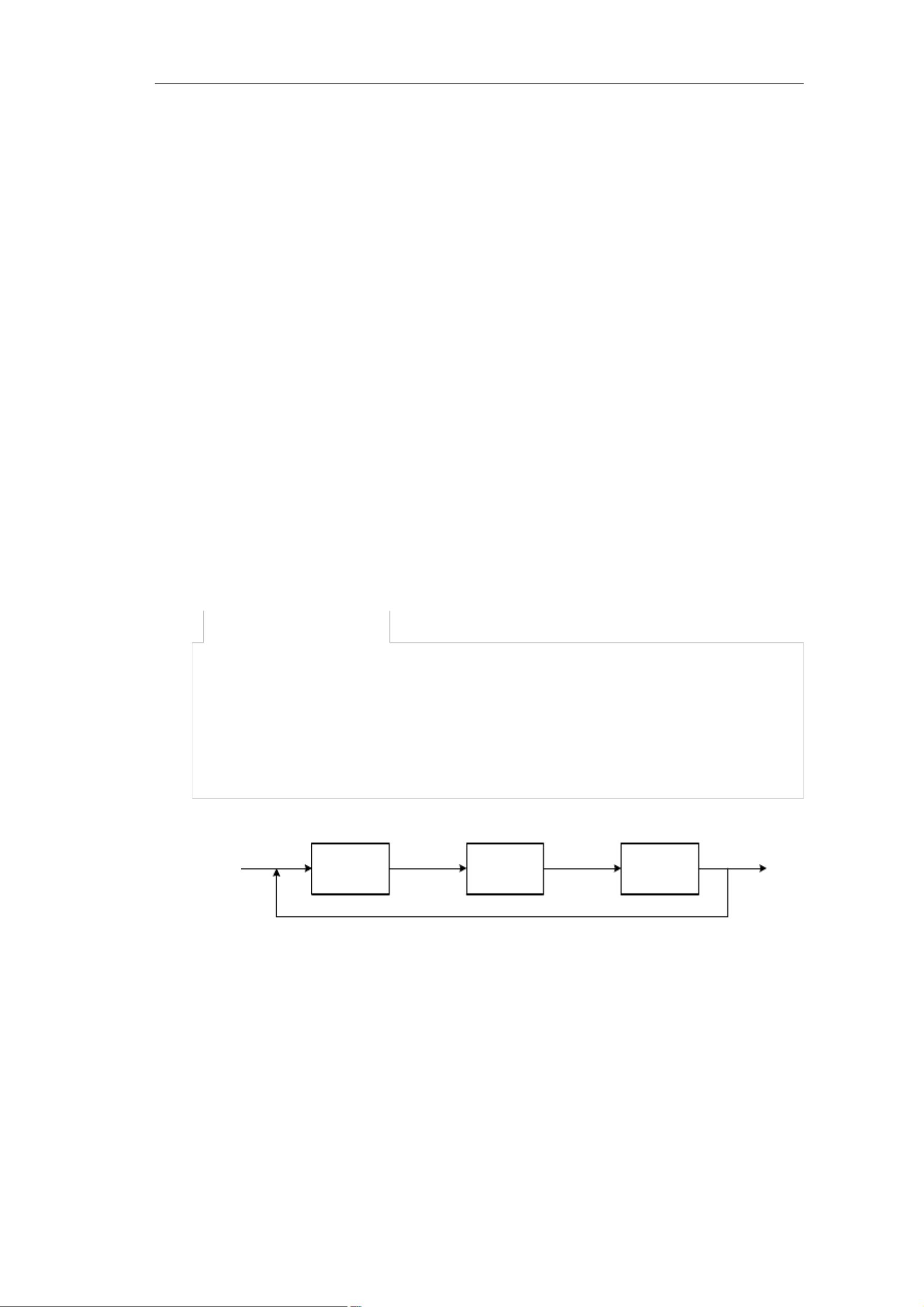

《基于FPGA的数字锁相环的设计》 第一章 绪论 锁相环技术自诞生以来,一直在通信、计算和信号处理等领域发挥着至关重要的作用。随着科技的进步,尤其是半导体技术的发展,全数字锁相环(Digital Phase-Locked Loop, DPLL)逐渐成为研究热点。全数字锁相环相比模拟锁相环具有更高的精度、更宽的频率范围和更好的可编程性,因此在现代通信系统中得到广泛应用。本课题的研究旨在深入理解锁相环的工作原理,并通过FPGA(Field-Programmable Gate Array)实现一个高效的数字锁相环,以满足高速、高精度的时钟同步需求。 第二章 FPGA的设计基础 FPGA是现代电子设计中的一种关键器件,它允许设计者通过硬件描述语言(如Verilog HDL)进行定制化逻辑设计。Verilog HDL是一种强大的工具,可以用来描述数字电路的逻辑行为。FPGA的设计流程包括逻辑设计、综合、布局布线以及最终的配置。设计者首先使用Verilog编写模块化的硬件描述代码,然后通过综合工具将高级语言转换为门级逻辑,接着在FPGA芯片上进行布局布线,最后将生成的配置文件下载到FPGA,实现电路功能。 第三章 锁相环的原理 全数字锁相环的基本结构通常包含数字鉴相器、K变模可逆计数器、脉冲加减器和N分频器等核心组件。数字鉴相器用于比较输入参考信号与环路内的振荡信号之间的相位差,产生误差信号;K变模可逆计数器根据误差信号调整环路的频率,实现相位锁定;脉冲加减器控制计数器的增减,保证相位调整的精确性;N分频器则根据特定的分频因子,将振荡器产生的高频信号转换为所需的较低频率。 第四章 数字锁相环的设计 基于FPGA的数字锁相环设计需要考虑各个组件的优化。数字鉴相器设计中,可以采用比较器或计数器结构,以提高相位检测的灵敏度。K变模可逆计数器需能快速响应误差信号,确保相位跟踪的实时性。脉冲加减器设计要求低延迟和低功耗,以提高整体系统的性能。N分频器则需要灵活的分频系数设置,以适应不同应用场景。 第五章 实验仿真与调试 在设计完成后,通过软件仿真验证数字锁相环的功能性和稳定性至关重要。使用诸如ModelSim或Vivado等工具进行逻辑仿真,检查各模块在各种条件下的行为。随后,将设计在实际FPGA硬件上进行系统实验,验证其在真实环境中的性能,包括锁相环的锁定时间、相位噪声和频率稳定度等关键指标。 总结,本论文详尽地探讨了基于FPGA的数字锁相环设计,从理论基础到具体实现,再到实验验证,全面展示了这一技术在互联网领域的应用潜力。通过深入理解和优化设计,我们可以构建出更高效、可靠的数字锁相环系统,为高速数据传输和通信系统提供坚实的支撑。

剩余26页未读,继续阅读

- 粉丝: 6756

- 资源: 3万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 柯尼卡美能达Bizhub C266打印机驱动下载

- java游戏之我当皇帝那些年.zip开发资料

- 基于Matlab的汉明码(Hamming Code)纠错传输以及交织编码(Interleaved coding)仿真.zip

- 中国省级新质生产力发展指数数据(任宇新版本)2010-2023年.txt

- 基于Matlab的2Q-FSK移频键控通信系统仿真.zip

- 使用C++实现的常见算法

- travel-web-springboot【程序员VIP专用】.zip

- 基于Matlab, ConvergeCase中部分2D结果文件输出至EXCEL中 能力有限,代码和功能极其简陋.zip

- java桌面小程序,主要为游戏.zip学习资源

- Java桌面-坦克大战小游戏.zip程序资源

信息提交成功

信息提交成功