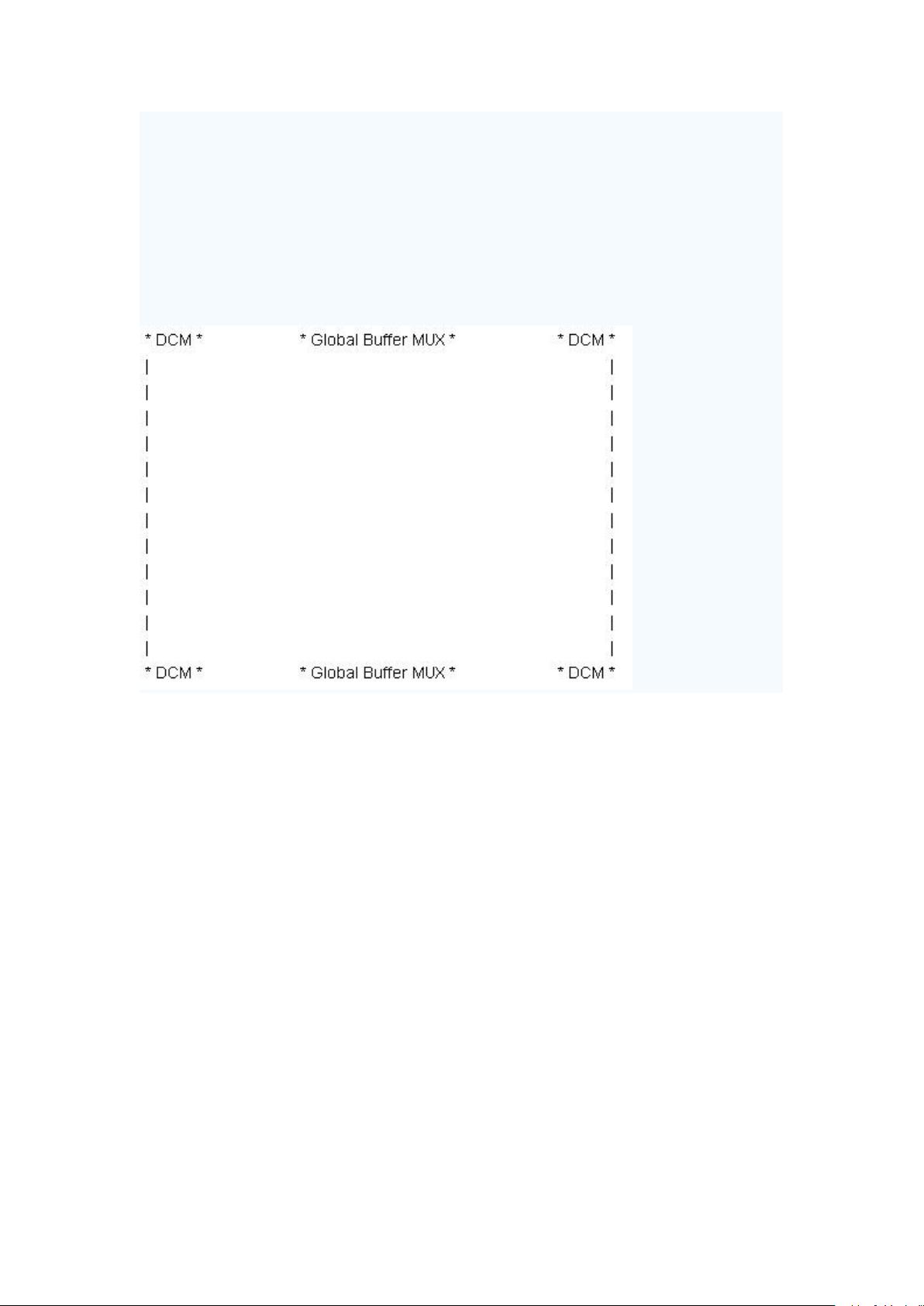

### DCM使用详解 #### 一、DCM概述 DCM(Digital Clock Manager,数字时钟管理器)是一种用于FPGA(Field Programmable Gate Array,现场可编程门阵列)中的时钟管理技术,主要用于处理时钟信号的各种复杂需求。在本篇文档中,我们将深入探讨DCM的主要功能、特点及其在Spartan-3系列FPGA中的应用。 #### 二、DCM主要功能 1. **分频与倍频**:DCM能够将输入时钟进行乘法或除法操作,从而生成新的输出时钟。这对于需要多种频率信号的应用非常有用。 2. **消除Skew**:Skew是指由于传输路径不同导致同一时钟信号到达不同目的地的时间差异。DCM可以通过内部的延迟补偿机制来减少这种时间差异,提高系统的时序性能。 3. **相位移动**:DCM还支持对输入时钟信号进行相位移动,通常是时钟周期的一个分数,这在多相时钟系统中非常有用。 4. **全局时钟分配**:DCM与FPGA内部的全局时钟分配网络紧密结合,能够高效地将时钟信号分发到整个芯片的不同部分。 5. **电平转换**:通过DCM可以输出不同电平标准的时钟信号,以适应不同的电路需求。 #### 三、DCM的特点与能力 以Spartan-3系列FPGA为例,DCM具有以下特点: 1. **数量**:每个FPGA包含4个DCM,足以满足大多数设计的需求。 2. **数字频率综合器输入**:CLKIN的频率范围为1-280MHz,可以满足大多数应用场景下的频率需求。 3. **延迟锁相环输入**:CLKIN的频率范围为18-280MHz,适合更高频率的应用场景。 4. **时钟输入源**:DCM可以接收来自全局缓冲输入垫、全局缓冲输出、通用I/O(无Skew)、内部逻辑(无Skew)等多种来源的时钟信号。 5. **频率综合器输出**:CLKFX和CLKFX180是CLKIN的M/D倍,其中M和D的范围分别为2-32和1-32,这使得用户可以根据需求灵活配置输出频率。 6. **时钟分频输出**:CLKDV提供一系列分频选项,包括1.5、2、2.5、3等,最大支持16分频,支持半分频。 7. **倍频输出**:CLK2X和CLK2X180分别提供CLKIN的两倍频率输出,适用于需要较高频率的应用场景。 8. **时钟条件化与占空比调整**:所有输出时钟均经过条件化处理,并保持50%的占空比,确保时钟信号的质量。 9. **相位移动输出**:支持1/4周期和半周期的相位移动输出,提供精确的相位控制。 10. **相移精度**:最高可达时钟周期的1/256,确保了高精度的相位调整能力。 11. **时钟输出**:每个DCM可以提供最多9个时钟输出,这些输出可以连接到全局时钟网络、通用互连或是输出脚,其中最多4个可以接入全局时钟网络。 #### 四、DCM的位置与布局 在Spartan-3系列FPGA中,DCM通常位于芯片的四个角上,以便于它们的输出可以直接连接到全局时钟缓冲区的入口。这样的布局有助于减少信号传输延迟,提高整体时序性能。 #### 五、DCM作为全局时钟网络的一部分 通常情况下,时钟信号通过全局输入缓冲区(IBUFG)和全局时钟缓冲区(BUFG)进入全局时钟网络。但在需要时,DCM也可以成为全局时钟网络的一部分,以进一步优化时钟信号的分发。 #### 六、DCM内部结构解析 1. **DLL(Delay Locked Loop,延迟锁定环)**:主要用于消除输入时钟与输出时钟之间的延迟,使得输入输出时钟之间保持一致。DLL的核心功能是实现零延迟。 2. **DFS(Digital Frequency Synthesizer,数字频率合成器)**:利用CLKIN合成新的频率,通过M和D的组合实现各种倍频和分频操作。DFS不使用DLL时,输出频率与输入频率之间可能不存在相位关系,因为没有进行延迟补偿。 3. **PS(Phase Shift,相位偏移)**:DCM支持对所有9个输出信号进行相位偏移,偏移量通常是CLKIN的一个分数,也可以在运行过程中进行动态调整,以满足更高级的应用需求。 DCM在FPGA设计中扮演着极其重要的角色,它不仅可以提供高度定制化的时钟信号,还能有效改善系统的时序性能。通过对DCM的深入了解和合理应用,设计师可以构建出更为高效和可靠的电子系统。

剩余7页未读,继续阅读

- 粉丝: 0

- 资源: 3

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功