TLS810D1EJ V50 英飞凌芯片 INFINEON 中文版规格书手册.pdf

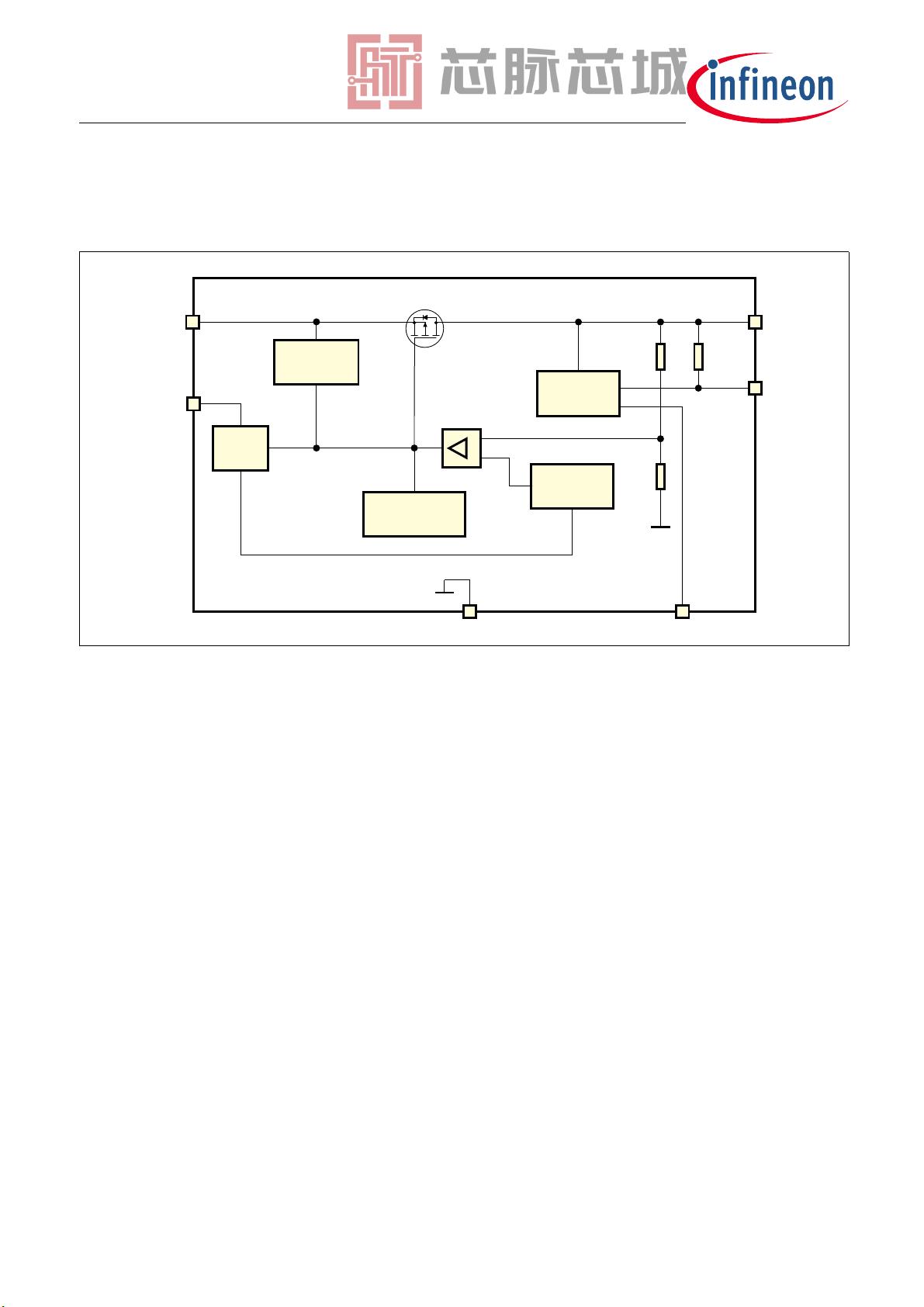

在当今汽车电子系统的发展中,对电源管理的需求日益增长,英飞凌科技推出的TLS810D1EJ V50超低静态电流线性电压调节器为汽车电子领域提供了一个高效且可靠的电源管理解决方案。这款芯片集成了多项尖端技术,不仅具备超低静态电流、宽输入电压范围、低 dropout 电压及高输出电流能力等特点,还提供高精度输出电压,能够满足汽车启动期间对电源管理的要求。 TLS810D1EJ V50的核心优势在于其极低的静态电流仅为9微安,这意味着即便在没有负载的情况下,芯片也能以极低的电流消耗运行,极大提升了能效。此外,宽广的输入电压范围从2.75伏延伸至42伏,这一设计不仅考虑了正常工作电压,还考虑到了汽车启动时电池电压可能降至极低的情况,确保在极端条件下也能稳定供电。 芯片的低 dropout 电压特性允许其在输入与输出电压之间仅保持很小的压差时即可正常工作,典型值为200毫伏在100毫安负载时。这种特性对于汽车电子系统来说极为重要,因为在某些场景下,电池电压波动较大,低 dropout 性能可确保系统在较宽的输入电压范围内稳定运行。同时,高达100毫安的输出电流能力,意味着它能够支持众多需要较大电流的应用。 除了其出色的性能外,TLS810D1EJ V50也特别注重电源管理的效率。在关闭模式下,芯片的电流消耗可以降低至小于1微安,这一功能对于需要频繁开关电源的应用场景尤其重要,能够进一步减少能量消耗。 这款芯片还提供了两种封装选项,PG-DSO-8 EP和PG-TSON-10,分别标记为810D1V50,以适应不同的安装空间和可靠性要求。两种封装都设计紧凑、可靠,满足汽车应用对空间有限的需求。 内置的输出电流限制保护功能是TLS810D1EJ V50的又一亮点。这种保护功能能够有效防止输出短路到地或过流等问题,保障设备的即时安全。而过温关断保护功能,则进一步增强了芯片的安全防护,使得设备在过热情况下能够自动关闭,避免潜在损坏。 芯片还提供了启用功能,使用户可以灵活控制芯片的工作状态,例如在芯片处于关闭状态时,其电流消耗极低,从而确保了设备的低功耗运行。这一特性对于需要长时间处于待机状态的汽车电子系统来说,尤为重要。 TLS810D1EJ/LDV50的固定5伏输出版本,输出电压精度可达2%,使其非常适合为需要精确电压的汽车电子系统供电。芯片能够在2.75伏的输入电压下就开始跟踪调节,这一特点进一步扩展了其工作范围,确保即使在汽车启动期间,也能保证电压的稳定输出。 符合绿色产品标准,遵循RoHS指令,并通过了AEC-Q100认证的TLS810D1EJ V50,展现出英飞凌对产品质量和环境责任的重视。这意味着这款芯片不仅满足了汽车电子行业的严格质量和可靠性标准,也符合了全球环保要求,对制造商和最终用户均提供质量保障。 TLS810D1EJ V50超低静态电流线性电压调节器以其卓越的性能参数、精巧的封装设计、安全的保护机制以及对环境的友好性,成为汽车电子系统中电源管理的理想选择。它不仅能提供稳定高效的电源,还能为设计工程师提供更大的设计灵活性,减少系统故障的可能,提升整个系统的性能和可靠性。无论是在传统燃油车还是电动汽车中,TLS810D1EJ V50都能找到广泛的应用场景,成为汽车电子电源管理不可或缺的一环。

剩余30页未读,继续阅读

- 粉丝: 4

- 资源: 4030

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 4b065校园朋友圈_springboot+vue0.zip

- 4b071郑州旅游景点智能推荐系统_springboot+vue0.zip

- 工作流管理与技术报告+Eclipse+Activiti+MySQL+关键代码+实现效果图

- SpringBoot+thymeleaf 请假系统(源码+MySQL文件)

- 页面精美的在线网址导航源码站长在线工具箱引流导航页源码HTML源码

- 4b074高校实验室预约系统_springboot+vue0.zip

- c代码记录日志,Python代码分析日志

- 多场comsol数值模拟耦合案例-多孔离散裂缝介质二氧化碳驱油,包含裂缝建模方法,对应案例的网格剖分介绍

- 4b076酒店点餐管理系统_springboot+vue0.zip

- 4b072中文社区交流平台_springboot+vue0.zip

- 4b079扶贫众筹网_springboot+vue0.zip

- 4b081高校素拓分管理系统_springboot+vue0.zip

- 4b078基于JavaWeb的宠物商城平台_springboot+vue0.zip

- 龙门坐标桁架机械手sw20全套技术资料100%好用.zip

- Web开发基础:HTML/CSS/JavaScript实现简易计算器

- 4b085基于java的大学生就业信息管理系统_springboot+vue0.zip

信息提交成功

信息提交成功