没有合适的资源?快使用搜索试试~ 我知道了~

DS1339U-33+T&R ADI芯片 电子元器件中文版规格手册.pdf

需积分: 5 3 下载量 196 浏览量

2023-06-02

11:09:56

上传

评论

收藏 273KB PDF 举报

温馨提示

试读

21页

DS1339U-33+T&R ADI芯片 电子元器件中文版规格手册

资源推荐

资源详情

资源评论

GENERAL DESCRIPTION

The DS1339 serial real-time clock (RTC) is a low-

power clock/date device with two programmable time-

of-day alarms and a programmable square-wave

output. Address and data are transferred serially

through an I

2

C bus. The clock/date provides seconds,

minutes, hours, day, date, month, and year

information. The date at the end of the month is

automatically adjusted for months with fewer than 31

days, including corrections for leap year. The clock

operates in either the 24-hour or 12-hour format with

AM/PM indicator. The DS1339 has a built-in power-

sense circuit that detects power failures and

automatically switches to the backup supply,

maintaining time, date, and alarm operation.

APPLICATIONS

Handhelds (GPS, POS Terminals)

Consumer Electronics (Set-Top Box, Digital

Recording, Network Appliance)

Office Equipment (Fax/Printers, Copier)

Medical (Glucometer, Medicine Dispenser)

Telecommunications (Routers, Switches, Servers)

Other (Utility Meter, Vending Machine, Thermostat,

Modem

)

Pin Configurations appear at end of data sheet.

BENEFITS AND FEATURES

Completely Manages All Timekeeping

Functions

o Real-Time Clock Counts Seconds,

Minutes, Hours, Date of the Month,

Month, Day of the Week, and Year

with Leap-Year Compensation Valid

Up to 2100

o Two Time-of-Day Alarms

o Programmable Square-Wave Output

o Oscillator Stop Flag

Interfaces to Most Microcontrollers

o I

2

C Serial Interface

Low-Power Operation Extends Battery

Backup Run Time

o Automatic Power-Fail Detect and

Switch Circuitry

o Trickle-Charge Capability

Underwriters Laboratories® (UL)

Recognized

Surface-Mount Package with an

Integrated Crystal (DS1339C Saves

Additional Space and Simplifies Design

ORDERING INFORMATION

PART

TEMP RANGE

VOLTAGE (V)

PIN-PACKAGE

TOP MARK†

DS1339C-2#

-40°C to +85°C

2.0

16 SO (300 mils)

DS1339C-2

DS1339C-3#

-40°C to +85°C

3.0

16 SO (300 mils)

DS1339C-3

DS1339C-33#

-40°C to +85°C

3.3

16 SO (300 mils)

DS1339C-33

DS1339U-2+

-40°C to +85°C

2.0

8 µSOP

1339 rr-2

DS1339U-3+

-40°C to +85°C

3.0

8 µSOP

1339 rr-3

DS1339U-33+

-40°C to +85°C

3.3

8 µSOP

1339 rr-33

+Denotes a lead(Pb)-free/RoHS-compliant package.

#Denotes a RoHS-compliant device that may include lead that is exempt under the RoHS requirements. The lead finish is JESD97 category

e3, and is compatible with both lead-based and lead-free soldering processes.

†A “+” anywhere on the top mark indicates a lead(Pb)-free device. A “#” denotes a RoHS-compliant device. rr = second line, revision code

DS1339

I

2

C Serial Real-Time Clock

19-5770; Rev 3/15

1 of 20

DS1339 I

2

C Serial Real-Time Clock

ABSOLUTE MAXIMUM RATINGS

Voltage Range on Any Pin Relative to Ground………………………………………………………………-0.3V to +6.0V

Operating Temperature Range (Noncondensing)………………………………………………………….-40°C to +85°C

Storage Temperature Range………………………………………………………………………………..-55°C to +125°C

Lead Temperature (soldering, 10s)...…………………………………………………………………………………+260°C

Soldering Temperature (reflow).……………………………………………………………………………………….+260°C

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only,

and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is

not implied. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.

PACKAGE THERMAL CHARACTERISTICS (Note 1)

µSOP

Junction-to-Ambient Thermal Resistance (θ

JA

).…………………...……………………………………….206.3°C/W

Junction-to-Case Thermal Resistance (θ

JC

)……………………………………………………………………42°C/W

SO

Junction-to-Ambient Thermal Resistance (θ

JA

).……………………………………………………………….73°C/W

Junction-to-Case Thermal Resistance (θ

JC

)……………………………………………………………………23°C/W

Note 1:

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer

board. For detailed information on package thermal considerations, refer to

www.maxim-ic.com/thermal-tutorial

.

RECOMMENDED DC OPERATING CONDITIONS

(T

A

= -40°C to +85°C) (Note 2)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Supply Voltage V

CC

DS1339-2

1.8

2.0

5.5

V

DS1339-3 2.7 3.0 5.5

DS1339-33 2.97 3.3 5.5

Backup Supply Voltage V

BACKUP

1.3 3.0 3.7 V

Logic 1 V

IH

0.7 x

V

CC

V

CC

+

0.3

V

Logic 0 V

IL

-0.3

+0.3 x

V

CC

V

Power-Fail Voltage V

PF

DS1339-2 1.58 1.70 1.80

V DS1339-3 2.45 2.59 2.70

DS1339-33 2.70 2.85 2.97

2 of 20

DS1339 I

2

C Serial Real-Time Clock

DC ELECTRICAL CHARACTERISTICS

(V

CC

= MIN to MAX, T

A

= -40°C to +85°C.) (Note 2)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Input Leakage I

LI

(Note 3) 1

µA

I/O Leakage I

LO

(Note 4) 1

µA

Logic 0 Out

V

OL

= 0.4V; V

CC

> V

CC

MIN (-3, -33);

V

CC

≥ 2.0V (-2)

I

OL

(Note 4) 3 mA

Logic 0 Out

V

OL

= 0.2 (V

CC

);

1.8V < V

CC

< 2.0V (DS1339-2)

I

OL

(Note 4) 3 mA

Logic 0 Out

V

OL

= 0.2 (V

CC

);

1.3V < V

CC

< 1.8V (DS1339-2)

I

OL

(Note 4) 250

µA

V

CC

Active Current I

CCA

(Note 5) 450

µA

V

CC

Standby Current (Note 6) I

CCS

-2: V

CC

= 2.2V 60 100

µA

-3: V

CC

= 3.3V 80 150

-33: V

CC

= 5.5V 200

Trickle-Charger Resistor Register

10h = A5h, V

CC

= Typ, V

BACKUP

= 0V

R1 (Note 7) 250

Ω

Trickle-Charger Resistor Register

10h = A6h, V

CC

= Typ, V

BACKUP

= 0V

R2 2000

Ω

Trickle-Charger Resistor Register

10h = A7h, V

CC

= Typ, V

BACKUP

= 0V

R3 4000

Ω

V

BACKUP

Leakage Current I

BKLKG

25 100 nA

DC ELECTRICAL CHARACTERISTICS

(V

CC

= 0V, T

A

= -40°C to +85°C.) (Note 2)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

V

BACKUP

Current EOSC = 0, SQW Off

I

BKOSC

(Note 8) 400 700 nA

V

BACKUP

Current EOSC = 0, SQW On

I

BKSQW

(Note 8) 600 1000 nA

V

BACKUP

Current EOSC = 1

I

BKDR

10 100 nA

3 of 20

DS1339 I

2

C Serial Real-Time Clock

AC ELECTRICAL CHARACTERISTICS

(V

CC

= MIN to MAX, T

A

= -40°C to +85°C.) (Note 9)

PARAMETER SYMBOL CONDITION MIN TYP MAX UNITS

SCL Clock Frequency f

SCL

Fast mode 100 400

kHz

Standard mode 100

Bus Free Time Between a STOP

and START Condition

t

BUF

Fast mode 1.3

µs

Standard mode 4.7

Hold Time (Repeated) START

Condition (Note 10)

t

HD:STA

Fast mode 0.6

µs

Standard mode 4.0

LOW Period of SCL Clock t

LOW

Fast mode 1.3

µs

Standard mode 4.7

HIGH Period of SCL Clock t

HIGH

Fast mode 0.6

µs

Standard mode 4.0

Setup Time for a Repeated

START Condition

t

SU:STA

Fast mode 0.6

µs

Standard mode 4.7

Data Hold Time (Notes 11, 12) t

HD:DAT

Fast mode 0 0.9

µs

Standard mode 0

Data Setup Time (Note 13) t

SU:DAT

Fast mode 100

ns

Standard mode 250

Rise Time of Both SDA and SCL

Signals (Note 14)

t

R

Fast mode 20 + 0.1C

B

300

ns

Standard mode 20 + 0.1C

B

1000

Fall Time of Both SDA and SCL

Signals (Note 14)

t

F

Fast mode 20 + 0.1C

B

300

ns

Standard mode 20 + 0.1C

B

300

Setup Time for STOP Condition t

SU:STO

Fast mode 0.6

µs

Standard mode 4.0

Capacitive Load for Each Bus

Line (Note 14)

C

B

400 pF

I/O Capacitance (SDA, SCL) C

I/O

(Note 9) 10 pF

Oscillator Stop Flag (OSF) Delay t

OSF

(Note 15) 100 ms

4 of 20

DS1339 I

2

C Serial Real-Time Clock

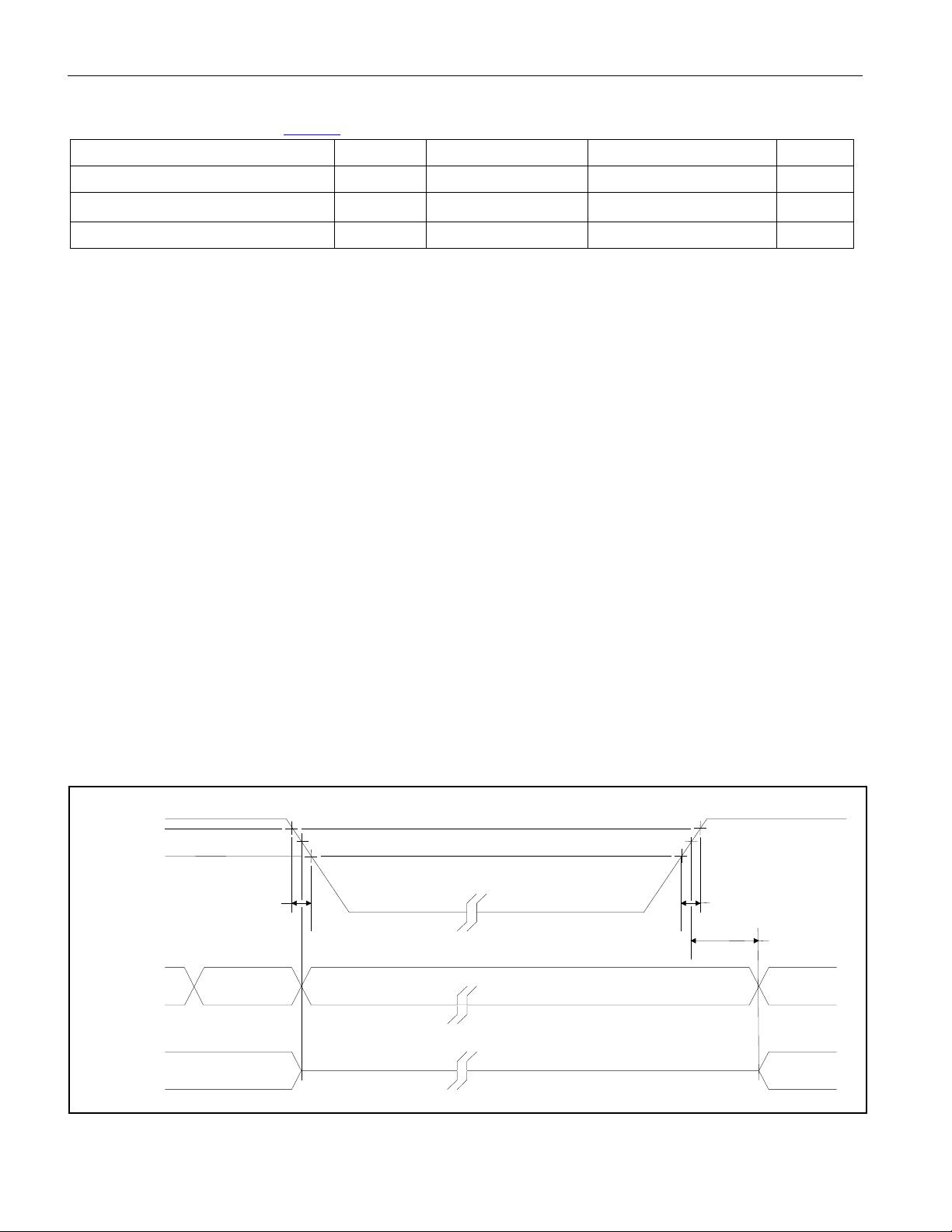

POWER-UP/DOWN CHARACTERISTICS

(T

A

= -40°C to +85°C) (Note 2, Figure 1)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Recovery at Power-Up t

REC

(Note 16) 2 ms

V

CC

Fall Time; V

PF(MAX)

to V

PF(MIN)

t

VCCF

300

µs

V

CC

Rise Time; V

PF(MIN)

to V

PF(MAX)

t

VCCR

0

µs

WARNING: Under no circumstances are negative undershoots, of any amplitude, allowed when device is in

battery-backup mode.

Note 2:

Limits at -40°C are guaranteed by design and are not production tested.

Note 3:

SCL only.

Note 4:

SDA and SQW/INT.

Note 5:

I

CCA

—SCL at f

SC

max, V

IL

= 0.0V, V

IH

= V

CC

, trickle charger disabled.

Note 6:

Specified with the I

2

C bus inactive, V

IL

= 0.0V, V

IH

= V

CC

, trickle charger disabled.

Note 7:

V

CC

must be less than 3.63V if the 250

Ω

resistor is selected.

Note 8:

Using recommended crystal on X1 and X2.

Note 9:

Guaranteed by design; not production tested.

Note 10:

After this period, the first clock pulse is generated.

Note 11:

A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the V

IHMIN

of the SCL signal) to bridge

the undefined region of the falling edge of SCL.

Note 12:

The maximum t

HD:DAT

need only be met if the device does not stretch the LOW period (t

LOW

) of the SCL signal.

Note 13:

A fast-mode device can be used in a standard-mode system, but the requirement t

SU:DAT

≥ to 250ns must then be met. This is

automatically the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW

period of the SCL signal, it must output the next data bit to the SDA line t

R(MAX)

+

t

SU:DAT

= 1000 + 250 = 1250ns before the SCL line

is released.

Note 14:

C

B

—total capacitance of one bus line in pF.

Note 15:

The parameter t

OSF

is the period of time the oscillator must be stopped for the OSF flag to be set over the voltage range of 0.0V ≤

V

CC

≤

V

CCMAX

and 1.3V

≤

V

BACKUP

≤

3.7V.

Note 16:

This delay applies only if the oscillator is running. If the oscillator is disabled or stopped, no power-up delay occurs.

Figure 1. Power-Up/Down Timing

OUTPUTS

V

CC

V

PF(MAX)

V

PF(MIN)

INPUTS

HIGH-Z

DON'T CARE

VALID

RECOGNIZED

RECOGNIZED

VALID

t

VCCF

t

VCCR

t

REC

5 of 20

剩余20页未读,继续阅读

资源评论

芯脉芯城

- 粉丝: 3

- 资源: 4031

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功