没有合适的资源?快使用搜索试试~ 我知道了~

RapidIO_Bring-Up_Procedure_on_PowerQUICC_III

需积分: 7 0 下载量 87 浏览量

2018-10-18

13:12:45

上传

评论

收藏 1.01MB PDF 举报

温馨提示

RapidIO_Bring-Up_Procedure_on_PowerQUICC_III,The MPC8540 and MPC8560 PowerQUICC III™ processors have an 8-bit parallel RapidIO interface. This document provides guidance in the basic use of this interface; detailing the setup of local and remote processors starting with basic verification and discovery, then describing booting over RapidIO and conducting simple memory tests

资源推荐

资源详情

资源评论

© Freescale Semiconductor, Inc., 2004. All rights reserved.

Freescale Semiconductor

The MPC8540 and MPC8560 PowerQUICC III™ processors

have an 8-bit parallel RapidIO interface. This document provides

guidance in the basic use of this interface; detailing the setup of

local and remote processors starting with basic verification and

discovery, then describing booting over RapidIO and conducting

simple memory tests.

Most of the guidance in this document applies to any RapidIO

enabled PowerQUICC III system. However, the concepts are

illustrated by a few specific examples.

1 Introduction

This document is designed to provide assistance to engineers

wishing to use the RapidIO interface on the MPC8540 and

MPC8560 PowerQUICC III processors. It summarizes some basic

aspects of the RapidIO specification, and the use of the RapidIO

interfaces on these processors. It also details a basic procedure to

bring up simple RapidIO systems; including the setup of the local

processor, simplified discovery, booting over RapidIO, and the

execution of simple memory reads/writes to the remote

processors.

Section 2, “Background Information,” provides background

information regarding the RapidIO specifications, the

implementation and usage of the RapidIO interface on the

MPC8540/60, and information regarding the example systems,

which are used to illustrate the steps of the procedure outlined in

Section 3, “Bring-up Procedure.”

AN2753

Rev. 1, 11/2004

Contents

1.Introduction 1

1.1. Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2

2.Background Information 3

2.1. RapidIO. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3

2.2. Using RapidIO on MPC8540 and MPC8560 . . . . . . .6

2.3. Example Target Hardware . . . . . . . . . . . . . . . . . . . . .8

3.Bring-up Procedure 11

3.1. Configure the Local Processor . . . . . . . . . . . . . . . . .12

3.2. Discover Other Devices in the System. . . . . . . . . . .20

3.3. Enable Access to Remote Configuration Space . . . .27

3.4. Boot over RapidIO . . . . . . . . . . . . . . . . . . . . . . . . . .30

3.5. Enable Memory Reads and Writes . . . . . . . . . . . . . .36

4.Output from Example Application 41

4.1. Point-to-Point Example. . . . . . . . . . . . . . . . . . . . . . .41

4.2. Fabric Example. . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

5.References 54

6.Revision History 54

Appendix A. Notes on Maintenance Transactions . . . . . . .55

RapidIO Bring-Up Procedure on

PowerQUICC III™

by Lorraine McLuckie and Colin Cureton

NCSD Platforms, East Kilbride

RapidIO Bring-Up Procedure on PowerQUICC III™, Rev. 1

2 Freescale Semiconductor

Introduction

Section 3, “Bring-up Procedure,” describes a procedure for bringing up a basic MPC8540/60-based RapidIO

system. Both point-to-point and fabric-based systems are considered.

Section 4 provides example output from an application that follows the procedure outlined in Section 3, “Bring-up

Procedure,” executed on the example hardware systems described in Section 2, “Background Information.”

Appendix A contains additional information about maintenance transactions, paying particular attention to

the calculation of the maintenance offset used

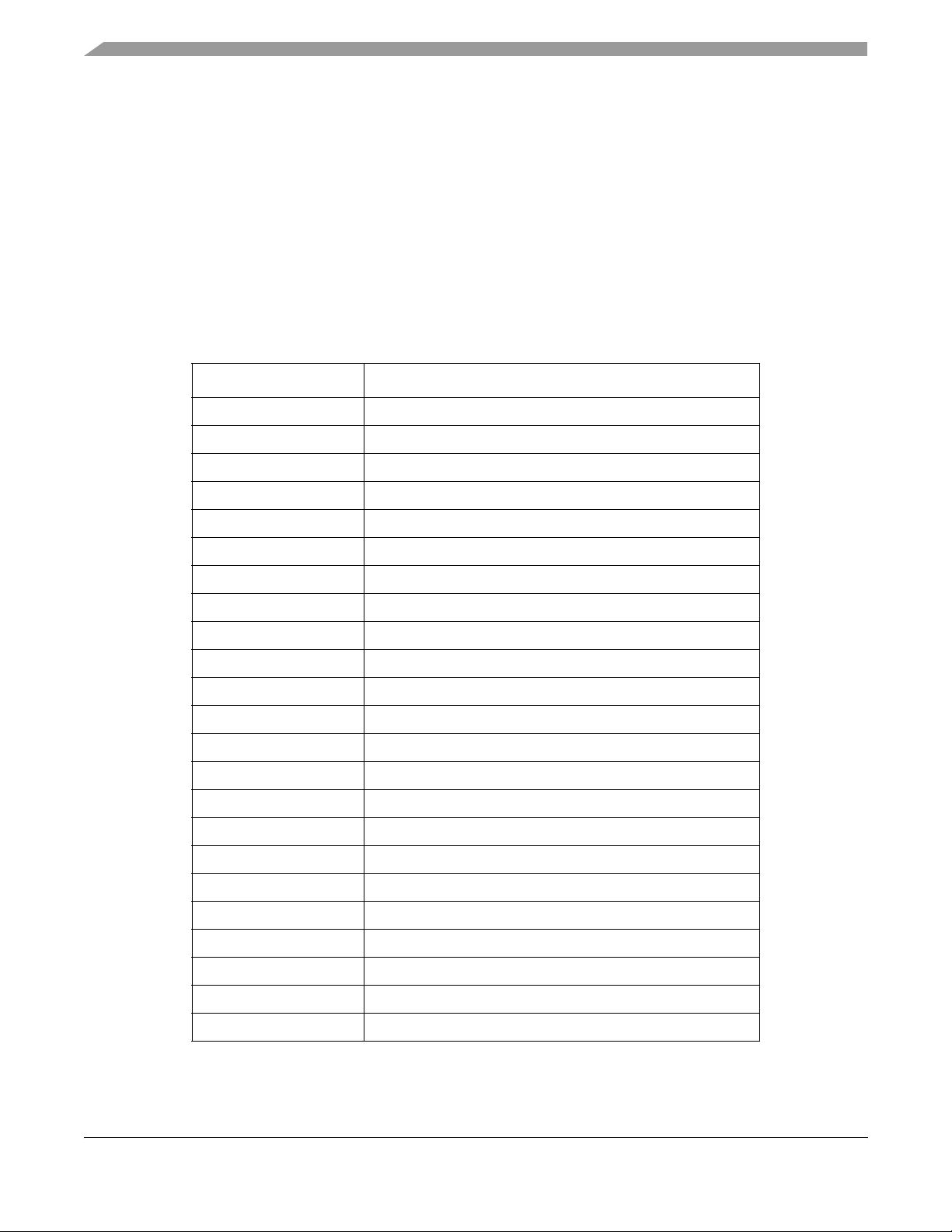

1.1 Glossary

The following acronyms and terms are used throughout this application note.

Table 1. Glossary of Terms

Term Description

ATMU Address translation and mapping unit

BAR Base address register

CAR Capability attribute register

CCSR Configuration, control and status registers

CCSRBAR CCSR base address register

CSR Capability status register

DDR SDRAM Double data rate SDRAM

DIDCAR Device identity capability register

DMA Direct memory access

EEPROM Electrically erasable programmable read only memory

HBDIDLCSR Host base device lock ID CSR

I/O Input/Output

JTAG Joint test access group

LAW Local area window

LP-LVDS Link protocol, low voltage differential signaling

MAS MMU assist register

MMU Memory management unit

PowerQUICC III MPC85xx networking and communications processor

R/W Read/Write

RIO RapidIO

RIW RapidIO inbound window

ROW RapidIO outbound window

SBTG Software bring-up technical group

RapidIO Bring-Up Procedure on PowerQUICC III™, Rev. 1

Freescale Semiconductor 3

Background Information

2 Background Information

This section provides background information relevant to the bring-up procedure. Section 2.1, “RapidIO,” provides

a summary of the relevant aspects of the RapidIO specification. Section 2.2, “Using RapidIO on MPC8540 and

MPC8560,” describes the implementation of RapidIO on MPC8540/60 and considerations for its use. Section 2.3,

“Example Target Hardware,” provides information regarding the example systems which will be used to illustrate

the procedure.

2.1 RapidIO

The RapidIO interconnect architecture is a high-performance packet-switched interconnect technology. It addresses

the high-performance embedded industry's need for reliability, increased bandwidth, and faster bus speeds in an

intra-system interconnect. The RapidIO interconnect allows chip-to-chip and board-to-board communications at

performance levels scaling to 10 Gigabits per second and beyond.

This section summarizes some basic information about the RapidIO specification. Additional information can be

found in the RapidIO Interconnect Specification.

1

2.1.1 RapidIO Layers

The RapidIO specification is written in a layered manner, to ensure flexibility and that changes to one layer do not

necessarily affect other layers.

The layers of the RapidIO architecture are as follows:

• Logical layer—Defines the overall protocol and packet formats, the types of transaction that can be carried

out with RapidIO and how addressing is handled.

• Transport layer—Provides the necessary route information for a packet to move from one point to another.

• Physical layer—Contains the device level interface such as packet transport mechanisms, flow control,

electrical characteristics, and low level error management.

The logical layer is split into two categories depending on the system model in use. The first part is the input/output

logical specification which defines the basic system architecture of RapidIO. The other is the message passing

logical specification which enables distributed I/O processing. This note concentrates on the input/output logical

specification.

2.1.2 Processing Element Models

There are several types of devices that can be used on a RapidIO based system. This note describes only two device

model types: the integrated processor-memory processing element and the switch processing element.

SDRAM Synchronous dynamic random access memory

TLB Translation lookaside buffer

Table 1. Glossary of Terms (continued)

Term Description

RapidIO Bring-Up Procedure on PowerQUICC III™, Rev. 1

4 Freescale Semiconductor

Background Information

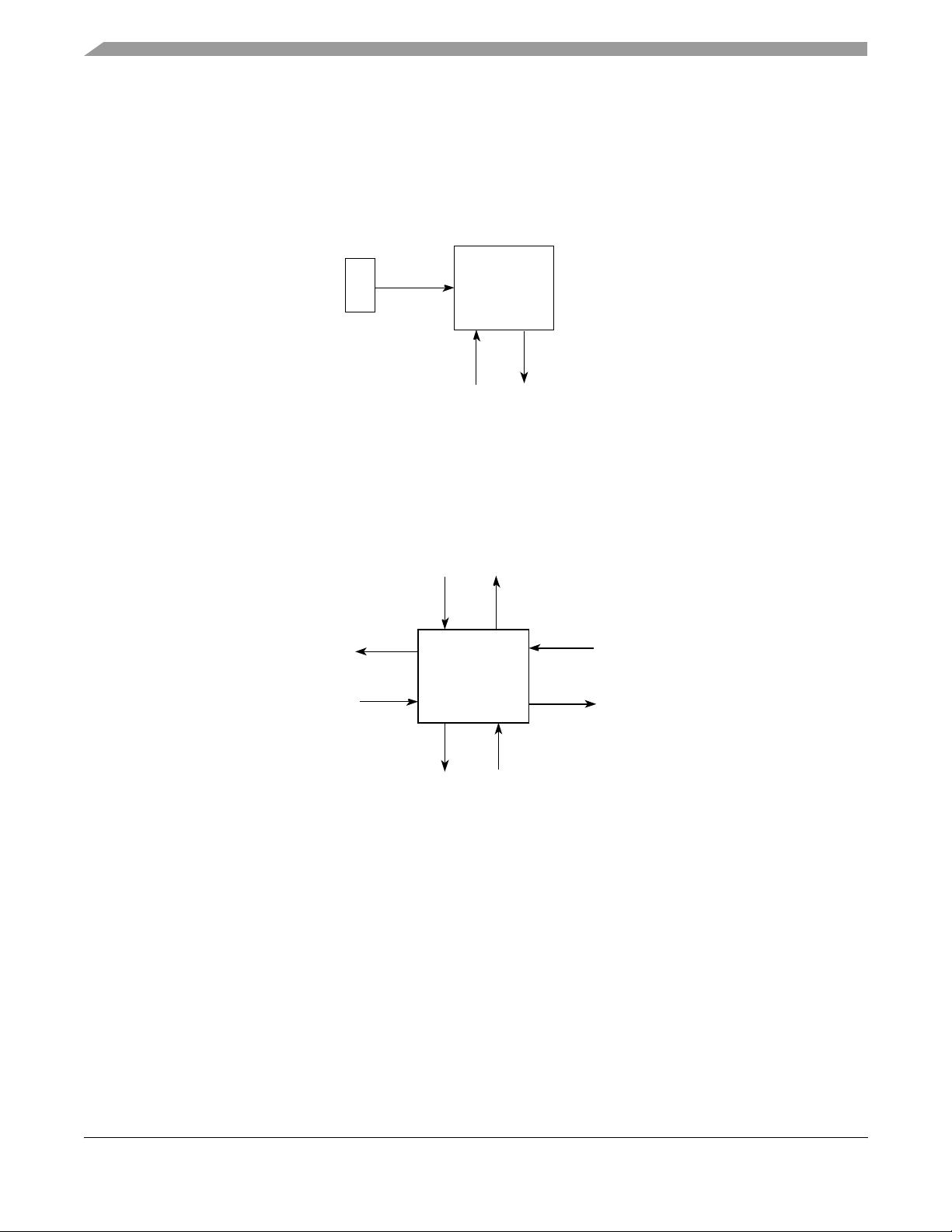

2.1.2.1 Integrated Processor-Memory Processing Element

One form of the processor-memory processing element is a fully integrated component that is designed to connect

to a RapidIO interconnect system as shown in

Figure 1. This type of device integrates a memory system and other

support logic with a processor core on the same piece of silicon, or within the same package, and is one example of

a RapidIO end-point. In this note the processing element is an MPC8540/60 device.

Figure 1. Integrated Processor-Memory Processing Element

2.1.2.2 Switch Processing Element

A switch processing element is a device that allows communication with other processing elements through a

switch. A switch may be used to connect a variety of RapidIO compliant processing elements. Behavior of the

switches, and the interconnect fabric in general, is addressed in the RapidIO Common Transport Specification.

1

In

this note the switch processing element used is the Tundra Tsi500™ 4-port switch.

3

Figure 2. Switch Processing Element Model

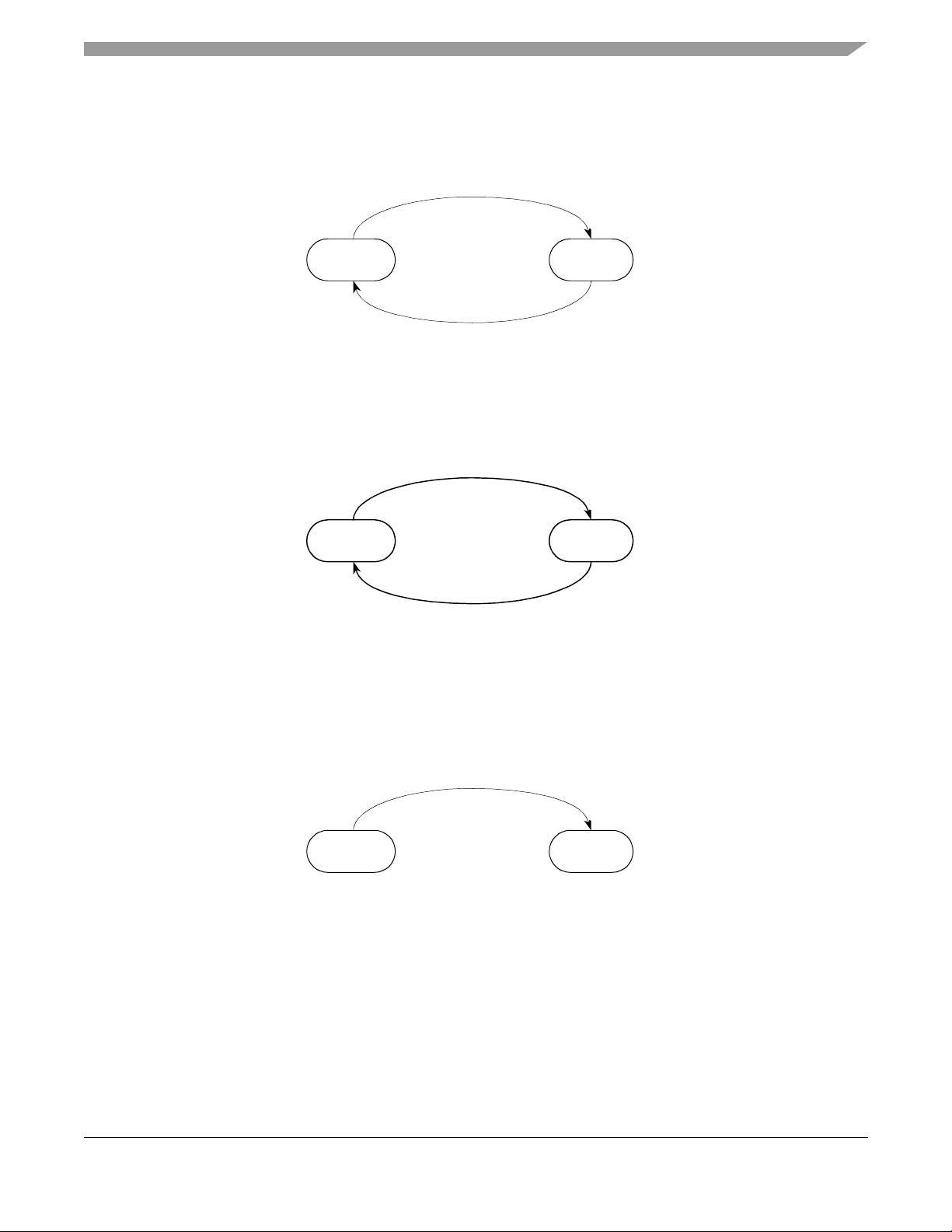

2.1.2.3 RapidIO Transactions

In the logical layer, RapidIO defines a broad range of transaction types, ranging from simple transactions to access

an agent device’s memory space, to user defined and implementation dependent transactions. Throughout this note,

three different classes of request transactions and their associated responses are used, where a request is a transaction

that is issued by a processing element to accomplish some activity on a remote processing element. The three

transactions that are used in this note are detailed below. These sections detail the logical layer aspects of these

transaction; no consideration is given to the transport or physical layer interactions.

2.1.2.3.1 Maintenance Transaction

A maintenance transaction is a special system support request. It is used by a processing element to read or write

data to capability attribute registers (CARs) and capability status registers (CSRs), defined in the RapidIO

Processor

Memory

RapidIO Based

System Interconnect

Switch

RapidIO Bring-Up Procedure on PowerQUICC III™, Rev. 1

Freescale Semiconductor 5

Background Information

specification.

1

Maintenance requests do not contain addresses, but use a maintenance offset into the CAR/CSR

block to specify which register is to be read or written.

Maintenance transactions are used for system initialization and discovery and for altering system configuration.

Figure 3. Maintenance Transaction

2.1.2.3.2 NREAD Transactions

A read transaction, consisting of the NREAD and RESPONSE transactions, is used by a processing element to read

data from a specified address. The data is returned in a response packet and is of the size requested.

Figure 4. NREAD Transaction

2.1.2.3.3 NWRITE/NWRITE_R Transactions

The write transaction is used by a processing element to write data to a specified address. The write transaction can

take several forms including NWRITE and NWRITE_R.

The NWRITE request allows data writes, with no expected response.

Figure 5. NWRITE Transaction

1. Maintenance Request

DestinationRequestor

2. Maintenance Response

DestinationRequestor

1. NREAD

2. Response, data

DestinationRequestor

1. NWRITE, data

剩余59页未读,继续阅读

资源评论

Gavin2099

- 粉丝: 11

- 资源: 12

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- C++和Qt基于数据库Mysql学生信息管理系统源码+数据库+实验报告

- MSE学习案例demo

- DuMediaCrashInfo

- 飞塔防火墙fortigate7.4.5 vm虚拟镜像下载

- Python毕业设计-学生信息管理系统的设计与实现django框架(源码+数据库)

- 2024-2025学年第一学期MySQL数据库期中考试题(含答案)

- Java及大数据求职面试指南.zip

- VBA 数据n行转M列【一行的每n列为1行】.xlsm

- 《顶刊复现》(复现程度90%),Reinforcement Learning-Based Fixed-Time Trajectory Tracking Control for Uncertain Ro

- Nestjs + TypeORM + MySQL + Jwt + Docker实现基本的一对一,多对多,一对多的数据库表连接,数据库链表查询,接口crud,分页查询,jwt鉴权,密码加密处理的.zip

- 1735786960511.jpg

- Amesim燃料电池电堆模型搭建 一共8个视频,包括:氢气系统建模,空气系统建模和热管理建模 有段视频无声,其余都有声音讲解

- NSFW implement in pytorch(色情图&性感图识别,本程序经过了线上大数据集测试,性能优异效果良好).zip

- 各个项目代码及其验证环境

- 基于java的大学生选修选课系统的的设计和实现.docx

- 基于java的“有光”摄影分享网站系统的设计和实现.docx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功