没有合适的资源?快使用搜索试试~ 我知道了~

英特尔IXP2400网络处理器中文手册

温馨提示

系统讲述了IXP2400网络处理器的硬件结构,近年来人们对CPU的要求越来越高,网络处理器的出现无疑为提高CPU性能作出了贡献

资源推荐

资源详情

资源评论

IXP2400 网络处理器简介

IXA 是用于 Internet 数据交换设备的处理器系统结构,它使得 Internet 设备由传统的固定协

议、低效率走向具有软件升级功能的高效率可编程设备。IXP2400 是 IXA 系统结构的一个具体

处理器产品。其外部特性如图 1 所示。

图 1 .Intel IXP2400 网络处理器外部特性

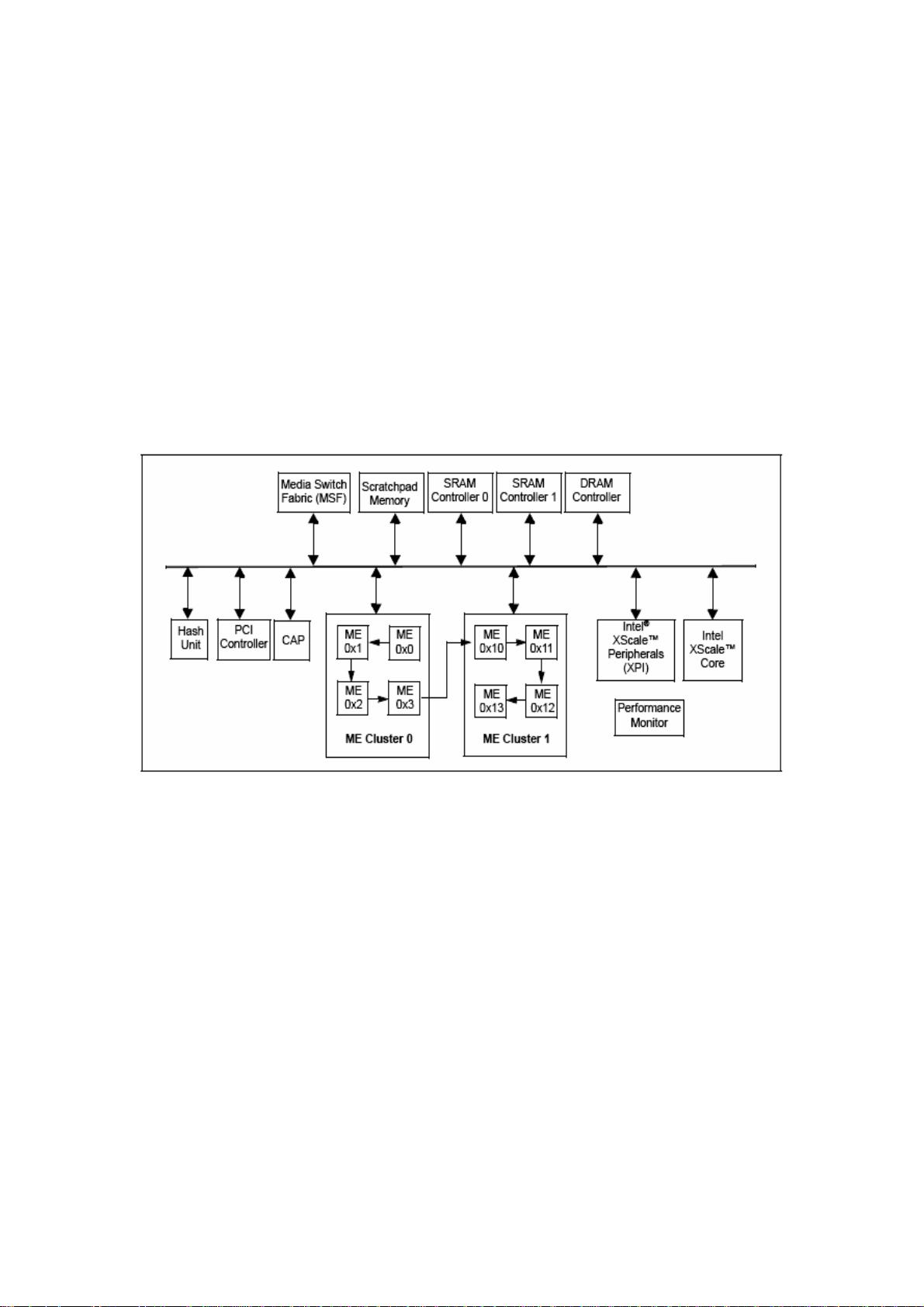

IXP2400 网络处理器是 Intel 公司继 IXP1200 之后推出的又一基于 IXA 体系结构的网络处理

器, 其系统模块结构如图 2 所示。它采用 600MHz 的 XScale 核心处理器取代 IXP1200 的

StrongARM,并配有 8 个第二版的微引擎,每个微引擎支持 8 个硬件实现的线程和多级的存储器

系统结构,支持校验功能,采用 MSF 接口取代原来的 FBI,两个 QDR SRAM 通道。IXP2400 网

络处理器通过提供编程环境高度灵活性、代码的可重用性和高性能的处理机制实现了更快的网络

服务智能处理。它支持各种各样的 WAN 和 LAN 应用。通过改进微引擎的系统结构达到高性能

和可扩展性,这些改进包括多线程的分配和使软件具有流水特性的高速缓存系统结构。这些特性

使得 IXP2400 网络处理器的性能比前一代 IXP1200 的性能更加优化,功能更加强大,每秒可进

行 5. 4G 次操作,并与 IXP1200 相兼容。

1. Intel XScale 核心处理器

Intel XScale 核心处理器是一个通用 32 位 RISC(Reduced Instruction Set Computer)处理器,

与 ARM 的结构相兼容。Intel XScale 核心处理器初始化并管理芯片,而且能够完成高层网络处理

任务。其特性主要为:高性能,低消耗,32 位内嵌 RISC 处理器;32K 字节指令高速缓冲器和

32K 数据高速缓冲器;2K 字节微数据高速缓冲器,使传输数据处理便捷;可有 4 个并发的读请

求,保证不延迟处理器;新的指令集合;性能监测特性;支持 JTAG。

Intel XScale 核心是基于 ARM V5TE 的高性能、低消耗的微处理器。它广泛融入了达到高性

能的系统结构的特性。同时在其中加入了许多特性来帮助隐藏访存延迟,这也是对高性能处理器

来说非常重要的障碍。这些特性包括:当数据高速缓冲器正从外部存储器取数据时,指令仍能连

续执行的能力;写缓存;多种数据高速缓冲分配策略,并且对于每个应用还可以进行不同的配置;

高速缓冲器加锁。所有这些特性改善了核心与外部存储器总线之间的效率。ARM Version5(V5)

在 ARM Version 4 的基础上增加了浮点指令。

图 2. IXP2400 网络处理器典型模块系统结构

XScale 核心只实现 ARM V5 体系结构的整数指令集,硬件不提供浮点运算指令。与 StrongARM

产品向下兼容性维持了用户模式应用。操作系统可能需要修改以与 Intel XScale 核心的特定硬件

特性相匹配,并充分利用新增的高性能。Intel XScale 核心体系结构特性主要包括:指令高速缓

冲器、数据高速缓冲器、数据 RAM、微数据高速缓冲器、分支目标缓存、存储管理单元(Memory

Management Unit,MMU)、性能监测、电源管理、调试单元、写缓存、MAC 单元和 JTAG 等,

分别介绍如下:

(1)通过对 MAC 单元进行一些体系结构的改进,使 MAC 单元可以支持音频编码算法,

该单元内包含一个 40 位的数字存储器,并支持 16 位的分组数据处理。

(2)存储管理单元提供访问保护和虚拟物理地址解析。为了加速虚拟物理地址解析,Intel

XScale 核心使用了指令快表(TLB)和数据快表来缓存最近解析过的地址。每个快表能够存储

32 个表项并且是全相连的。快表不仅包含解析的地址,而且还包含访问存储器的权限。存储管

理体系结构也为指令高速缓冲和数据存储指定高速缓冲策略。这些策略属性包括:区分是否可高

速缓冲的代码、选择缓冲在微数据缓冲中还是在数据高速缓冲器中、当数据被修改后是采用写回

还是写直达和授权数据写分配策略。当指令快表没有命中的情况下,就会唤醒硬件解析表查询机

制。当解析完成时,物理地址和访问权限以及段页属性就一起被放入快表中。这些解析在快表中

同样是加锁实现的,以保证关键事务的性能。

(3)Intel XScale 核心处理器的指令高速缓存通过减少从外部存取指令的次数来提高性能。

高速缓存提供缓存代码的高速执行。当指令高速缓存有效时,它将请求的指令地址与它当前所包

含的指令地址相比较。如果比较相等则成为“命中”,否则称为“失效”。失效时,高速缓存请

求从外部的存储器中用取指策略取得长为 8 个字(32 个字节)的指令。取到的多条指令存入指

令高速缓存和两个取缓存之一中,同时请求的那条指令被送到指令解码器解释执行。

(4)分支目标缓存(Branch Target Buffer,BTB)存储沿着目标执行过的分支历史。分支

目标缓存拥有当前的指令地址,并且查看这个地址是否是以前见到过的分支地址。分支目标缓存

可以不必由软件显示的管理,在复位之后缺省情况下是无效的,并且当指令高速缓冲无效时它也

是无效的。通过软件置位可使它有效。当执行到分支指令、分支命中或分支当前不在 BTB 当中

时,在分支目标缓存中就会增加一个新的表项。

(5)与指令高速缓存类似,Intel XScale 核心中的数据高速缓存也是通过减少访问外部存储

器的次数来提高新性能的。所不同的是在 Intel XScale 核心中有两种数据高速缓存结构:32K 字

节的数据高速缓存器和 2K 字节的为数据高速缓存器。一个能容纳 8 个表项的写缓冲和 4 个表项

的填充缓冲实现了 Intel XScale 核心指令执行部件与外部存储器访问,这种机制也提高了系统整

体的性能。32K 字节组相联的数据缓存有 32 组,每组又有 32 路;每路有一个称为高速缓存行的

结构,包含 32 字节的数据和一个有效位。每行中还有两位脏数据位。一位代表低十六位,另一

位代表高十六位。当写命中时,相关的位就被置 1,并根据该位的置位情况在替换时采取不同的

替换策略。2K 的组相联微数据缓存有 32 组,每组又有 2 路;其他结构如行结构、替换策略、缓

存操作以及控制都与数据高速缓存类似。

(6)Intel XScale 核心硬件提供 32 位的性能计数器,它可以同时监测两个独立的事件。此

外,Intel XScale 核心实现了 32 位时钟计数器,它能和性能计数器联合使用;他唯一的目的就是

计数核心时钟周期,这些计数周期将用来计算总共执行的时间。Intel XScale 核心可以监控发生

事件和持续事件。监测事件发生时,指定事件每发生一次,计数器就增加一次。如果监测持续事

件,当指定的条件为真时,计数器就记数处理器的时钟数。每个计数器都有自己的中断,当三个

计数器中的任意一个溢出时,就会发出中断请求。当计数器溢出时,它仍然监控事件,直到软件

设置它无效为止。

2. 微引擎(Microengines,MEs)

IXP2400 的微引擎被分为 2 个簇,每个簇有 4 个微引擎,每个簇有一条独立的命令总线和一

条独立的 SRAM 总线,两个簇共享一条 DRAM 总线。每个微引擎有 8 个 32 位为网络处理而专

门设计的可编程引擎;这些微引擎负责处理每个分组的主要数据,支持软件控制的多线程,微引

擎结构如图 3 所示。由于处理器周期时间与外部存储器时间不匹配,一个单一线程的执行经常会

由于等待外部存储器操作的完成而被阻塞。多线程执行时允许线程插入操作,即一个线程准备好

运行,而其他线程则处于阻塞状态,从而使得微引擎的工作效率得以大幅度的提高。

微引擎拥有专门为处理网络数据而开发的指令集。这个指令集包括 50 多条针对比特、字节

或长字的不同的算术运算和逻辑运算指令。在一条指令中,这些操作还能与移位操作相结合。微

引擎拥有整数乘法指令,但没有除法指令或浮点运算指令

其中每个微引擎运行 8 个线程,这些线程之间的转换是无耗时的;每个微引擎有 4K×40 位

指令控制存储器;微引擎配有专门为处理网络数据而开发的增强的指令集合(MEv2);每个微

剩余15页未读,继续阅读

资源评论

yoyo_bright2011-09-28详细全面,权威

yoyo_bright2011-09-28详细全面,权威 kevinyao01262013-05-05系统讲述了IXP2400网络处理器的硬件结构

kevinyao01262013-05-05系统讲述了IXP2400网络处理器的硬件结构

南派七叔

- 粉丝: 41

- 资源: 9

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功