MT7620

PROGRAMMING

GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

PGMT7620_V.1.0_040503

Page 2 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

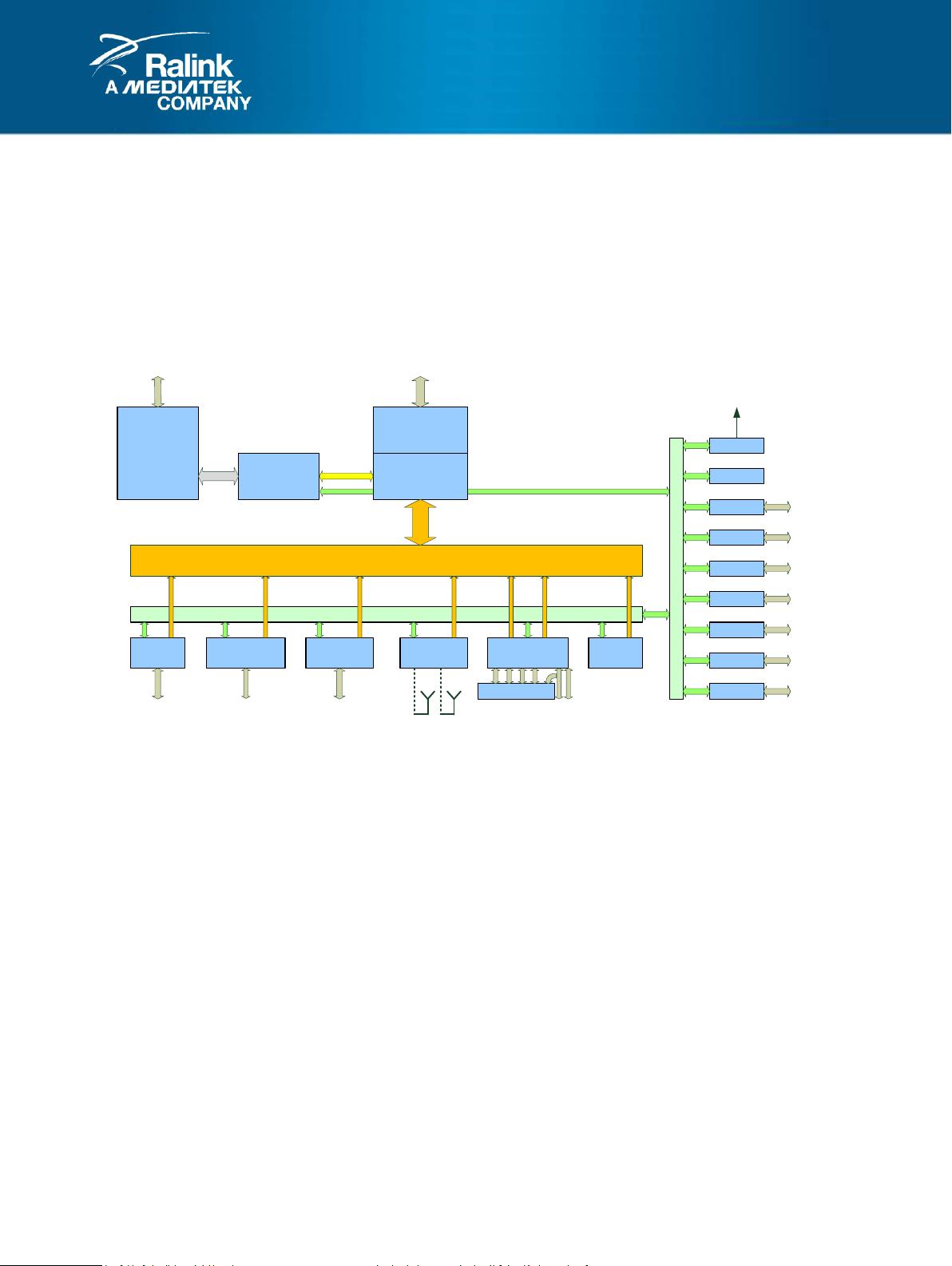

MT7620 Overview

The MT7620 SoC includes a high performance 580 MHz MIPS24KEc CPU core and USB host controller/PHY,

which is designed to enable a multitude of high performance, cost-effective IEEE 802.11n applications with a

MediaTek (Ralink) client card.

Functional Block Diagram

MIPS 24KEc

64 KB I-Cache

32 KB D-

Cache

(580 MHz)

OCP Bridge

OCP

_IF

Arbiter

DRAM

Controller

RBUS (SYS_CLK)

SPI

NFC

PBUS

GDMA

RJ45 x5

Switch

(4FE + 2GE)

5-Port EPHY

RGMII

TMII/MII

x2

PCIe 1.1

PHY

Single-Port

USB 2.0 PHY

Host/

Device

PCIe x1

UART

GPIO

PCM x4

I2S

I2C

I2S

PBUS

INTC

I2C

GPIO

/LED

SPI

NAND

UART

To CPU

interrupt

s

16-Bit

SDR/DDR1/DDR2

EJTAG

WLAN

11n 2x2

2.4 GHz

Timer

PCM

SDHC

SD

Figure 1-1 MT7620 Block Diagram

There are several masters (MIPS 24KEc, USB , PCI Express) in the MT7620 SoC on a high performance, low

latency Rbus, (Ralink Bus). In addition, the MT7620 SoC supports lower speed peripherals such as UART, GPIO,

and SPI via a low speed peripheral bus (Pbus). The SDRAM/DDR1/DDR2 controller is the only bus slave on the

Rbus. It includes an Advanced Memory Scheduler to arbitrate the requests from bus masters, enhancing the

performance of memory access intensive tasks.

PGMT7620_V.1.0_040503

Page 3 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

Table of Contents

1. MIPS 24K PROCESSOR 11

1.1 FEATURES 11

1.2 BLOCK DIAGRAM 12

1.3 MEMORY MAP SUMMARY 13

1.4 CLOCK PLAN 14

1.5 CPU CLOCK MUX 15

2. REGISTERS 16

2.1 NOMENCLATURE 16

2.2 SYSTEM CONTROL 17

2.2.1 FEATURES 17

2.2.2 BLOCK DIAGRAM 17

2.2.3 LIST OF REGISTERS 18

2.2.4 REGISTER DESCRIPTIONS (BASE: 0X1000_0000) 19

2.3 TIMER 46

2.3.1 FEATURES 46

2.3.2 BLOCK DIAGRAM 47

2.3.3 LIST OF REGISTERS 48

2.3.4 REGISTER DESCRIPTIONS (BASE: 0X1000_0100) 49

2.4 INTERRUPT CONTROLLER 53

2.4.1 FEATURES 53

2.4.2 BLOCK DIAGRAM 53

2.4.3 LIST OF REGISTERS 54

2.4.4 REGISTER DESCRIPTIONS (BASE: 0X1000_0200) 55

2.5 SYSTEM TICK COUNTER 60

2.5.1 LIST OF REGISTERS 60

2.5.2 REGISTER DESCRIPTIONS (BASE: 0X1000_0D00) 61

2.6 UART 62

2.6.1 FEATURES 62

2.6.2 BLOCK DIAGRAM 62

2.6.3 LIST OF REGISTERS 63

2.6.4 REGISTER DESCRIPTIONS (BASE: 0X1000_0500) 64

2.7 UART LITE 72

2.7.1 FEATURES 72

2.7.2 BLOCK DIAGRAM 72

2.7.3 LIST OF REGISTERS 73

2.7.4 REGISTER DESCRIPTIONS (BASE: 0X1000_0C00) 74

2.8 PROGRAMMABLE I/O 81

2.8.1 FEATURES 81

2.8.2 BLOCK DIAGRAM 81

2.8.3 LIST OF REGISTERS 82

2.8.4 REGISTER DESCRIPTIONS (BASE: 0X1000_0600) 84

2.9 I

2

C CONTROLLER 97

2.9.1 FEATURES 97

2.9.2 BLOCK DIAGRAM 97

2.9.3 LIST OF REGISTERS 98

PGMT7620_V.1.0_040503

Page 4 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

2.9.4 REGISTER DESCRIPTIONS (BASE: 0X1000_0900) 99

2.10 NAND FLASH CONTROLLER 105

2.10.1 FEATURES 105

2.10.2 NORMAL MODE FLOW 105

2.10.3 ECC 105

2.10.4 LIST OF REGISTERS 108

2.10.5 REGISTER DESCRIPTIONS (BASE: 0X1000_0800) 109

2.11 PCM CONTROLLER 116

2.11.1 FEATURES 116

2.11.2 BLOCK DIAGRAM 116

2.11.3 LIST OF REGISTERS 118

2.11.4 REGISTER DESCRIPTIONS (BASE: 0X1000_2000) 119

2.11.5 PCM CONFIGURATION 130

2.12 GENERIC DMA CONTROLLER 132

2.12.1 FEATURES 132

2.12.2 BLOCK DIAGRAM 132

2.12.3 PERIPHERAL CHANNEL CONNECTION 133

2.12.4 LIST OF REGISTERS 134

2.12.5 REGISTER DESCRIPTIONS (BASE: 0X1000_2800) 135

2.13 SPI CONTROLLER 139

2.13.1 FEATURES 139

2.13.2 BLOCK DIAGRAM 139

2.13.3 LIST OF REGISTERS 140

2.13.4 REGISTER DESCRIPTIONS (BASE: 0X1000_0B00) 141

2.14 I2S CONTROLLER 152

2.14.1 FEATURES 152

2.14.2 BLOCK DIAGRAM 152

2.14.3 I

2

S SIGNAL TIMING FOR I

2

S DATA FORMAT 153

2.14.4 LIST OF REGISTERS 154

2.14.5 REGISTER DESCRIPTIONS (BASE: 0X1000_0A00) 155

2.15 MEMORY CONTROLLER 159

2.15.1 FEATURES 159

2.15.2 BLOCK DIAGRAM 159

2.15.3 SDRAM INITIALIZATION SEQUENCE 159

2.15.4 SDRAM POWER SAVING CONFIGURATION 160

2.15.5 DDR INITIALIZATION SEQUENCE 161

2.15.6 LIST OF REGISTERS 162

2.15.7 REGISTER DESCRIPTIONS (BASE: 0X1000_0300) 163

2.16 RBUS MATRIX AND QOS ARBITER 178

2.16.1 FEATURES 178

2.16.2 BLOCK DIAGRAM 178

2.16.3 LIST OF REGISTERS 179

2.16.4 REGISTER DESCRIPTIONS (BASE: 0X1000_0400) 180

2.17 USB HOST CONTROLLER & PHY 183

2.17.1 FEATURES 183

2.17.2 BLOCK DIAGRAM 183

2.17.3 REGISTER DESCRIPTION (BASE: 0X101C.0000) 183

2.17.4 EHCI OPERATION REGISTERS (BASE: 0X101C.0000) 184

PGMT7620_V.1.0_040503

Page 5 of 523

MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

2.17.5 OHCI OPERATION REGISTERS (BASE: 0X101C.1000) 185

2.18 USB DEVICE CONTROLLER 186

2.18.1 FEATURES 186

2.18.2 BLOCK DIAGRAM 186

2.18.3 BULK OUT 186

2.18.4 LEGACY MODE 187

2.18.5 AGGREGATION MODE 187

2.18.6 DE-AGGREGATION MODE 188

2.18.7 BULK-OUT AGGREGATION FORMAT 189

2.18.8 BULK IN 189

2.18.9 PDMA DESCRIPTOR FORMAT 190

2.18.10 REGISTER DESCRIPTIONS (BASE: 0X1012_0000) 192

2.18.11 USB DEVICE CONTROLLER REGISTERS 192

2.18.12 UDMA REGISTERS 193

2.18.13 PDMA REGISTERS 194

2.19 FRAME ENGINE 202

2.19.1 PSE FEATURES 202

2.19.2 PPE FEATURES 202

2.19.3 PACKET DMA (PDMA) FEATURES 202

2.19.4 BLOCK DIAGRAM 203

2.19.5 PDMA FIFO-LIKE RING CONCEPT 204

2.19.6 PDMA TX DESCRIPTOR FORMAT 205

2.19.7 PDMA RX DESCRIPTOR FORMAT 207

2.19.8 GLOBAL REGISTERS (BASE: 0X1010_0000) 209

2.19.9 CPU PORT REGISTERS (BASE: 0X1010_0400) 216

2.19.10 PDMA REGISTERS (BASE: 0X1010_0800) 223

2.19.11 MIB COUNTER DESCRIPTION (BASE: 0X1010_1000) 235

2.20 ETHERNET SWITCH 237

2.20.1 FEATURES 237

2.20.2 BLOCK DIAGRAM 238

2.20.3 FRAME CLASSFICATION 238

2.20.4 SWITCH L2/L3 ADDRESS TABLE 240

2.20.5 VIRTUAL LAN 244

2.20.6 ACCESS CONTROL LOGIC 247

2.20.7 ARL REGISTERS (BASE: 0X1011_0000) 252

2.20.8 BMU REGISTERS 291

2.20.9 PORT REGISTERS 308

2.20.10 MAC REGISTERS 320

2.20.11 MIB REGISTERS 329

2.20.12 GSW CONFIGURATION REGISTERS 338

2.20.13 MDIO CONTROL 347

2.21 PCI/PCIE CONTROLLER 354

2.21.1 BLOCK DIAGRAM 355

2.21.2 PCIE CONTROLLER ACTING AS A PCIE DEVICE 356

2.21.3 BLOCK DIAGRAM 357

2.21.4 PCI/PCIE MASTER ACCESS IN HOST MODE 358

2.21.5 PCIE CONTROLLER HOST MODE INITIALIZATON EXAMPLE 359

2.21.6 HOST-PCI BRIDGE REGISTERS (BASE: 0X1014_0000) 359

2.21.7 PCIE0 RC CONTROL REGISTERS (BASE: 0X1014_2000) 363

- 1

- 2

- 3

- 4

- 5

- 6

前往页