在电工技术的学习中,第13章主要探讨的是触发器和时序逻辑电路。这部分内容是数字电子技术的基础,尤其对于理解和设计复杂的数字系统至关重要。触发器和时序逻辑电路在计算机硬件、通信设备以及自动化控制等领域都有广泛应用。

我们要了解双稳态触发器,这是构成时序逻辑电路的基本逻辑单元。双稳态触发器具有两个稳定状态,通常用“0”和“1”来表示。这种触发器能够存储一位二进制数据,并在输入信号消失后仍能保持其状态,即具有记忆功能。这一特性使得它们成为构建存储器和计数器等时序逻辑电路的基础。

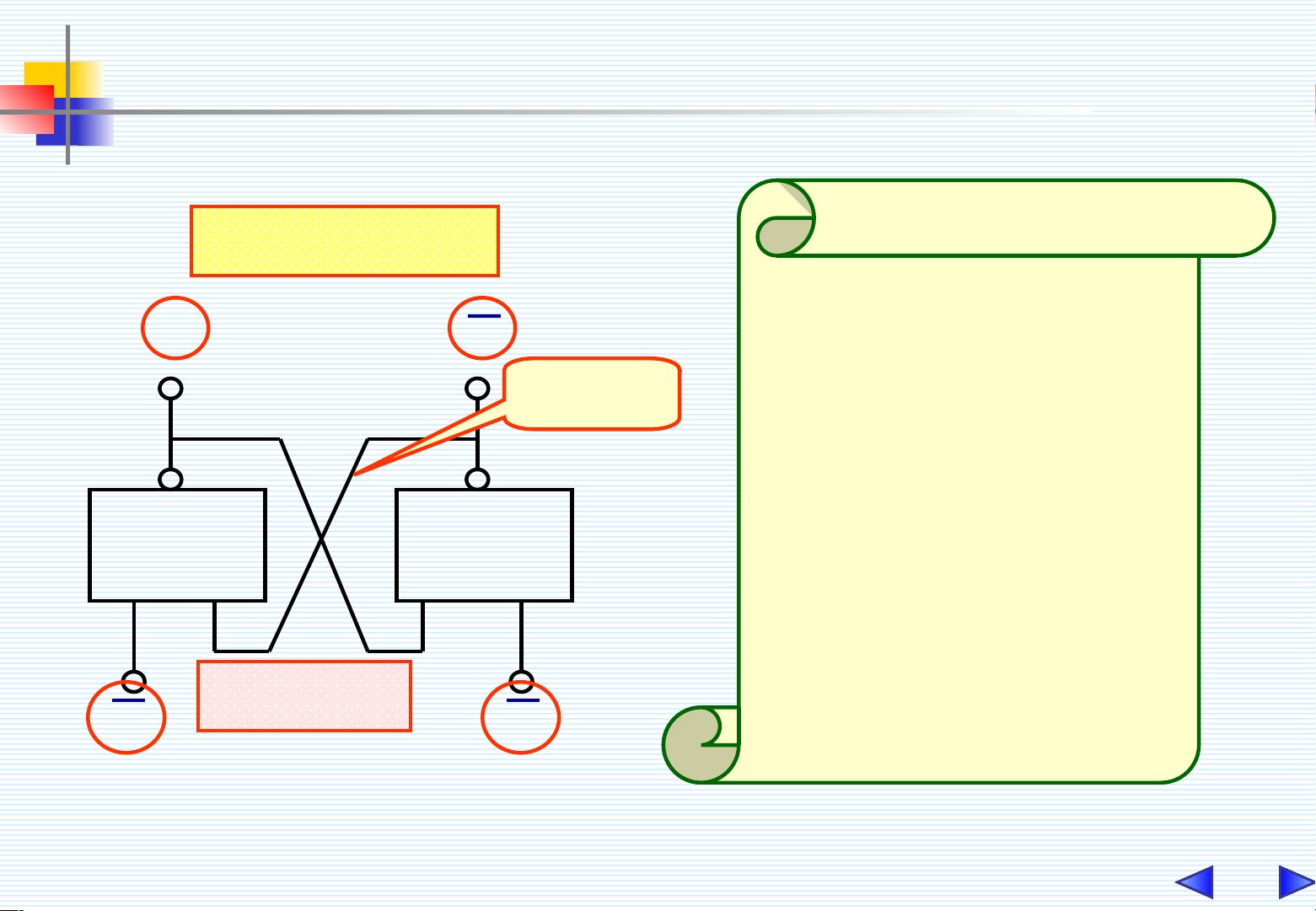

其中,基本的RS触发器是最简单的双稳态触发器类型。RS触发器有两个输入端(S为设置端,R为复位端)和两个互补输出端(Q和Q')。正常工作时,Q和Q'的电平总是相反,用以表示触发器的状态。当S为高电平(1),R为低电平(0)时,触发器被设置为“1”状态;反之,如果R为高电平,S为低电平,则触发器被复位为“0”状态。如果S和R同时为高电平,或者同时为低电平,触发器将进入不确定状态,此时输出既不是“0”也不是“1”,这是应避免的情况。

除了基本的RS触发器,还有其他类型的触发器,如JK触发器、D触发器和T触发器。这些触发器在逻辑功能上更加复杂,可以实现更丰富的操作,例如JK触发器可以设置为置“0”、置“1”或保持原状态,D触发器则是数据的透明传递,T触发器则根据时钟信号翻转其状态。

时序逻辑电路是由这些触发器和其他门电路组成的,它们不仅能够根据输入信号处理信息,还能记忆之前的状态。例如,寄存器用于存储多位二进制数据,移位寄存器可以对数据进行左移或右移操作,而计数器则可以实现二进制或十进制的加法计数。时序逻辑电路的一个关键特点是它们的输出不仅取决于当前的输入,还依赖于电路的先前状态。

学习时序逻辑电路,需要掌握如何分析电路的逻辑功能,理解触发器的工作原理,以及如何利用这些知识去设计和实现各种逻辑系统。在实际应用中,常常会使用到集成电路,例如555定时器,它可以作为脉冲发生器、定时器或振荡器,虽然在本章内容中不是重点,但也是电子工程师必须熟悉的工具。

第13章的电工技术课程将引导学生深入理解数字系统的核心——触发器和时序逻辑电路,为后续更高级的数字设计和分析打下坚实基础。通过学习,学生应能熟练掌握不同类型的触发器,理解时序逻辑电路的特性,并能够分析和设计简单的时序逻辑系统。