没有合适的资源?快使用搜索试试~ 我知道了~

温馨提示

内容概要:本文档为Xilinx公司关于Zynq-7000系列SoC器件的数据手册,详细列出了不同型号(如XC7Z030、XC7Z045等)在多种速度等级下的直流与交流特性规格。涵盖的内容广泛,包括电压范围、温度性能、引脚配置及时序参数。同时提供了针对各种接口(SPI、CAN、UART等)的切换特性和测试条件。最后附有详细的修订历史,记录了每次更新的具体改动事项。 适合人群:从事嵌入式系统设计的技术人员和开发者。 使用场景及目标:用于指导硬件设计与验证阶段对Zynq-7000 SoC器件的选择、评估及测试,确保满足项目需求的同时优化性能表现。 阅读建议:建议读者首先浏览文档概述部分以获得全面的产品认知,再针对具体的应用场景细读相关章节,重点关注所选用芯片的速度等级、电源管理及接口特性。此外,应仔细检查最新的版本更新记录,了解最新修正的细节及其潜在影响。

资源推荐

资源详情

资源评论

DS191 (v1.18) April 12, 2017 www.xilinx.com

Product Specification 1

© Copyright 2012–2017 Xilinx, Inc. Xilinx, the Xilinx logo, Zynq, Virtex, Artix, Kintex, Spartan, ISE, Vivado and other designated brands included herein are trademarks of Xilinx

in the United States and other countries. AMBA, AMBA Designer, ARM, Cortex-A9, CoreSight, Cortex, PrimeCell, ARM Powered, and ARM Connected Partner are trademarks

of ARM Ltd. All other trademarks are the property of their respective owners.

Introduction

The Zynq®-7000 All Programmable SoCs are available in

-3, -2, -2LI, -1, and -1LQ speed grades, with -3 having the

highest performance. The -2LI devices operate at

programmable logic (PL) V

CCINT

/V

CCBRAM

= 0.95V and are

screened for lower maximum static power. The speed

specification of a -2LI device is the same as that of a

-2 device. The -1LQ devices operate at the same voltage

and speed as the -1Q devices and are screened for lower

power. Zynq-7000 device DC and AC characteristics are

specified in commercial, extended, industrial, and

expanded (Q-temp) temperature ranges. Except the

operating temperature range or unless otherwise noted, all

the DC and AC electrical parameters are the same for a

particular speed grade (that is, the timing characteristics of

a -1 speed grade industrial device are the same as for a -1

speed grade commercial device). However, only selected

speed grades and/or devices are available in the

commercial, extended, or industrial temperature ranges.

All supply voltage and junction temperature specifications

are representative of worst-case conditions. The

parameters included are common to popular designs and

typical applications.

The available device/package combinations are outlined in:

• Zynq-7000 All Programmable SoC Overview (DS190

)

• Defense-grade Zynq-7000Q All Programmable SoC

Overview (DS196

)

• XA Zynq-7000 All Programmable SoC Overview

(

DS188)

This Zynq-7000 AP SoC data sheet, which covers the

specifications for the XC7Z030, XA7Z030, XQ7Z030,

XC7Z035, XC7Z045, XQ7Z045, XC7Z100, and XQ7Z100

complements the Zynq-7000 AP SoC documentation suite

available on the Xilinx website at www.xilinx.com/zynq

.

DC Characteristics

Zynq-7000 All Programmable SoC

(Z-7030, Z-7035, Z-7045, and Z-7100):

DC and AC Switching Characteristics

DS191 (v1.18) April 12, 2017 Product Specification

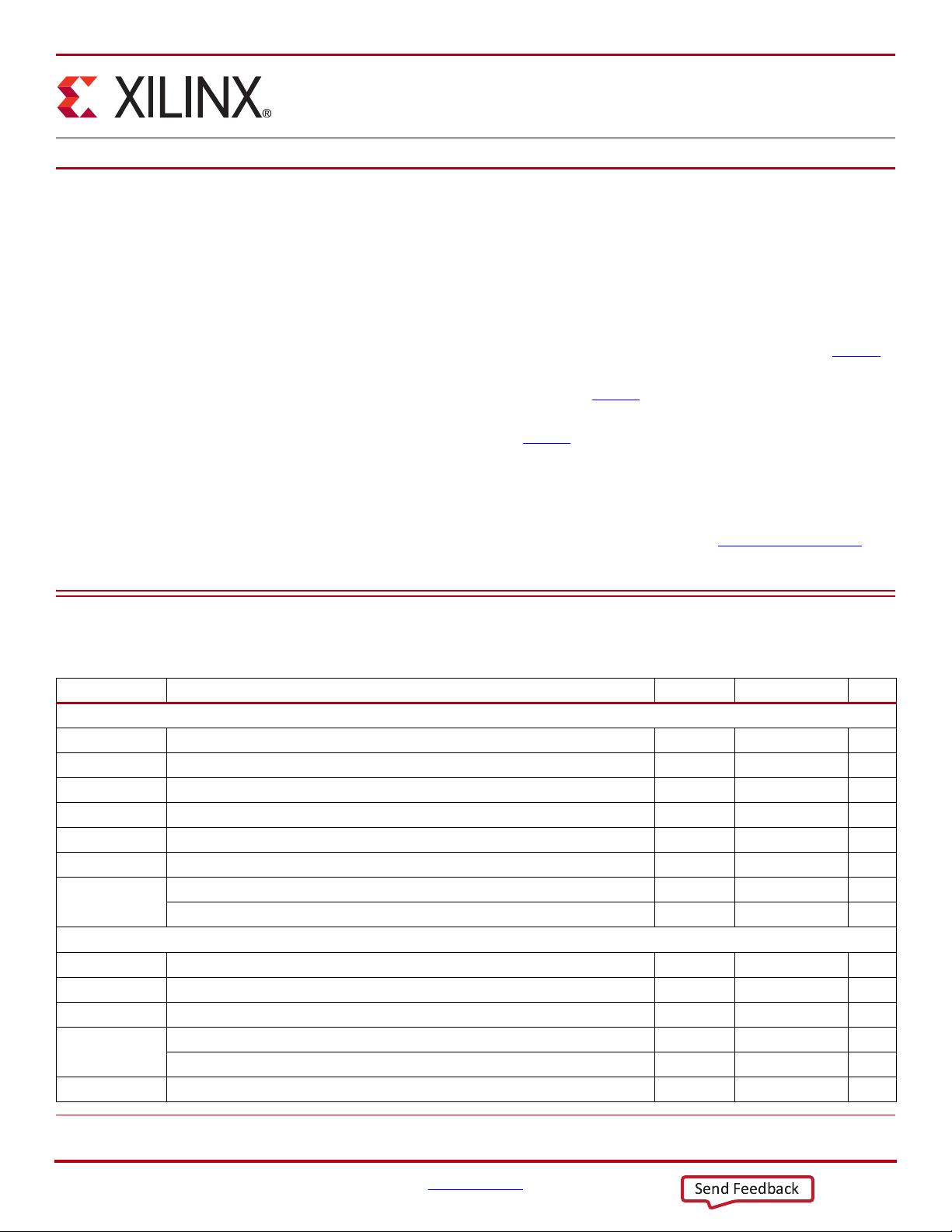

Table 1: Absolute Maximum Ratings

(1)

Symbol Description Min Max Units

Processing System (PS)

V

CCPINT

PS internal logic supply voltage –0.5 1.1 V

V

CCPAUX

PS auxiliary supply voltage –0.5 2.0 V

V

CCPLL

PS PLL supply –0.5 2.0 V

V

CCO_DDR

PS DDR I/O supply –0.5 2.0 V

V

CCO_MIO

(2)

PS MIO I/O supply –0.5 3.6 V

V

PREF

PS input reference voltage –0.5 2.0 V

V

PIN

(2)(3)(4)(5)

PS MIO I/O input voltage –0.40 V

CCO_MIO

+0.55 V

PS DDR I/O input voltage –0.55 V

CCO_DDR

+0.55 V

Programmable Logic (PL)

V

CCINT

PL internal supply voltage

–0.5 1.1 V

V

CCBRAM

PL supply voltage for the block RAM memories

–0.5 1.1 V

V

CCAUX

PL auxiliary supply voltage

–0.5 2.0 V

V

CCO

PL output drivers supply voltage for HR I/O banks

–0.5 3.6 V

PL output drivers supply voltage for HP I/O banks

–0.5 2.0 V

V

CCAUX_IO

(4)

Auxiliary supply voltage

–0.5 2.06 V

Send Feedback

Zynq-7000 AP SoC (Z-7030, Z-7035, Z-7045, and Z-7100): DC and AC Switching Characteristics

DS191 (v1.18) April 12, 2017 www.xilinx.com

Product Specification 2

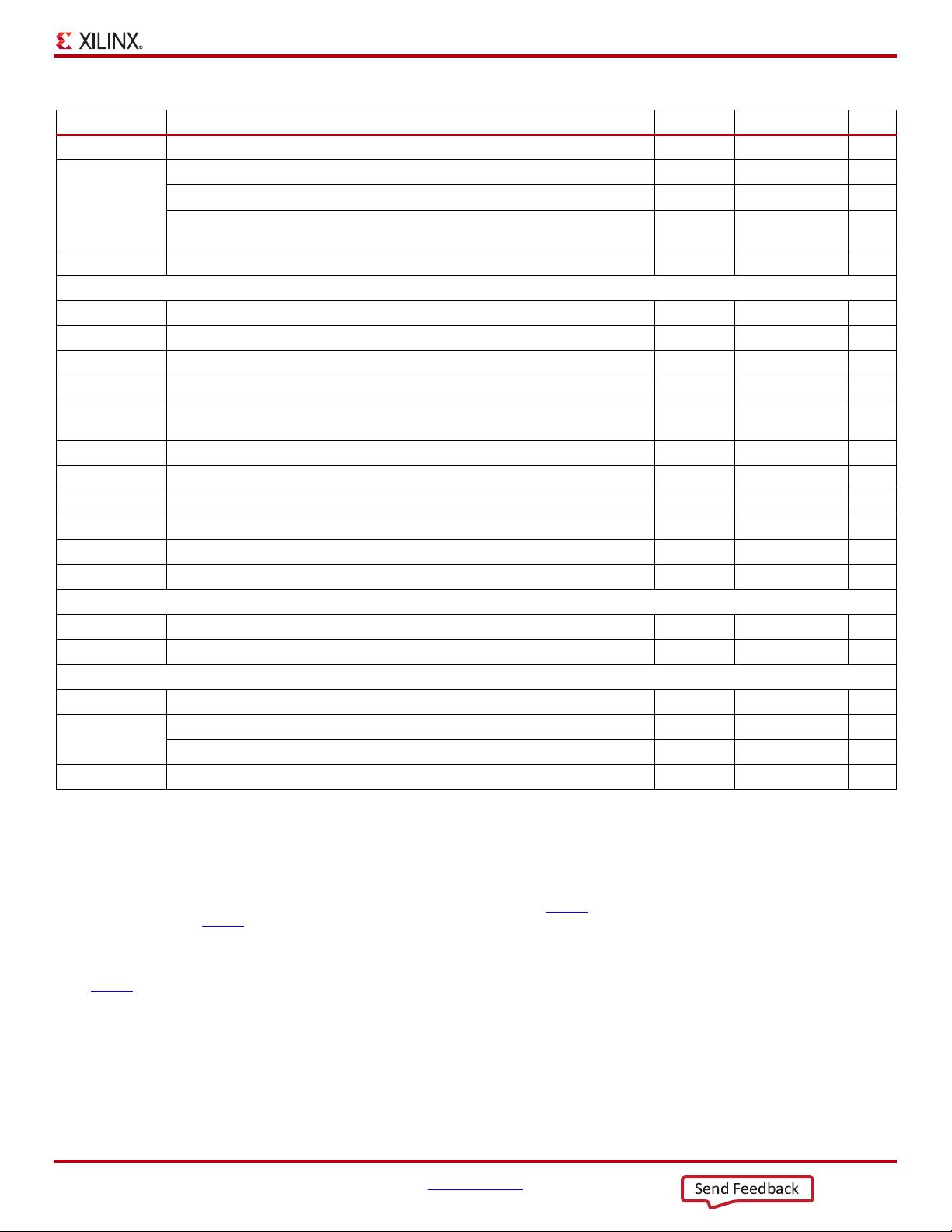

V

REF

Input reference voltage

–0.5 2.0 V

V

IN

(3)(4)(5)

I/O input voltage for HR I/O banks –0.40 V

CCO

+0.55 V

I/O input voltage for HP I/O banks –0.55 V

CCO

+0.55 V

I/O input voltage (when V

CCO

= 3.3V) for V

REF

and differential I/O standards

except TMDS_33

(6)

–0.40 2.625 V

V

CCBATT

Key memory battery backup supply

–0.5 2.0 V

GTX Transceiver

V

MGTAVCC

Analog supply voltage for the GTX transmitter and receiver circuits –0.5 1.1 V

V

MGTAVTT

Analog supply voltage for the GTX transmitter and receiver termination circuits –0.5 1.32 V

V

MGTVCCAUX

Auxiliary analog Quad PLL (QPLL) voltage supply for the GTX transceivers –0.5 1.935 V

V

MGTREFCLK

GTX transceiver reference clock absolute input voltage –0.5 1.32 V

V

MGTAVTTRCAL

Analog supply voltage for the resistor calibration circuit of the GTX transceiver

column

–0.5 1.32 V

V

IN

Receiver (RXP/RXN) and Transmitter (TXP/TXN) absolute input voltage –0.5 1.26 V

I

DCIN-FLOAT

DC input current for receiver input pins DC coupled RX termination = floating – 14 mA

I

DCIN-MGTAVTT

DC input current for receiver input pins DC coupled RX termination = V

MGTAVTT

–12mA

I

DCIN-GND

DC input current for receiver input pins DC coupled RX termination = GND – 6.5 mA

I

DCOUT-FLOAT

DC output current for transmitter pins DC coupled RX termination = floating – 14 mA

I

DCOUT-MGTAVTT

DC output current for transmitter pins DC coupled RX termination = V

MGTAVTT

–12mA

XADC

V

CCADC

XADC supply relative to GNDADC

–0.5 2.0 V

V

REFP

XADC reference input relative to GNDADC

–0.5 2.0 V

Temperature

T

STG

Storage temperature (ambient)

–65 150 °C

T

SOL

Maximum soldering temperature for Pb/Sn component bodies

(7)

– +220 °C

Maximum soldering temperature for Pb-free component bodies

(7)

– +260 °C

T

j

Maximum junction temperature

(7)

– +125 °C

Notes:

1. Stresses beyond those listed under Absolute Maximum Ratings might cause permanent damage to the device. These are stress ratings only,

and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied.

Exposure to Absolute Maximum Ratings conditions for extended periods of time might affect device reliability.

2. Applies to both MIO supply banks V

CCO_MIO0

and V

CCO_MIO1

.

3. The lower absolute voltage specification always applies.

4. For I/O operation, refer to the 7 Series FPGAs SelectIO Resources User Guide (UG471

) or the Zynq-7000 All Programmable SoC Technical

Reference Manual (UG585

).

5. The maximum limit applies to DC signals. For maximum undershoot and overshoot AC specifications, see Table 4 and Table 5.

6. See Table 12 for TMDS_33 specifications.

7. For soldering guidelines and thermal considerations, see the Zynq-7000 All Programmable SoC Packaging and Pinout Specification

(UG865

).

Table 1: Absolute Maximum Ratings

(1)

(Cont’d)

Symbol Description Min Max Units

Send Feedback

Zynq-7000 AP SoC (Z-7030, Z-7035, Z-7045, and Z-7100): DC and AC Switching Characteristics

DS191 (v1.18) April 12, 2017 www.xilinx.com

Product Specification 3

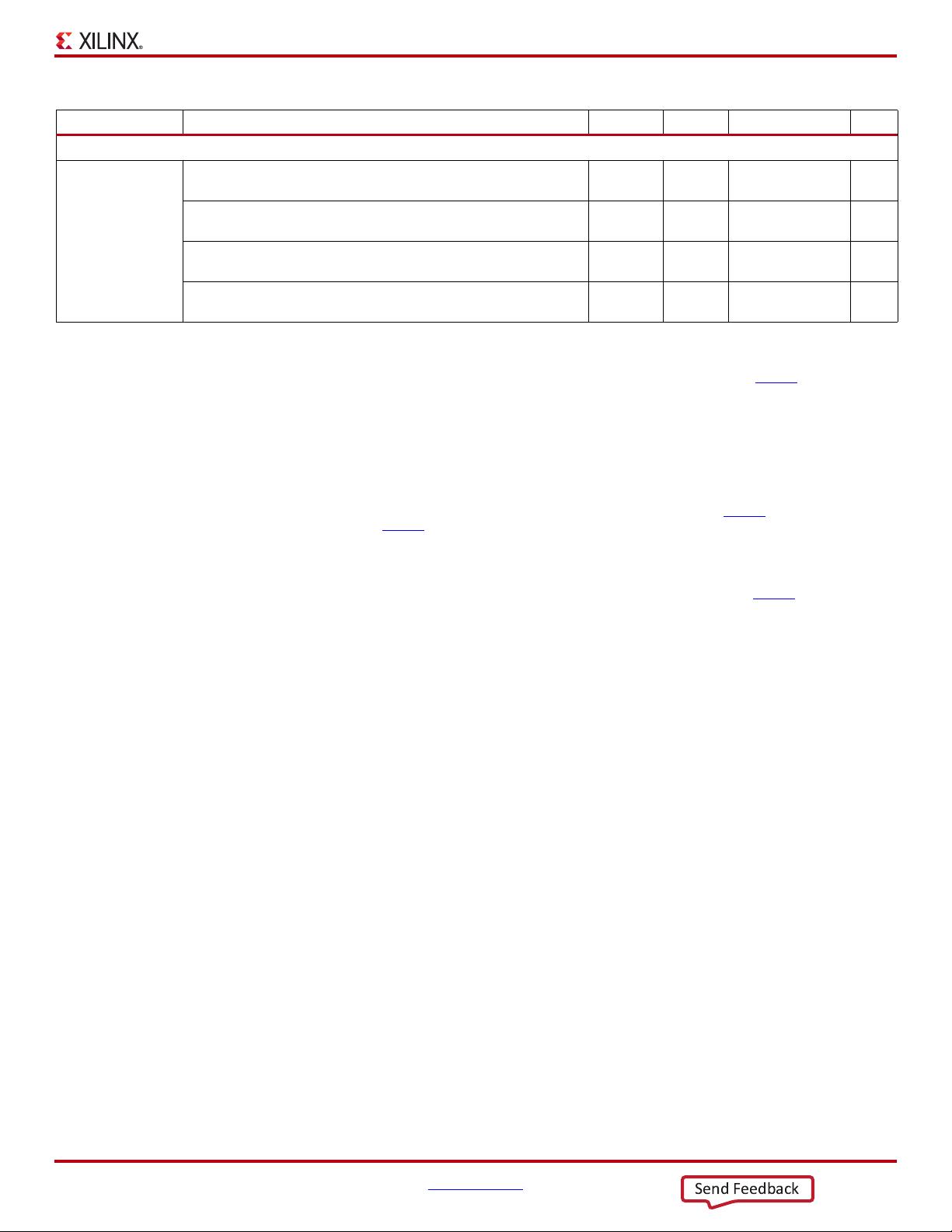

Table 2: Recommended Operating Conditions

(1)(2)

Symbol Description Min Typ Max Units

PS

V

CCPINT

(3)

PS internal logic supply voltage 0.95 1.00 1.05 V

V

CCPAUX

PS auxiliary supply voltage 1.71 1.80 1.89 V

V

CCPLL

PS PLL supply voltage 1.71 1.80 1.89 V

V

CCO_DDR

PS DDR supply voltage 1.14 – 1.89 V

V

CCO_MIO

(4)

PS supply voltage for MIO banks 1.71 – 3.465 V

V

PIN

(5)

PS DDR and MIO I/O input voltage –0.20 –

V

CCO_DDR

+ 0.20

V

CCO_MIO

+0.20

V

PL

V

CCINT

(6)

PL internal supply voltage 0.97 1.00 1.03 V

PL -2LI (0.95V) internal supply voltage 0.93 0.95 0.97 V

V

CCBRAM

(6)

PL block RAM supply voltage 0.97 1.00 1.03 V

PL -2LI (0.95V) block RAM supply voltage 0.93 0.95 0.97 V

V

CCAUX

PL auxiliary supply voltage 1.71 1.80 1.89 V

V

CCO

(7)(8)

PL supply voltage for HR I/O banks 1.14 – 3.465 V

PL supply voltage for HP I/O banks 1.14 – 1.89 V

V

CCAUX_IO

(9)

PL auxiliary supply voltage when set to 1.8V 1.71 1.80 1.89 V

PL auxiliary supply voltage when set to 2.0V 1.94 2.00 2.06 V

V

IN

(5)

I/O input voltage –0.20 – V

CCO

+0.20 V

I/O input voltage (when V

CCO

= 3.3V) for V

REF

and differential

I/O standards except TMDS_33

(10)

–0.20 – 2.625 V

I

IN

(11)

Maximum current through any (PS or PL) pin in a powered or

unpowered bank when forward biasing the clamp diode

–– 10 mA

V

CCBATT

(12)

Battery voltage 1.0 – 1.89 V

GTX Transceiver

V

MGTAVCC

(13)

Analog supply voltage for the GTX transceiver QPLL frequency

range ≤ 10.3125 GHz

(14)(15)

0.97 1.0 1.08 V

Analog supply voltage for the GTX transceiver QPLL frequency

range > 10.3125 GHz

1.02 1.05 1.08

V

MGTAVTT

(13)

Analog supply voltage for the GTX transmitter and receiver

termination circuits

1.17 1.2 1.23 V

V

MGTVCCAUX

(13)

Auxiliary analog QPLL voltage supply for the transceivers 1.75 1.80 1.85 V

V

MGTAVTTRCAL

(13)

Analog supply voltage for the resistor calibration circuit of the

GTX transceiver column

1.17 1.2 1.23 V

XADC

V

CCADC

XADC supply relative to GNDADC 1.71 1.80 1.89 V

V

REFP

Externally supplied reference voltage 1.20 1.25 1.30 V

Send Feedback

Zynq-7000 AP SoC (Z-7030, Z-7035, Z-7045, and Z-7100): DC and AC Switching Characteristics

DS191 (v1.18) April 12, 2017 www.xilinx.com

Product Specification 4

Temperature

T

j

Junction temperature operating range for commercial (C)

temperature devices

0– 85 °C

Junction temperature operating range for extended (E)

temperature devices

0– 100 °C

Junction temperature operating range for industrial (I)

temperature devices

–40 – 100 °C

Junction temperature operating range for expanded (Q)

temperature devices

–40 – 125 °C

Notes:

1. All voltages are relative to ground. The PL and PS share a common ground.

2. For the design of the power distribution system consult the Zynq-7000 All Programmable SoC PCB Design Guide (UG933

).

3. When the processor cores operate F

CPU_6X4X_621_MAX

at 1 GHz (-3E speed grade) or when the DDR interface operates at 1333 Mb/s, the

V

CCPINT

minimum is 0.97V and the V

CCPINT

maximum is 1.03V.

4. Applies to both MIO supply banks V

CCO_MIO0

and V

CCO_MIO1

.

5. The lower absolute voltage specification always applies.

6. V

CCINT

and V

CCBRAM

should be connected to the same supply.

7. Configuration data is retained even if V

CCO

drops to 0V.

8. Includes V

CCO

of 1.2V, 1.35V, 1.5V, 1.8V, 2.5V (HR I/O only), and 3.3V (HR I/O only) at ±5%.

9. For more information, refer to the V

CCAUX_IO

section of the 7 Series FPGAs SelectIO Resources User Guide (UG471) or the Zynq-7000 All

Programmable SoC Technical Reference Manual (UG585

).

10. See Table 12 for TMDS_33 specifications.

11. A total of 200 mA per PS or PL bank should not be exceeded.

12. V

CCBATT

is required only when using bitstream encryption. If battery is not used, connect V

CCBATT

to either ground or V

CCAUX

.

13. Each voltage listed requires the filter circuit described in the 7 Series FPGAs GTX/GTH Transceivers User Guide (UG476

).

14. For data rates ≤ 10.3125 Gb/s, V

MGTAVCC

should be 1.0V ±3% for lower power consumption.

15. For lower power consumption, V

MGTAVCC

should be 1.0V ±3% over the entire CPLL frequency range.

Table 2: Recommended Operating Conditions

(1)(2)

(Cont’d)

Symbol Description Min Typ Max Units

Send Feedback

Zynq-7000 AP SoC (Z-7030, Z-7035, Z-7045, and Z-7100): DC and AC Switching Characteristics

DS191 (v1.18) April 12, 2017 www.xilinx.com

Product Specification 5

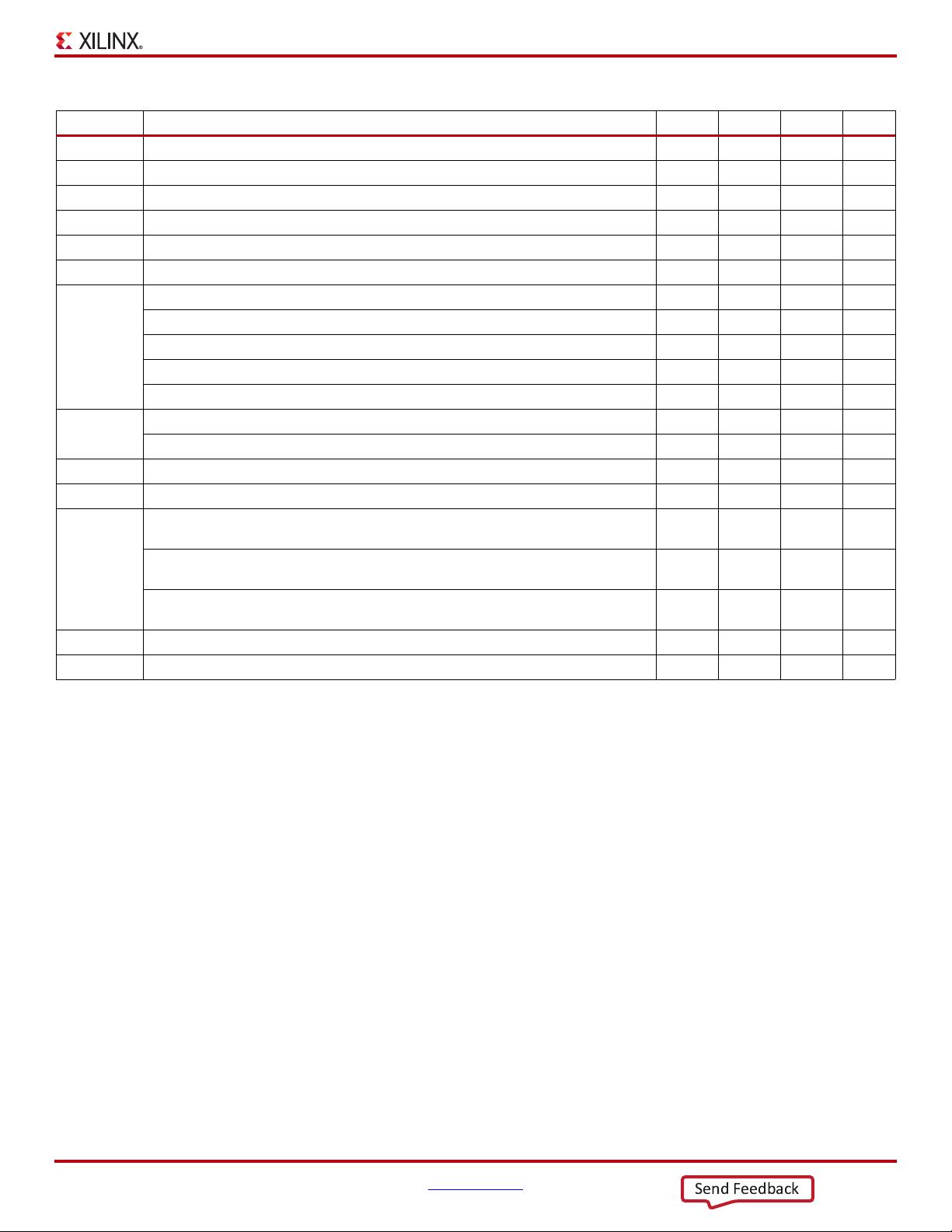

Table 3: DC Characteristics Over Recommended Operating Conditions

Symbol Description Min Typ

(1)

Max Units

V

DRINT

Data retention V

CCINT

voltage (below which configuration data might be lost) 0.75 – – V

V

DRI

Data retention V

CCAUX

voltage (below which configuration data might be lost) 1.5 – – V

I

REF

PS_DDR_VREF 0/1, PS_MIO_VREF, and V

REF

leakage current per pin – – 15 µA

I

L

Input or output leakage current per pin (sample-tested) – – 15 µA

C

IN

(2)

PL die input capacitance at the pad – – 8 pF

C

PIN

(2)

PS die input capacitance at the pad – – 8 pF

I

RPU

Pad pull-up (when selected) @ V

IN

=0V, V

CCO

=3.3V 90 – 330 µA

Pad pull-up (when selected) @ V

IN

=0V, V

CCO

=2.5V 68 – 250 µA

Pad pull-up (when selected) @ V

IN

=0V, V

CCO

=1.8V 34 – 220 µA

Pad pull-up (when selected) @ V

IN

=0V, V

CCO

=1.5V 23 – 150 µA

Pad pull-up (when selected) @ V

IN

=0V, V

CCO

=1.2V 12 – 120 µA

I

RPD

Pad pull-down (when selected) @ V

IN

=3.3V 68 – 330 µA

Pad pull-down (when selected) @ V

IN

=1.8V 45 – 180 µA

I

CCADC

Analog supply current, analog circuits in powered up state – – 25 mA

I

BATT

(3)

Battery supply current – – 150 nA

R

IN_TERM

(4)

Thevenin equivalent resistance of programmable input termination to V

CCO

/2

(UNTUNED_SPLIT_40)

28 40 55 Ω

Thevenin equivalent resistance of programmable input termination to V

CCO

/2

(UNTUNED_SPLIT_50)

35 50 65 Ω

Thevenin equivalent resistance of programmable input termination to V

CCO

/2

(UNTUNED_SPLIT_60)

44 60 83 Ω

n Temperature diode ideality factor – 1.010 – –

r Temperature diode series resistance – 2 – Ω

Notes:

1. Typical values are specified at nominal voltage, 25°C.

2. This measurement represents the die capacitance at the pad, not including the package.

3. Maximum value specified for worst case process at 25°C.

4. Termination resistance to a V

CCO

/2 level.

Send Feedback

剩余85页未读,继续阅读

资源评论

半步成诗!

- 粉丝: 53

- 资源: 13

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 西门子数控系统调试与通讯:828D、840D、808D的参数配置、梯形图修改及外部IO增加案例分享,西门子数控系统调试与配置手册:涉及828D、840D与808D系统的参数调整、梯形图修改与外部通讯实

- 中国各类互联网应用的用户规模数据.zip

- 中国各省地图(包含港澳台) 山西(shanxi)陕西(shanxi1)

- E000620医院体检医疗健康类网站模板+PHP+Mysql+响应式+CMS+建站模板

- 中国各省对应各市级地图json

- 大模型基础-30分钟一文了解大模型基础知识(人工智能必读).zip

- COMSOL模拟:二氧化碳充装与输气管道泄漏的耦合温度场分析,输出速度与温度分布,COMSOL模拟:二氧化碳充装与输气管道泄漏的耦合温度场分析,输出速度与温度分布,comsol 二氧化碳充装二氧化碳输

- 基于python开发的简单的windows桌面画笔功能,全部使用快捷键操作(python源码+图文教程),开箱即用,非常优质的资源

- C#上位机与西门子PLC通讯教程:数据读取存储、报表生成、报警历史查询及变量自定义配置实战案例详解,C#上位机与西门子PLC通讯教程:数据读取存储、报表生成、报警历史查询及变量自定义配置实战案例详解

- 基于遗传算法的锂电池二阶RC模型参数辨识技术研究-附Matlab程序与多种工况充放电数据集(DST、FUDs、US06、BJDST等八种),基于遗传算法的锂电池二阶RC模型参数辨识技术研究-附Ma

- 利用格子玻尔兹曼方法LBM D1Q3模型在Matlab中模拟一维扩散方程的研究,使用格子玻尔兹曼方法LBM D1Q3模拟一维扩散方程的Matlab实现与应用研究,使用格子玻尔兹曼方法LBM D1Q3模

- 流水线电机变频调速系统设计 MATLAB电路建模仿真

- 2022年美国各州基本经济统计数据.zip

- 基于Transformer的Matlab代码:数据回归与多场景预测工具箱,Transformer在数据回归分析中的应用-基于Matlab代码的实战教学,Transformer回归 Matlab代码

- Sigma-Delta ADC Matlab模型集合:包含CTSD调制器、FFT分析、动态静态特性仿真与教程,方便入门学习,Continuous-Time Sigma-Delta ADC Matlab

- 基于Comsol仿真的兰姆波导波在钢板中的传播及裂隙检测分析,Comsol仿真中兰姆波导波在有限尺寸钢板内传播的裂隙检测技术研究,Comsol仿真无损检测时产生的兰姆波 导波在宽度和厚度有限的钢板中传

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功