XilinxISE软件简单教程PPT课件PPT学习教案.pptx

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

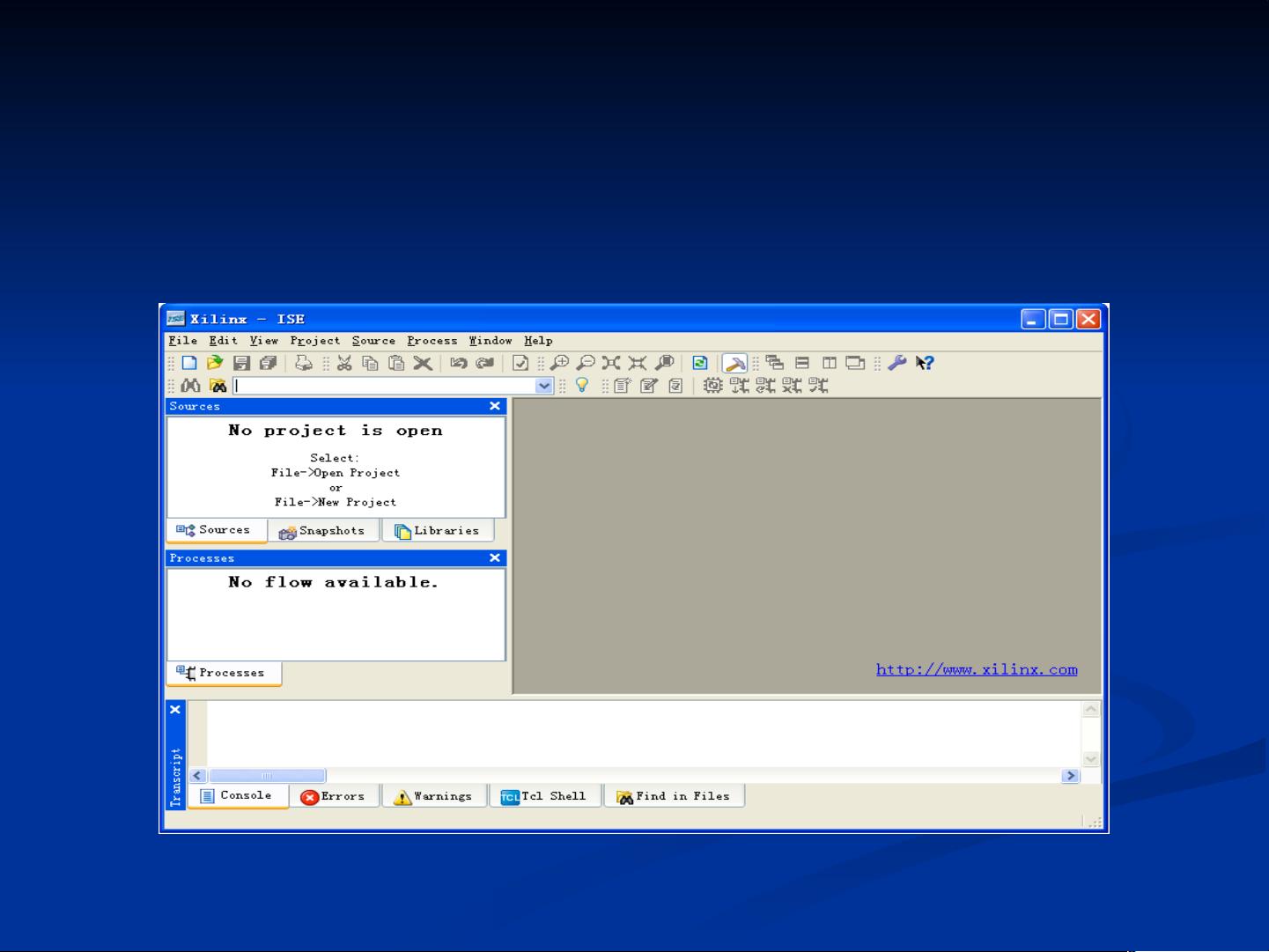

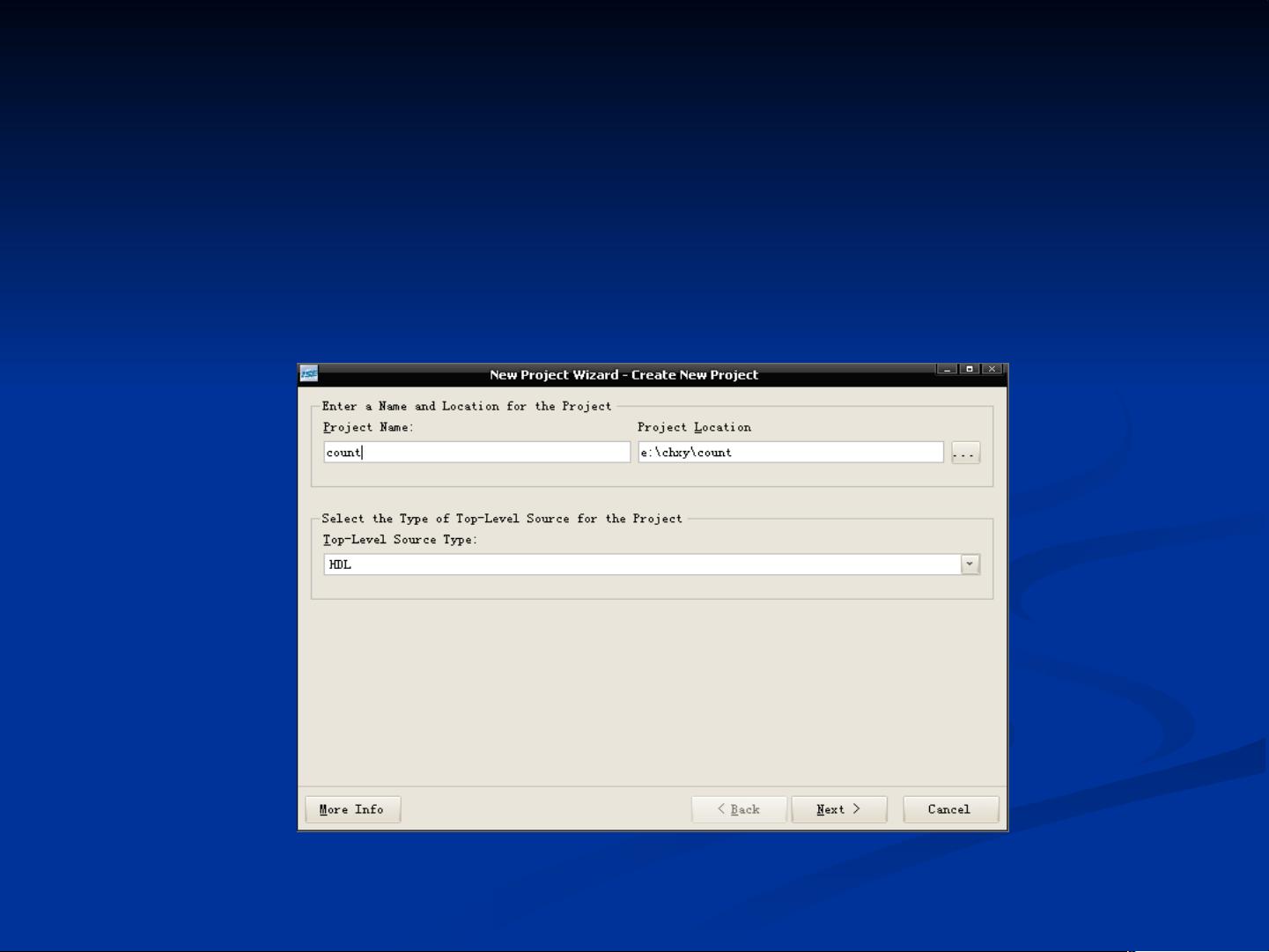

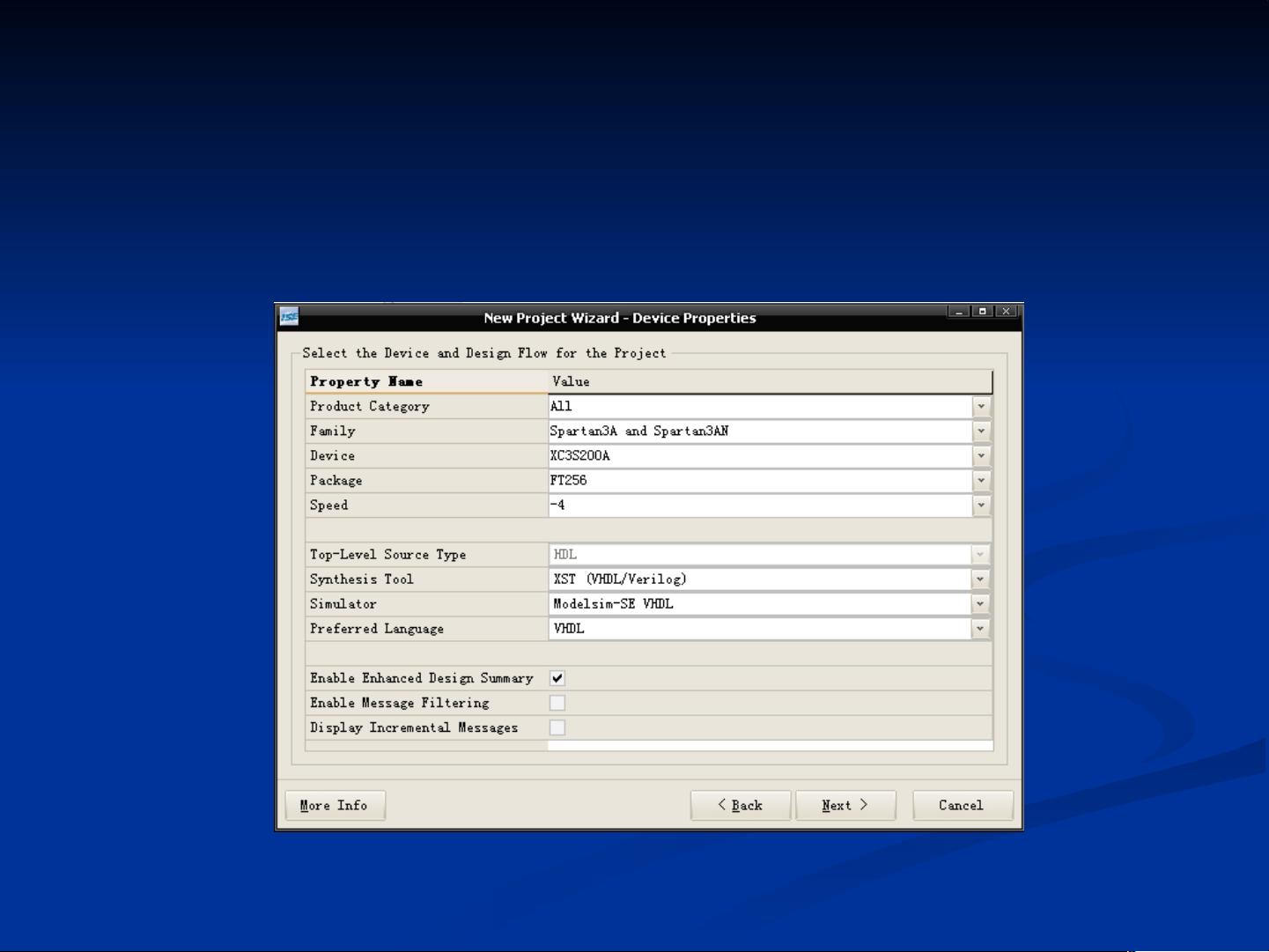

《Xilinx ISE软件简单教程》是一份详细指导如何使用Xilinx Integrated Software Environment(ISE)进行数字逻辑设计的教程。该教程适用于初学者,通过PPT形式呈现,旨在帮助学习者掌握利用Xilinx ISE设计和实现FPGA(Field-Programmable Gate Array)电路的基本步骤。 教程以一个具体的设计任务为例,即设计一个模16计数器。这个计数器需要在48MHz的系统输入时钟下工作,生成1Hz的输出信号,并用LED指示灯显示。同时,它还要输出模16的数据,同样通过4个LED显示。具体的管脚分配为:CLK连接至T8,模16的四个LED分别连接至C10、A10、B10和A9,1Hz信号的LED连接至B8。 接下来,教程逐步介绍了使用Xilinx ISE软件进行项目建立的流程。启动Xilinx ISE 9.1并打开Project Navigator。然后,通过菜单栏的【File】->【New Project】创建新项目,设定项目名称和保存路径,需要注意的是,项目文件名应避免使用中文和数字开头。在新项目对话框中,按照提示配置参数,如选择设备、目标板等。 在项目建立后,需要添加源文件。通过【Project】->【New Source】新建源文件,选择VHDL Module作为文件类型。在新建文件中,输入VHDL代码来实现模16计数器的功能。例如,定义实体cnt16,包含输入时钟clk、输出数据dout和dclk1,以及内部信号clk1、q、w。接着,编写两个过程t1和t2,分别用于计数器主时钟的翻转和模16计数值的更新。 为了确保代码无误,需要进行语法检查。在Source Navigator中选择Check Syntax,根据报告窗口中的错误提示进行修正,直至报告成功。之后,进行功能仿真,创建新的仿真源文件,设置激励信号,如时钟Clk的值。通过双击Simulate Behavioral Model运行仿真,观察波形窗口以验证设计是否符合预期。 设计完成后需要进行综合和实现,这包括逻辑优化、映射到FPGA结构、管脚分配等步骤。这部分通常涉及【Synthesis】和【Implement Design】等工具,以确保设计能在目标硬件上正确运行。在实现完成后,生成编程文件,通过JTAG或其它接口下载到FPGA中。 这份Xilinx ISE软件简单教程覆盖了从项目创建、VHDL编程、语法检查、功能仿真到综合实现的整个流程,是学习FPGA设计和Xilinx ISE软件操作的宝贵资源。通过实践这个教程,学习者将能熟练掌握基本的FPGA设计技能。

剩余26页未读,继续阅读

- 粉丝: 8

- 资源: 58万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 行政管理人员面试题.doc

- 行政秘书.doc

- 秘书笔试题.doc

- 01.经典行为面试题目(个人品行).doc

- 02.经典行为面试题目(认知能力).doc

- 05.素质模型与行为面试题库(销售).doc

- 06.外企面试常见问题114例(中英文对照).doc

- 12.中外知名企业的招聘典型试题精选.doc

- 13.经典行为面试题目(动力系统二).docx

- 20.行为面试法精讲精练.ppt

- 19.校园招聘及行为面试法.ppt

- 22.基于胜任力的行为面试法.pptx

- 01.20XXjava面试题全攻略.doc

- 03.IT MRPII人员考试试题.doc

- 06.JAVA-SSH面试题.doc

- 12.SQL面试题目汇总.doc

信息提交成功

信息提交成功