PCI EXPRESS BASE SPECIFICATION, REV. 3.0

5

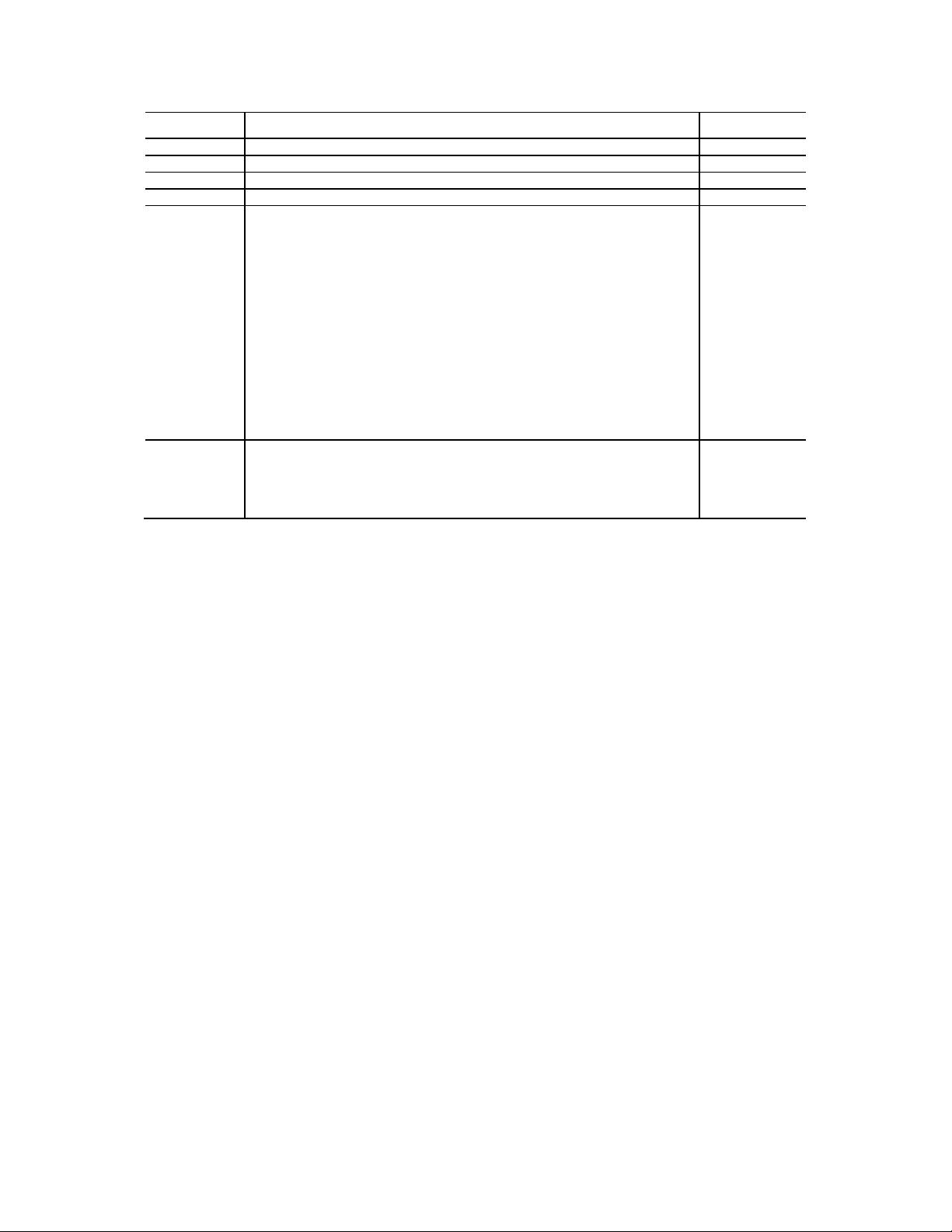

4.3. ELECTRICAL SUB-BLOCK ............................................................................................. 323

4.3.1. Electrical Specification Organization................................................................. 323

4.3.2. Interoperability Criteria for 2.5, 5.0, and 8.0 GT/s Devices .............................. 323

4.3.3. Transmitter Specification.................................................................................... 325

4.3.4. Receiver Specifications....................................................................................... 359

4.3.5. Low Frequency and Miscellaneous Signaling Requirements............................. 382

4.3.6. Channel Specification......................................................................................... 387

4.3.7. Refclk Specifications........................................................................................... 400

4.3.8. Refclk Specifications for 8.0 GT/s....................................................................... 408

5. POWER MANAGEMENT................................................................................................. 413

5.1. OVERVIEW ................................................................................................................... 413

5.1.1. Statement of Requirements.................................................................................. 414

5.2. LINK STATE POWER MANAGEMENT............................................................................. 414

5.3. PCI-PM

SOFTWARE COMPATIBLE MECHANISMS......................................................... 419

5.3.1. Device Power Management States (D-States) of a Function.............................. 419

5.3.2. PM Software Control of the Link Power Management State.............................. 424

5.3.3. Power Management Event Mechanisms............................................................. 429

5.4. N

ATIVE PCI EXPRESS POWER MANAGEMENT MECHANISMS....................................... 436

5.4.1. Active State Power Management (ASPM) .......................................................... 436

5.5. AUXILIARY POWER SUPPORT....................................................................................... 455

5.5.1. Auxiliary Power Enabling................................................................................... 455

5.6. POWER MANAGEMENT SYSTEM MESSAGES AND DLLPS............................................. 456

6. SYSTEM ARCHITECTURE ............................................................................................. 459

6.1. INTERRUPT AND PME SUPPORT ................................................................................... 459

6.1.1. Rationale for PCI Express Interrupt Model........................................................ 459

6.1.2. PCI Compatible INTx Emulation........................................................................ 460

6.1.3. INTx Emulation Software Model ........................................................................ 460

6.1.4. Message Signaled Interrupt (MSI/MSI-X) Support............................................. 460

6.1.5. PME Support....................................................................................................... 462

6.1.6. Native PME Software Model .............................................................................. 462

6.1.7. Legacy PME Software Model ............................................................................. 463

6.1.8. Operating System Power Management Notification........................................... 463

6.1.9. PME Routing Between PCI Express and PCI Hierarchies ................................ 463

6.2. E

RROR SIGNALING AND LOGGING................................................................................ 464

6.2.1. Scope................................................................................................................... 464

6.2.2. Error Classification............................................................................................ 464

6.2.3. Error Signaling................................................................................................... 466

6.2.4. Error Logging..................................................................................................... 474

6.2.5. Sequence of Device Error Signaling and Logging Operations .......................... 478

6.2.6. Error Message Controls ..................................................................................... 480

6.2.7. Error Listing and Rules ...................................................................................... 481

6.2.8. Virtual PCI Bridge Error Handling.................................................................... 486

6.2.9. Internal Errors.................................................................................................... 488

6.3. VIRTUAL CHANNEL SUPPORT ...................................................................................... 489

6.3.1. Introduction and Scope....................................................................................... 489

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功

评论2