没有合适的资源?快使用搜索试试~ 我知道了~

实验一 Xilinx-ISE13软件使用.docx

1.该资源内容由用户上传,如若侵权请联系客服进行举报

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

版权申诉

0 下载量 9 浏览量

2023-04-06

19:50:03

上传

评论

收藏 3.74MB DOCX 举报

温馨提示

试读

23页

。

资源推荐

资源详情

资源评论

实验一 Xilinx_ISE 软件使用与计数器相关实验

一、实验目的

1.1 了解并掌握采用可编程逻辑器件实现数字电路与系统的方法;

1.2 学习并掌握采用Xilinx_ISE 软件开发可编程器件的过程

1.3 学习使用verilog HDL描述数字逻辑电路与系统的方法;

1.4 掌握分层次、分模块的电路设计方法,熟悉使用可编程器件实现数字系统的一

般步骤。

二、实验条件

PC机

Xilinx ISE13.1 软件

USB下载线

Digilent Adept软件(2.0或更新版)

Xilinx大学计划开发板Basys2

三、预习要求

阅读实验原理及参考资料,了解使用Xilinx ISE13.1 软件开发Xilinx 可编程器件,设

计实现所需电子系统的流程。

四、实验原理

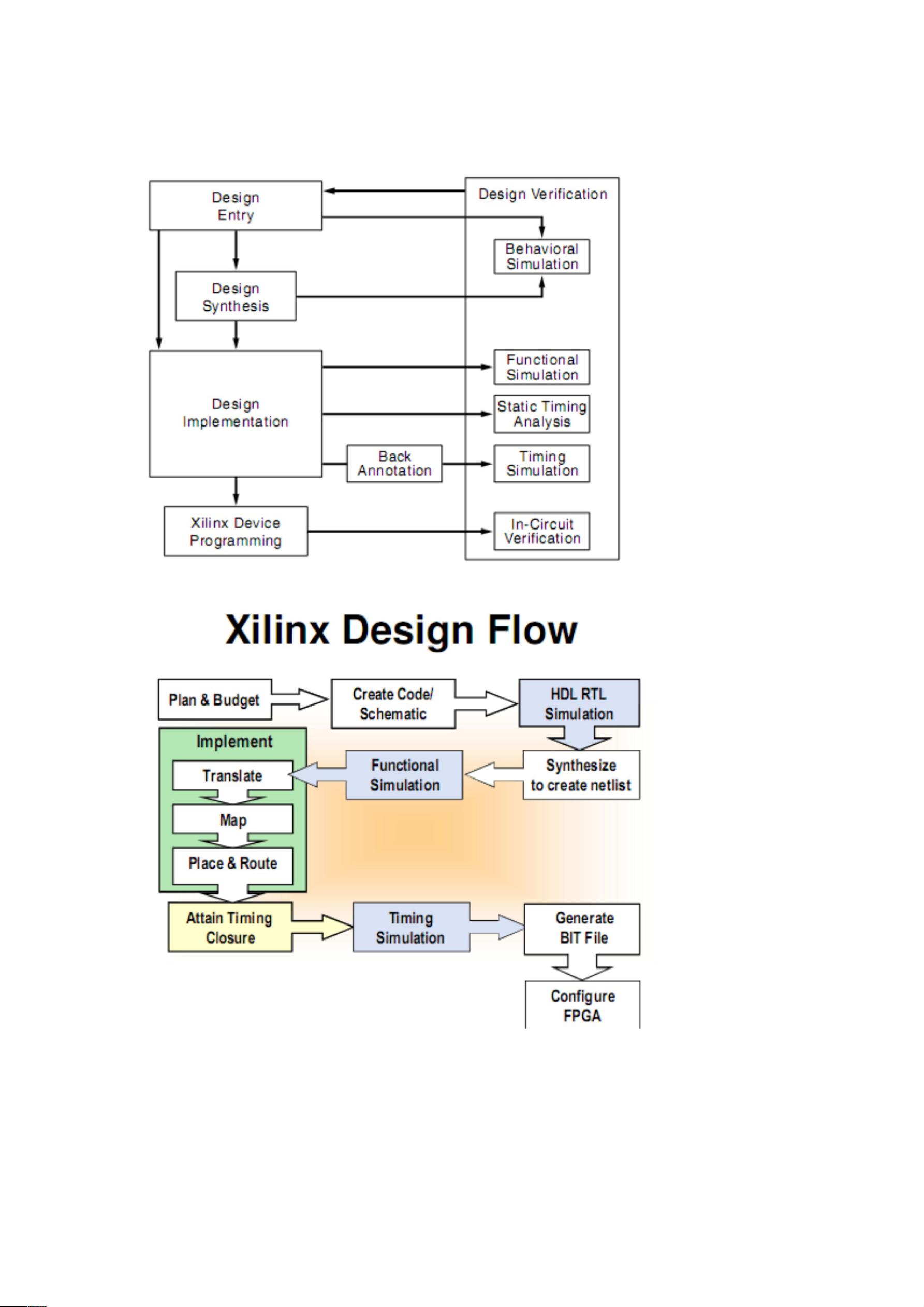

4.1 可编程器件开发流程

4.2 Xilinx ISE13.1 软件概要介绍

ISE 简要介绍

Xilinx 是全球领先的可编程逻辑完整解决方案的供应商,研发、制造并销售应用范围广泛

的高级集成电路、软件设计工具以及定义系统级功能的 IP(Intellectual Property)核,长期

以来一直推动着 FPGA 技术的发展。Xilinx 的开发工具也在不断地升级,目前的 ISE Project

Navigator 13.x 集成了 FPGA 开发需要的所有功能,其主要特点有:

• 包含了 Xilinx 新型 SmartCompile 技术,可以将实现时间缩减 2.5 倍,能在最短的时间

内提供最高的性能,提供了一个功能强大的设计收敛环境;

• 全面支持 Virtex-5 系列器件(业界首款 65nm FPGA);

• 集成式的时序收敛环境有助于快速、轻松地识别 FPGA 设计的瓶颈;

• 可以节省一个或多个速度等级的成本,并可在逻辑设计中实现最低的总成本。

ISE Project Navigator 13.x 的主要功能包括设计输入、综合、仿真、实现和下载,涵盖

了 FPGA 开发的全过程,从功能上讲,其工作流程无需借助任何第三方 EDA 软件。

• 设计输入:ISE 提供的设计输入工具包括用于 HDL 代码输入和查看报告的 ISE 文本编

辑器(The ISE Text Editor),用于原理图编辑的工具 ECS(The Engineering Capture

System),用于生成 IP Core 的 Core Generator,用于状态机设计的 StateCAD 以及用于约

束文件编辑的 Constraint Editor 等。

• 综合:ISE 的综合工具不但包含了 Xilinx 自身提供的综合工具 XST,同时还可以内嵌

Mentor Graphics 公司的 LeonardoSpectrum 和 Synplicity 公司的 Synplify,实现无缝链接。

• 仿真:ISE 本身自带了一个具有图形化波形编辑功能的仿真工具 HDL Bencher,同

时又提供了使用 Model Tech 公司的 Modelsim 进行仿真的接口。

• 实现:此功能包括了翻译、映射、布局布线等,还具备时序分析、管脚指定以及增

量设计等高级功能。

• 下载:下载功能包括了 BitGen,用于将布局布线后的设计文件转换为位流文件,还

包括了 ImPACT,功能是进行设备配置和通信,控制将程序烧写到 FPGA 芯片中去。

• 使用 ISE 进行 FPGA 设计的各个过程可能涉及到的设计工具如表 4-1 所示。

4.3 使用 Xilinx ISE13.1 软件开发可编程器件的流程介绍

4.3.1 新建工程

( 1)开启 ISE13.1 软 件: 开 始 程 序 Xilinx ISE Design Suite 13.1ISE Design

ToolsProject Navigator,会出现 ISE13.1 的画面.

(2)在 ISE13.1 软件环境下,开启一个新的工程: File New Project.

[Project Name] : lab1_4bitsLEDs

[Project Location]: E:\Training\training_demo\Verilog\lab1_4bitsLEDs (依使用者设定的目录).

[Top-Level Module Type] : HDL( 代表最上层的设计模块是以HDL方式实现的模块.

图 4.3.1:创建新的工程

(3)单击next,下一个画面就是设定硬件FPGA 的参数---请对照实验板芯片系列进行选择!

[FPGA 系 (Device Family)]:Spartan3E( 请看板子的FPGA FPGA 的编号)

[FPGA 名称(Device)] : XC3S100E(请参考开发板的FPGA FPGA 的编号)

[FPGA 包装(Package)]:CP132(请参考开发板的FPGA FPGA 的编号)

[FPGA 速 等级(Speed)]: -4 ( FPGA 速 等级)

[综合工具(Synthesis Tool)]:XST (VHDL/Verilog)

[仿真器(Simulator)] : Isim(VHDL/Verilog)

图 4.3.2:FPGA参数设置

(4)点击next. 此时出现此项目所有设定的信息, 需重新设定,则可back.

finish

无误,则按

剩余22页未读,继续阅读

资源评论

คิดถึง643

- 粉丝: 3931

- 资源: 1万+

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功