Rt-TEC-G-TE188

Writing IFS test cases for existing

IFS test benches

(AMS and digital)

Integrated

Functional Verification

Script Environment – IFSnG 4.1/4.2

Internal | Automotive Electronics | AE/EIV1-Trunzer | 2023-02-21

© Robert Bosch GmbH 2016. All rights reserved, also regarding any disposal, exploitation, reproduction, editing, distribution, as well as in the event of applications for industrial property rights.

IFS - Writing Test Cases (Rt-TEC-G-TE188)

Overview

▪ Introduction into IFS

▪ IFS language (including Labs)

▪ IFS for AMS

▪ Debugging hints

2

Internal | Automotive Electronics | AE/EIV1-Trunzer | 2023-02-21

© Robert Bosch GmbH 2016. All rights reserved, also regarding any disposal, exploitation, reproduction, editing, distribution, as well as in the event of applications for industrial property rights.

IFS - Writing Test Cases (Rt-TEC-G-TE188)

Overview

▪ Introduction into IFS

− Testbench structure

− Concurrency

▪ IFS language (including Labs)

▪ IFS for AMS

▪ Debugging hints

3

Internal | Automotive Electronics | AE/EIV1-Trunzer | 2023-02-21

© Robert Bosch GmbH 2016. All rights reserved, also regarding any disposal, exploitation, reproduction, editing, distribution, as well as in the event of applications for industrial property rights.

IFS - Writing Test Cases (Rt-TEC-G-TE188)

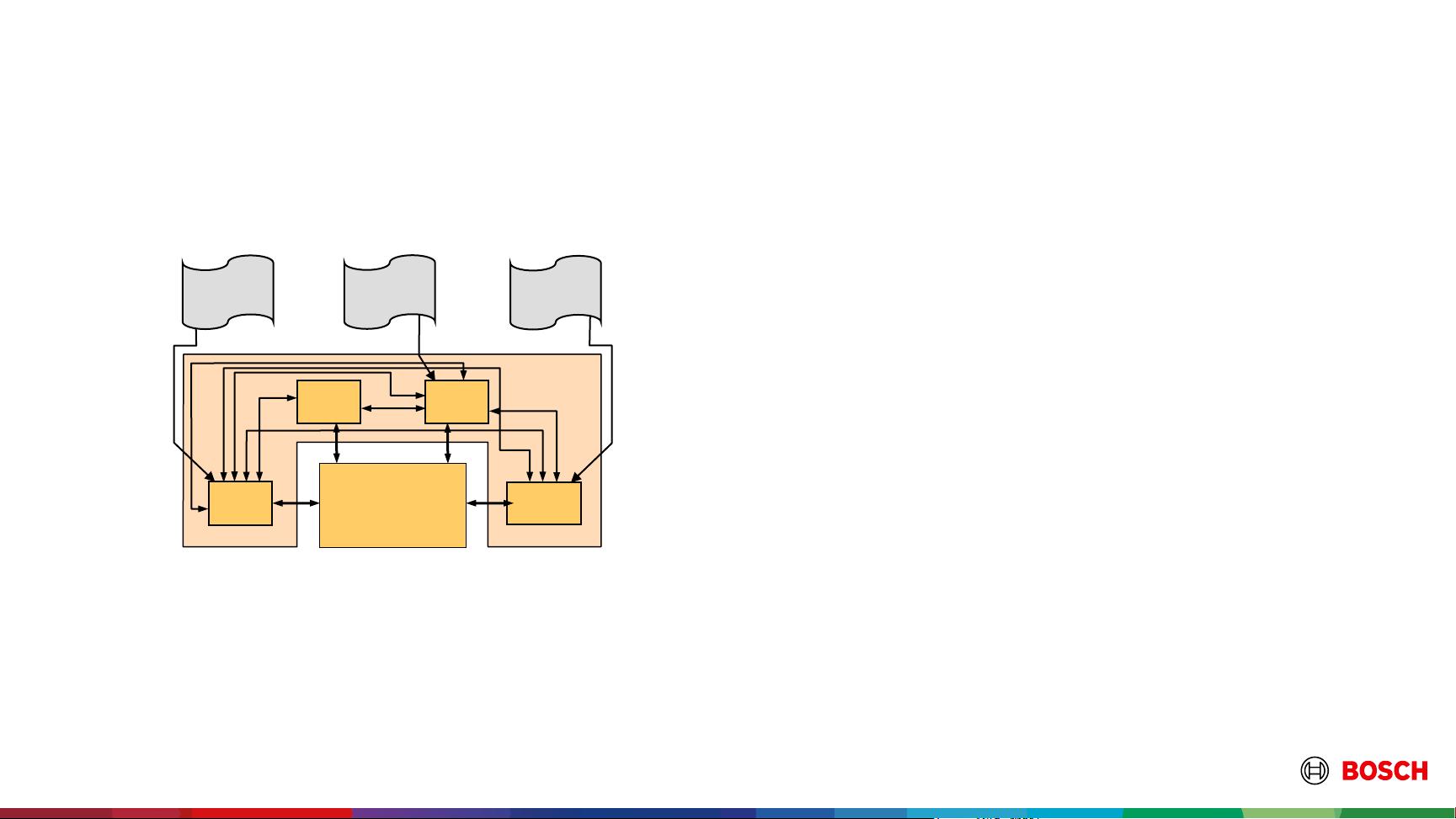

Traditional Test Bench

▪ Characteristics

− Structural interconnect to DUT and between test

bench modules

− Multiple input data

▪ Disadvantages

− Complex test bench structure

− Limited reuse capabilities

− Difficult hard-wired synchronization between test

bench modules

− High implementation effort

Command

File

1

Command

File

4

Command

File

3

IFS

1

Stim

4

IFS

2

IFS

3

Interconnect

Stim

3

Stim

2

Stim

1

DUT

(Device

under Test)

Testbench

4

Internal | Automotive Electronics | AE/EIV1-Trunzer | 2023-02-21

© Robert Bosch GmbH 2016. All rights reserved, also regarding any disposal, exploitation, reproduction, editing, distribution, as well as in the event of applications for industrial property rights.

IFS - Writing Test Cases (Rt-TEC-G-TE188)

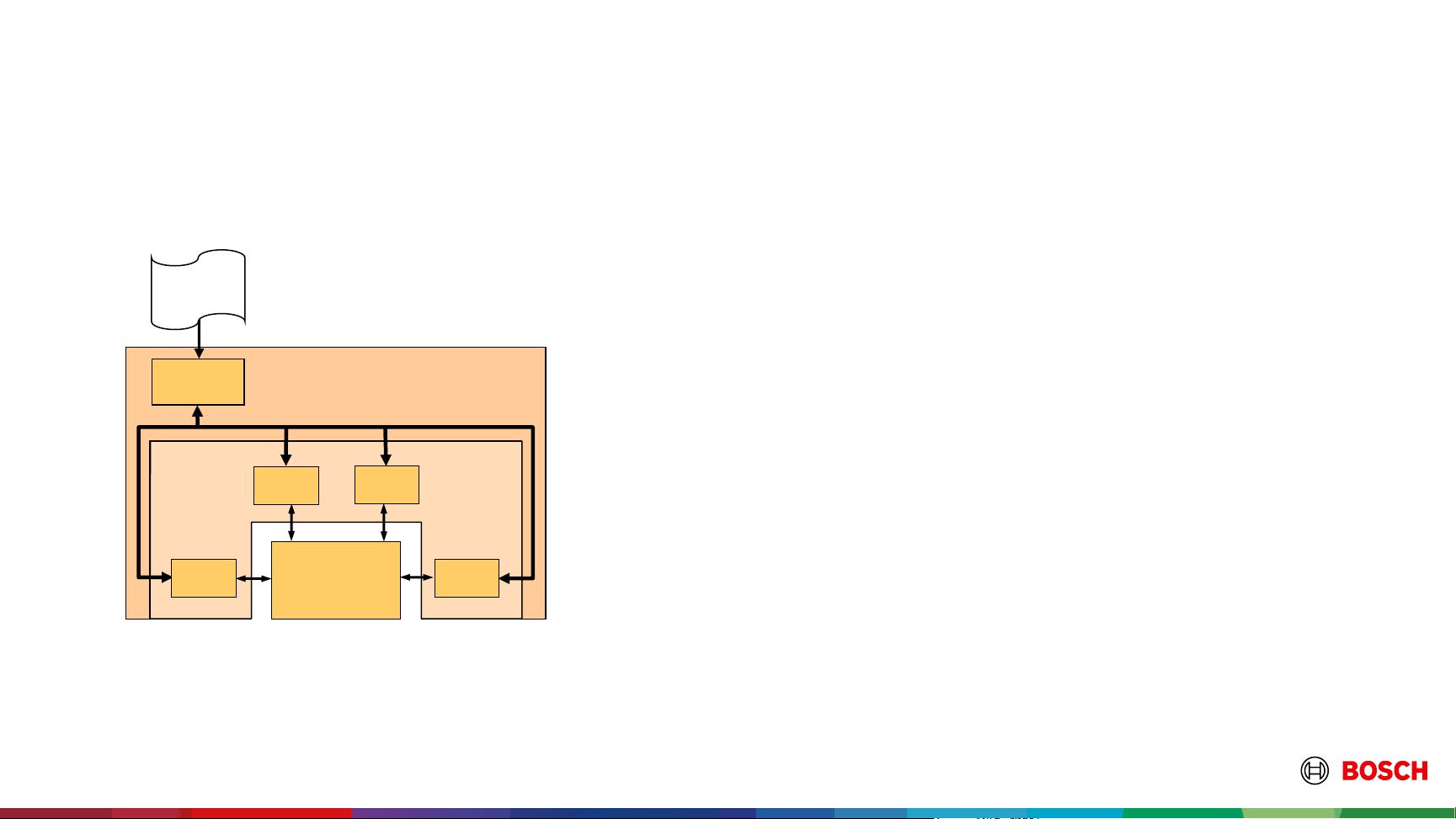

VHDL IFS

▪ Characteristics

− Implemented in VHDL

− 1 TM per interface

− Structural interconnect

to DUT

− Virtual interconnect

between TMs

− Command file

▪ Benefits

− Reusability

− Low implementation

effort

− Smart synchronization

Virtual Interconnect

Testbench

Package

Structural

Interconnect

Command

File

TM3

TM4

TM2

TM1

DUT

Testbench

▪ Disadvantages

▪ Limited random

testing

▪ Limited command

syntax

5