没有合适的资源?快使用搜索试试~ 我知道了~

GS2971A芯片手册

需积分: 50 20 下载量 75 浏览量

2021-07-23

16:56:07

上传

评论 1

收藏 4.52MB PDF 举报

温馨提示

试读

150页

GS2971A_DS datasheet 默认不需驱动,读取寄存器【0x6】的值即可知分辨率

资源推荐

资源详情

资源评论

1 of 150GS2971A 3Gb/s, HD, SD SDI Receiver

Final Data Sheet Rev. 3

GENDOC-054311 July 2013

3Gb/s, HD, SD SDI Receiver, with Integrated Adaptive Cable Equalizer complete

with SMPTE Audio and Video Processing

GS2971A

www.semtech.com

Key Features

• Operation at 2.97Gb/s, 2.97/1.001Gb/s, 1.485Gb/s,

1.485/1.001Gb/s and 270Mb/s

• Supports SMPTE ST 425 (Level A and Level B),

SMPTE ST 424, SMPTE ST 292, SMPTE ST 259-C and

DVB-ASI

• Integrated adaptive cable equalizer

• Typical equalized length of Belden 1694A cable:

150m at 2.97Gb/s

250m at 1.485Gb/s

480m at 270Mb/s

• Integrated Reclocker with low phase noise, integrated

VCO

• Serial digital reclocked, or non-reclocked output

• Integrated audio de-embedder for 8 channels of 48kHz

audio

• Integrated audio clock generator

• Ancillary data extraction

• Optional conversion from SMPTE ST 425 Level B to

Level A for 1080p 50/60 4:2:2 10-bit

• Parallel data bus selectable as either 20-bit or 10-bit

• Comprehensive error detection and correction

features

• Output H, V, F or CEA 861 Timing Signals

• 1.2V digital core power supply, 1.2V and 3.3V analog

power supplies, and selectable 1.8V or 3.3V I/O power

supply

• GSPI Host Interface

• -20ºC to +85ºC operating temperature range

• Low power operation (typically 545mW)

• Small 11mm x 11mm 100-ball BGA package

• Pb-free and RoHS compliant

Applications

HD-SDI

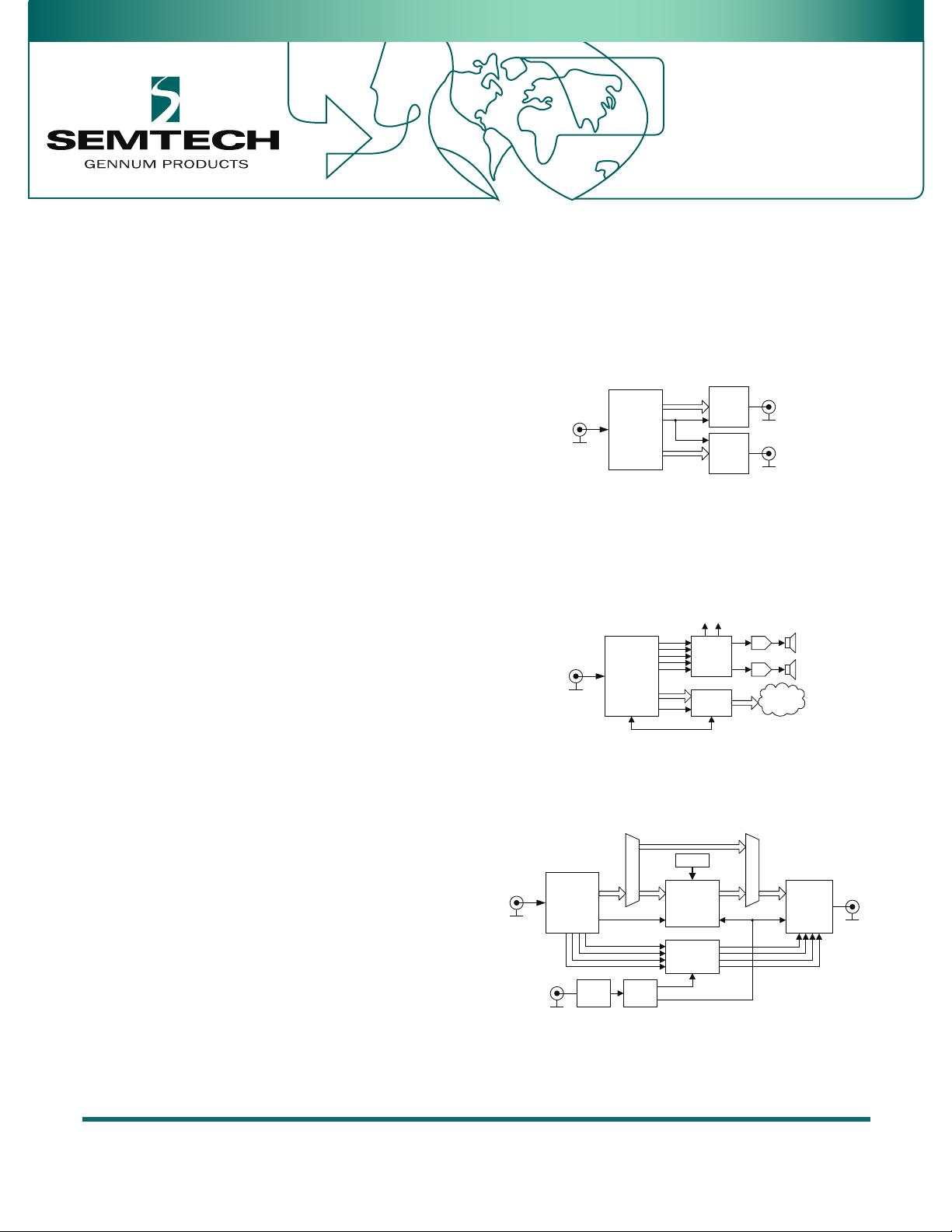

Application: Single Link (3G-SDI)

to Dual Link (HD-SDI) Converter

GS2962/72

Link A

Link B

HV F/PCLK

10-bit

3G-SDI

GS2971A

GS2962/72

10-bit

HV F/PCLK

HD-SDI

Application: 1080p50/60 Monitor

Audio

Selector

Video

Processor

10-bit

HV F/PCLK

CTR L/TIMECODE

AES - OUT

AUDIO 1/2

Audio C locks

Speakers

Display

DAC

DAC

3G-SDI

GS2971A

AUDIO 3/4

AUDIO 5/6

AUDIO 7/8

Application: Multi-format Downconverter

Audio

Processing

& Delay

GS4901

Analog

Sync

Sync

Seperator

10-bit

HV F/PCLK

HD/SD

Serializer

(GS1582,

GS1672)

Video

Downconver ter &

Aspect Ratio

Conversion

Memory

10-bit

10-bit bit SD Bypass

HV F/PCLK

Audio Clocks

AE S 1/2

AE S 3/4

AE S 5/6

AE S 7/8

SD-SDI

SD/HD/3G-SDI

GS2971A

AE S 1/2

AE S 3/4

AE S 5/6

AE S 7/8

GS2971A 3Gb/s, HD, SD SDI Receiver

Final Data Sheet Rev. 3

GENDOC-054311 July 2013

2 of 150

www.semtech.com

Description

The GS2971A is a multi-rate SDI integrated Receiver which

includes complete SMPTE processing, as per SMPTE ST 425,

SMPTE ST 292 and SMPTE ST 259-C. The SMPTE processing

features can be bypassed to support signals with other

coding schemes.

The GS2971A integrates Semtech's adaptive cable equalizer

technology, achieving unprecedented cable lengths and

jitter tolerance. It features DC restoration to compensate for

the DC content of SMPTE pathological signals.

The device features an Integrated Reclocker with an

internal VCO and a wide Input Jitter Tolerance (IJT) of 0.7UI.

A serial digital loop-through output is provided, which can

be configured to output either reclocked or non-reclocked

serial digital data. The serial digital output can be connected

to an external cable driver.

The device operates in one of four basic modes: SMPTE

mode, DVB-ASI mode, Data-Through mode or Standby

mode.

In SMPTE mode (the default operating mode), the GS2971A

performs full SMPTE processing, and features a number of

data integrity checks and measurement capabilities.

The device also supports ancillary data extraction, and can

provide entire ancillary data packets through

host-accessible registers. It also provides a variety of other

packet detection and error handling features. All of these

processing features are optional, and may be individually

enabled or disabled through register programming.

Both SMPTE ST 425 Level A and Level B inputs are

supported with optional conversion from Level B to Level A

for 1080p 50/59.94/60 4:2:2 10-bit inputs.

In DVB-ASI mode, sync word detection, alignment and

8b/10b decoding is applied to the received data stream.

In Data-Through mode all forms of SMPTE and DVB-ASI

processing are disabled, and the device can be used as a

simple serial to parallel converter.

The device can also operate in a lower power Standby

mode. In this mode, no signal processing is carried out and

the parallel output is held static.

Parallel data outputs are provided in 20-bit or 10-bit format

for 3Gb/s, HD and SD video rates, with a variety of mapping

options. As such, this parallel bus can interface directly with

video processor ICs, and output data can be multiplexed

onto 10 bits for a low pin count interface.

Up to eight channels (two audio groups) of serial digital

audio may be extracted from the video data stream, in

accordance with SMPTE ST 272-C and SMPTE ST 299.

The output audio formats supported by the device include

AES/EBU and I

2

S, and two other industry standard serial

digital formats. A variety of audio processing features are

provided to ease implementation. Audio clocks are

internally generated and provided by the device.

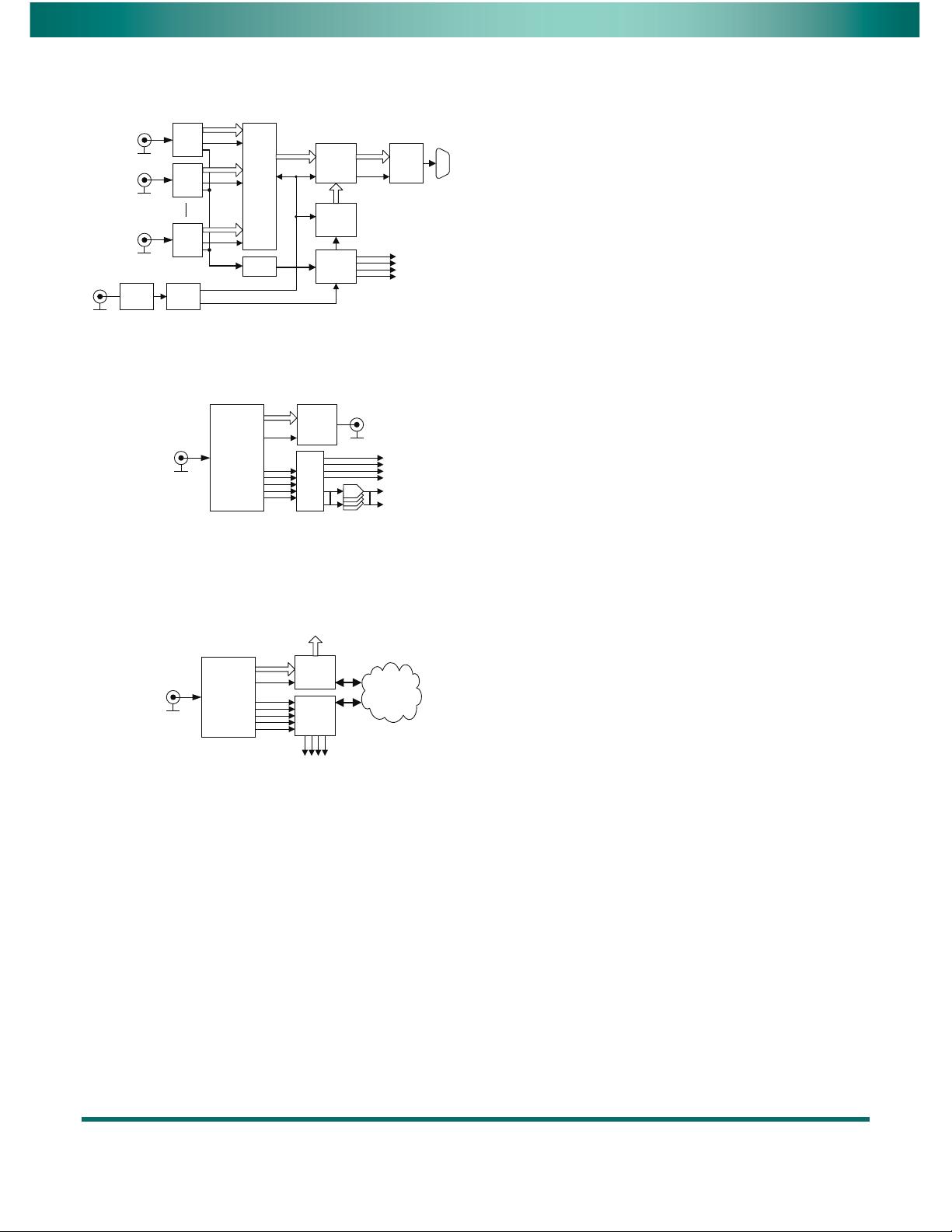

Application: Multi-input Video Monitoring System

GS4911

Analog

Sync

Sync

Seperator

Video

Formatter

Video

Memory

HV F/PCLK

Audio Clock s

10-bit

HV F/PCLK

AE S OUT 1/2

AE S OUT 3/4

AE S OUT 5/6

AE S OUT 7/8

HV F/PCLK

HV F/PCLK

Audio

Select

10-bit

10-bit

On Screen

Display

Generator

AES BUS

Audio

Processor

HV/DE/PCLK

DVI/

VGA DAC

Video

Output

3G-SDI

Input 1

GS2971A

GS2971A

GS2971A

3G-SDI

Input 2

3G-SDI

Input n

Application: Multi-format Audio De-embedder Module

PCLK

10 - bit

GS2962

DAC

Switch

Logic

&

Drivers

Analog

Audio

Outputs

AES

Audio

Outputs

AUDIO 1/2

AUDIO 3/4

AUDIO 5/6

AUDIO 7/8

Audio Clock s

SD/HD/3G-SDI

GS2971A

SD/HD/3G-SDI

Application: Multi-format Digital VTR/Video Server

Stor age :

Tape/ HDD/Sol i d State

Audio

Processor

Video

Processor

10-bit

HVF/PCLK

Audio Out puts

V ideo Out put

Audio Clock s

AUDIO 1/2

AUDIO 3/4

AUDIO 5/6

AUDIO 7/8

SD/HD/3G-SDI

GS2971A

GS2971A 3Gb/s, HD, SD SDI Receiver

Final Data Sheet Rev. 3

GENDOC-054311 July 2013

3 of 150

www.semtech.com

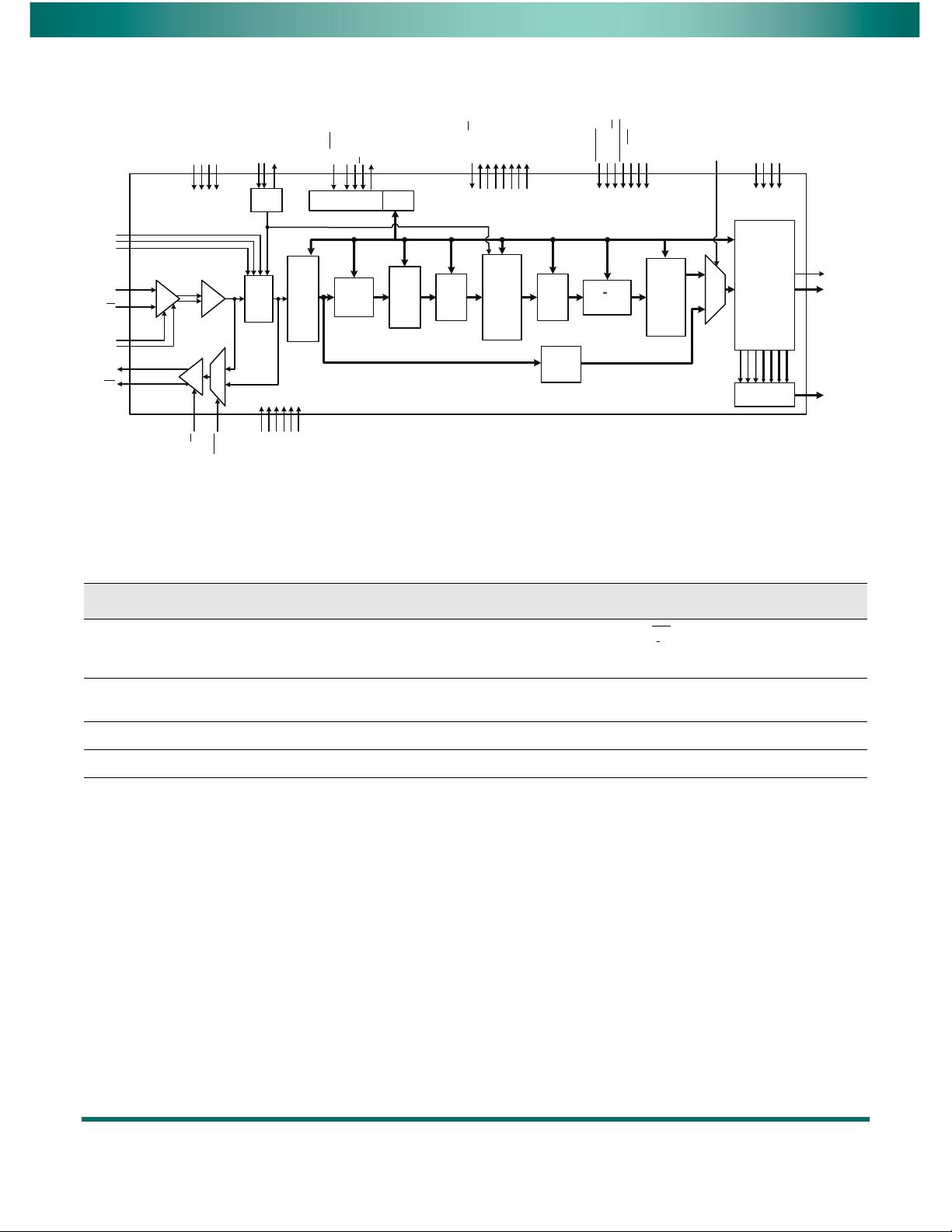

Functional Block Diagram

GS2971A Functional Block Diagram

Revision History

Version ECO PCN Date Changes and/or Modifications

3 014961– August 2013

Clarified IOPROC_EN/DIS

register configuration

throughout Section 4.

Added note to Section 4.20.

Updated SMPTE format throughout document.

2 158578 – September 2012

Added back the Typ column in the Table 2-4: AC

Electrical Characteristics

1 158083 – June 2012 Updates throughout the document

0 154391 – July 2010 New Document

Buffe r Mux

Reclocker

with

Integrated

VCO

SDI

SDO

SDO

Serial

to

Parallel

Converter

Descramble,

Word Align,

Rate Detect

Flywheel

Video

Standard

Detect

TRS

Detect

Timing

Extraction

Mux

DVB-ASI

Decoder

Illegal code

remap,

TRS/

Line Number/

CRS

Insertion,

EDH Packet

Insertion

V/VSync

H/HSync

F/De

Rate_det[1:0]

ANC/

Checksum

/ST 352

Extraction

Audio

De-Embedder,

Audio Clock

Generation

Error Flags

YANC/CANC

LOCKED

DVB_ASI

STANDBY

GSPI and

JTAG Controller

Host

Interface

Output Mux/

Demux

Crystal

Buffer/

Oscillator

LF

LB_CONT

VBG

RC_BYP

I/O Co ntrol

TIM861

20BIT/10BIT

SMPTE_BYPASS

IOPROC_EN/DIS

RESET_TRST

CORE_VDD

CORE_GND

IO_VDD

IO_GND

AUDIO_EN/DIS

AOUT_1/2

ACLK

AMCLK

WCLK

SDO_EN/DIS

CS_TMS

SCLK_TCLK

SDIN_TDI

SDOUT_TDO

JTAG/HOST

XTAL1

SW_EN

VCO_VDD

VCO_GND

PLL_VDD

PLL_GND

EQ_VDD

EQ_GND

A_VDD

A_GND

BUFF_VDD

BUFF_GND

Buffe r

SDI

AOUT_3/4

AOUT_5/6

AOUT_7/8

XTAL2

XTAL_OUT

SMPTE ST 425

1080p 50/60

4:2:2 10-bit

Level B Level A

EQ

AGCP

AGCN

DOUT[19:0]

PCLK

LOCKED

GS2971A 3Gb/s, HD, SD SDI Receiver

Final Data Sheet Rev. 3

GENDOC-054311 July 2013

4 of 150

www.semtech.com

Contents

1. Pin Out...............................................................................................................................................................9

1.1 Pin Assignment ..................................................................................................................................9

1.2 Pin Descriptions ................................................................................................................................9

2. Electrical Characteristics ......................................................................................................................... 16

2.1 Absolute Maximum Ratings ....................................................................................................... 16

2.2 Recommended Operating Conditions .................................................................................... 16

2.3 DC Electrical Characteristics ..................................................................................................... 17

2.4 AC Electrical Characteristics ..................................................................................................... 19

3. Input/Output Circuits ............................................................................................................................... 25

4. Detailed Description.................................................................................................................................. 28

4.1 Functional Overview .................................................................................................................... 28

4.2 SMPTE ST 425 Mapping - 3G Level A and Level B Formats ............................................. 29

4.2.1 Level A Mapping................................................................................................................ 29

4.2.2 Level B Mapping ................................................................................................................ 29

4.3 Serial Digital Input ........................................................................................................................ 30

4.3.1 Integrated Adaptive Cable Equalizer.......................................................................... 30

4.4 Serial Digital Loop-Through Output ........................................................................................ 31

4.5 Serial Digital Reclocker ............................................................................................................... 32

4.5.1 PLL Loop Bandwidth ........................................................................................................32

4.6 External Crystal / Reference Clock .........................................................................................33

4.7 Lock Detect ...................................................................................................................................... 34

4.7.1 Asynchronous Lock .......................................................................................................... 35

4.7.2 Signal Interruption............................................................................................................ 35

4.8 SMPTE Functionality .................................................................................................................... 35

4.8.1 Descrambling and Word Alignment ........................................................................... 35

4.9 Parallel Data Outputs ................................................................................................................... 36

4.9.1 Parallel Data Bus Buffers.................................................................................................36

4.9.2 Parallel Output in SMPTE Mode ................................................................................... 39

4.9.3 Parallel Output in DVB-ASI Mode ............................................................................... 39

4.9.4 Parallel Output in Data-Through Mode ..................................................................... 39

4.9.5 Parallel Output Clock (PCLK)......................................................................................... 39

4.9.6 DDR Parallel Clock Timing ............................................................................................. 40

4.10 Timing Signal Generator ........................................................................................................... 42

4.10.1 Manual Switch Line Lock Handling.......................................................................... 43

4.10.2 Automatic Switch Line Lock Handling .................................................................... 44

4.10.3 Switch Line Lock Handling During Level B to Level A Conversion ............... 44

4.11 Programmable Multi-function Outputs ............................................................................... 47

4.12 H:V:F Timing Signal Generation ............................................................................................47

4.12.1 CEA-861 Timing Generation ....................................................................................... 49

4.13 Automatic Video Standards Detection ................................................................................ 56

4.13.1 2K Support......................................................................................................................... 60

4.14 Data Format Detection & Indication ..................................................................................... 60

4.15 EDH Detection .............................................................................................................................. 61

GS2971A 3Gb/s, HD, SD SDI Receiver

Final Data Sheet Rev. 3

GENDOC-054311 July 2013

5 of 150

www.semtech.com

4.15.1 EDH Packet Detection ................................................................................................... 61

4.15.2 EDH Flag Detection ........................................................................................................ 62

4.16 Video Signal Error Detection & Indication ......................................................................... 62

4.16.1 TRS Error Detection........................................................................................................ 64

4.16.2 Line Based CRC Error Detection ................................................................................ 64

4.16.3 EDH CRC Error Detection............................................................................................. 65

4.16.4 HD & 3G Line Number Error Detection ................................................................... 65

4.17 Ancillary Data Detection & Indication ................................................................................. 65

4.17.1 Programmable Ancillary Data Detection................................................................ 67

4.17.2 SMPTE ST 352 Payload Identifier............................................................................... 68

4.17.3 Ancillary Data Checksum Error ................................................................................. 69

4.17.4 Video Standard Error.....................................................................................................70

4.18 Signal Processing ......................................................................................................................... 71

4.18.1 TRS Correction & Insertion........................................................................................... 72

4.18.2 Line Based CRC Correction & Insertion ................................................................... 72

4.18.3 Line Number Error Correction & Insertion ............................................................. 72

4.18.4 ANC Data Checksum Error Correction & Insertion ............................................. 73

4.18.5 EDH CRC Correction & Insertion ............................................................................... 73

4.18.6 Illegal Word Re-mapping ............................................................................................. 73

4.18.7 TRS and Ancillary Data Preamble Remapping...................................................... 73

4.18.8 Ancillary Data Extraction............................................................................................. 74

4.18.9 Level B to Level A Conversion .................................................................................... 78

4.19 Audio De-embedder ................................................................................................................... 79

4.19.1 Serial Audio Data I/O Signals...................................................................................... 79

4.19.2 Serial Audio Data Format Support ............................................................................ 81

4.19.3 Audio Processing............................................................................................................. 85

4.19.4 Error Reporting ................................................................................................................ 92

4.20 GSPI - HOST Interface ................................................................................................................ 93

4.20.1 Command Word Description...................................................................................... 94

4.20.2 Data Read or Write Access........................................................................................... 94

4.20.3 GSPI Timing....................................................................................................................... 95

4.21 Host Interface Register Maps .................................................................................................. 97

4.21.1 Video Core Registers ...................................................................................................... 97

4.21.2 SD Audio Core Registers.............................................................................................111

4.21.3 HD and 3G Audio Core Registers............................................................................. 126

4.22 JTAG Test Operation ................................................................................................................141

4.23 Device Power-up .......................................................................................................................143

4.24 Device Reset ................................................................................................................................143

4.25 Standby Mode ............................................................................................................................ 143

5. Application Reference Design ............................................................................................................. 144

5.1 High Gain Adaptive Cable Equalizers ..................................................................................144

5.2 PCB Layout ..................................................................................................................................... 144

5.3 Typical Application Circuit ...................................................................................................... 145

6. References & Relevant Standards ....................................................................................................... 146

剩余149页未读,继续阅读

资源评论

悠哉无忧

- 粉丝: 1890

- 资源: 43

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功