5

SN65DSI86-Q1

www.ti.com.cn

ZHCSDD1A –JULY 2014–REVISED DECEMBER 2015

Copyright © 2014–2015, Texas Instruments Incorporated

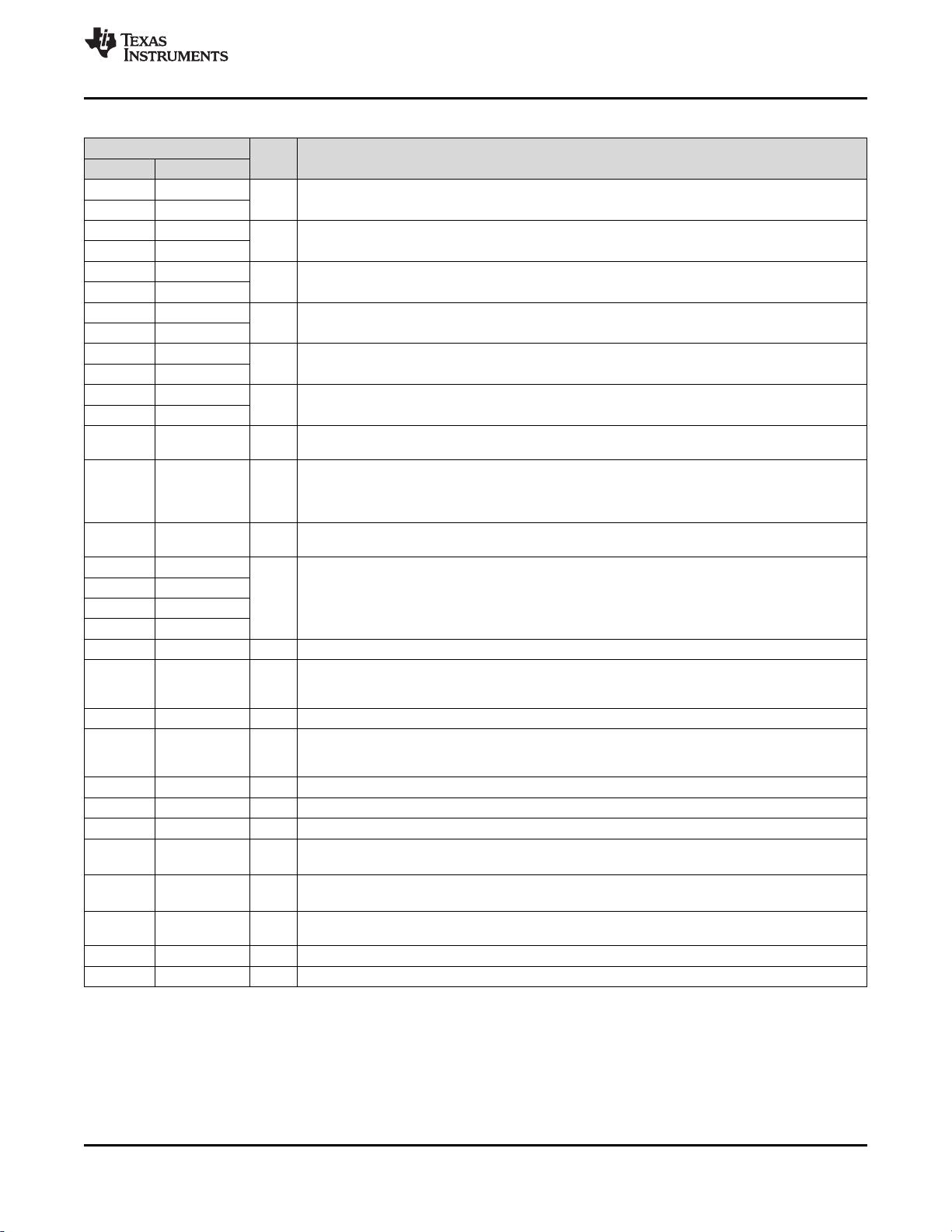

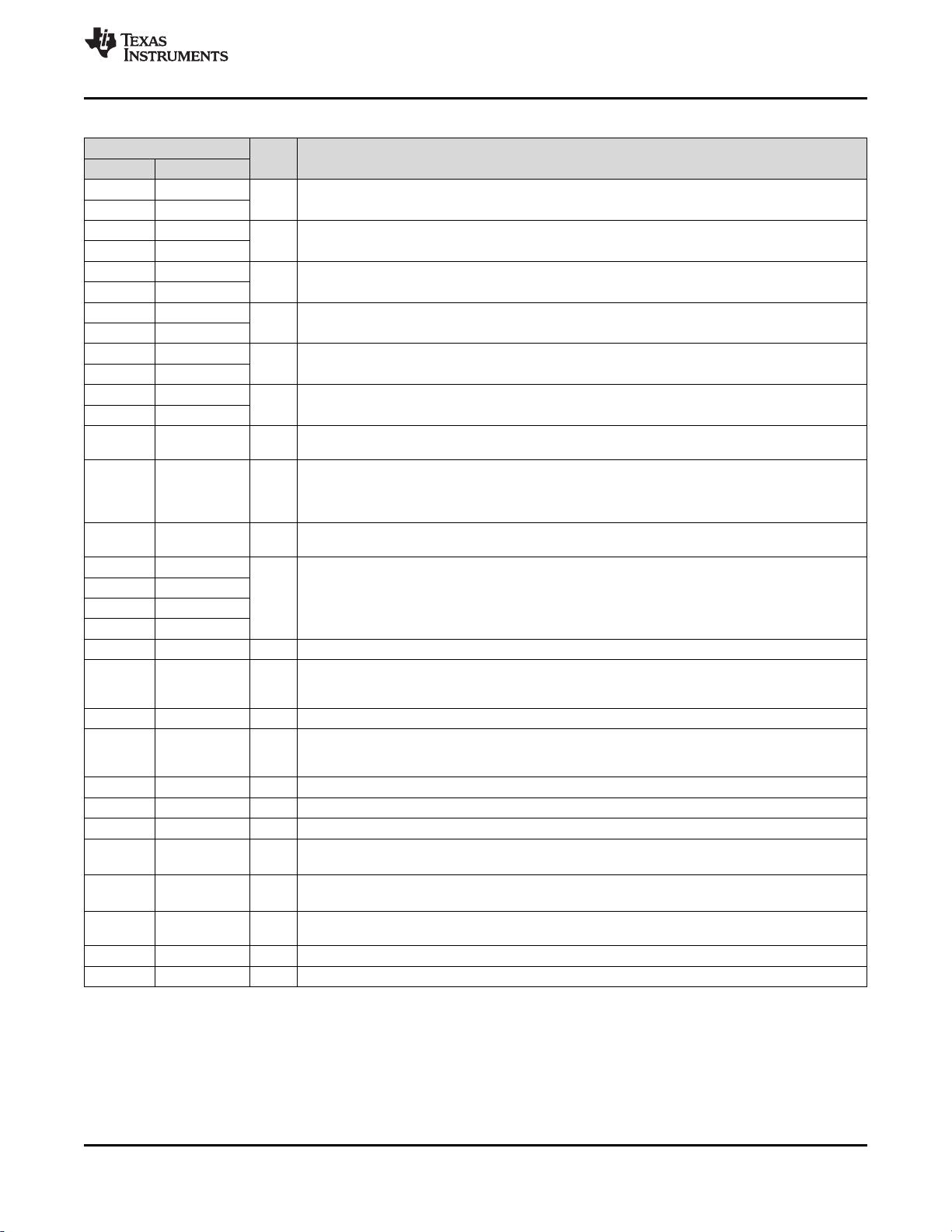

Pin Functions (continued)

PIN

TYPE DESCRIPTION

NAME NO.

DB3P 12

I MIPI D-PHY Channel B Data Lane 3; data rate up to 1.5 Gbps.

DB3N 13

ML0P 37

O

DisplayPort Lane 0 transmit differential pair. Supports 1.62Gbps, 2.16Gbps, 2.43Gbps, 2.7Gbps,

3.24Gbps, 4.32Gbps, and 5.4Gbps. All DisplayPort lanes transmit at the same data rate.

ML0N 38

ML1P 39

O

DisplayPort Lane 1 transmit differential pair. Supports 1.62Gbps, 2.16Gbps, 2.43Gbps, 2.7Gbps,

3.24Gbps, 4.32Gbps, and 5.4Gbps. All DisplayPort lanes transmit at the same data rate.

ML1N 40

ML2P 44

O

DisplayPort Lane 2 transmit differential pair. Supports 1.62Gbps, 2.16Gbps, 2.43Gbps, 2.7Gbps,

3.24Gbps, 4.32Gbps, and 5.4Gbps. All DisplayPort lanes transmit at the same data rate.

ML2N 45

ML3P 46

O

DisplayPort Lane 3 transmit differential pair. Supports 1.62Gbps, 2.16Gbps, 2.43Gbps, 2.7Gbps,

3.24Gbps, 4.32Gbps, and 5.4Gbps. All DisplayPort lanes transmit at the same data rate.

ML3N 47

AUXP 34

I/O Aux Channel Differential Pair.

AUXN 35

TEST1 60 I PD

Test Mode. When high, the SN65DSIx6 enters Test Mode. This pin should be left unconnected or

tied to ground for normal operation.

TEST2 55 I/O PD

Used for internal test, HBR2 Compliance Eye, and Symbol Error Rate Measurement pattern. For

normal operation, this pin should be pull-down to ground or left unconnected. Refer to DP Training

and Compliance patterns for information on HBR2 Compliance Eye and Symbol Error Rate

Measurement patterns.

TEST3 50 I

Used for Texas Instruments internal use only. This pin must be left unconnected or tied to ground

through a 0.1µF capacitor.

GPIO1 58

I/O

General Purpose I/O. Refer to General Purpose Input and Outputs for details on GPIO functionality.

When these pins are set high, they should be tied to the same 1.8V power rail where SN65DSIx6

VCCIO 1.8V power rail is connected.

GPIO2 56

GPIO3 54

GPIO4 57

HPD 32 I PD HPD Input. This input requires an 51K 1% series resistor.

ADDR 1 I

Local I2C Interface Target Address Select. In normal operation, this pin is an input. When the ADDR

pin is programmed high, it should be tied to the same 1.8V power rails where the SN65DSIx6 VCCIO

1.8V power rail is connected.

EN 2 I PU Chip Enable and Reset. Device is reset (shutdown) when EN is low.

REFCLK 51 I

REFCLK. Frequency determined by value programmed in I2C register or value of GPIO[3:1] latched

at rising edge of EN. Supported frequencies are: 12MHz, 19.2MHz, 26MHz, 27MHz, and 38.4MHz.

This pin must be tied to or pulled down to ground when DACP/N feeds the DisplayPort PLL.

SCL 15 I Local I2C Interface Clock

SDA 16 I/O Local I2C Interface Data

IRQ 61 O Interrupt Signal

GND

23, 26, 52, 64,

Thermal pad

G Reference Ground

VCCA

3, 14, 18, 31,

36, 41, 43, 48

P

1.2V Power Supply for Analog Circuits.

VCCA and VCC must be applied simultaneously.

VCC

17, 33, 49, 59,

62

P 1.2V Power Supply for digital core

VPLL 42 P 1.8V Power Supply for DisplayPort PLL

VCCIO 53, 63 P 1.8V Power Supply for Digital I/O.

qq_335607272023-02-15#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整

qq_335607272023-02-15#完美解决问题 #运行顺畅 #内容详尽 #全网独家 #注释完整 我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功