没有合适的资源?快使用搜索试试~ 我知道了~

TI-LMK61E08.pdf

需积分: 9 0 下载量 134 浏览量

2022-11-30

22:55:11

上传

评论 4

收藏 1.36MB PDF 举报

温馨提示

试读

54页

TI-LMK61E08.pdf

资源详情

资源评论

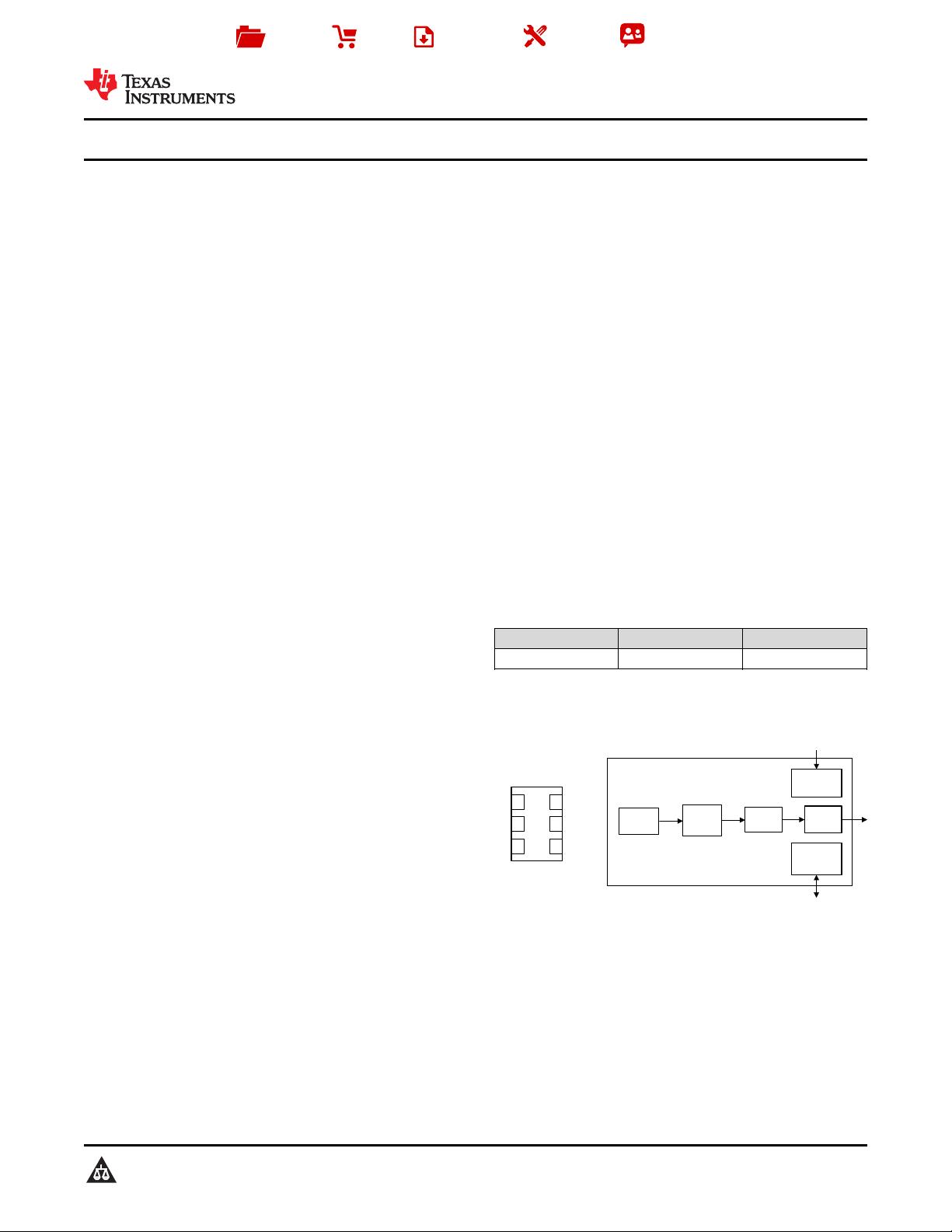

SCL OUTN

VDDSDA

GND OUTP

1 6

2 5

43

LMK61E0X

Ultra-high performance oscillator

PLL

Output

Divider

Output

Buffer

Power

Conditioning

Interface

I

2

C/EEPROM

Integrated

Oscillator

Copyright © 2016, Texas Instruments Incorporated

Product

Folder

Order

Now

Technical

Documents

Tools &

Software

Support &

Community

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

LMK61E08

SNAS805 –JUNE 2020

LMK61E08 Ultra-Low Jitter Programmable Oscillator With Internal EEPROM

1

1 Features

1

• Ultra-Low Noise, High Performance

– Jitter: 90-fs RMS Typical f

OUT

> 100 MHz on

LMK61E08

– PSRR: –70 dBc, Robust Supply Noise

Immunity on LMK61E08

• Flexible Output Format on LMK61E08

– LVPECL up to 1 GHz

– LVDS up to 900 MHz

– HCSL up to 400 MHz

• Total Frequency Tolerance of ±25 ppm

• System Level Features

– Glitch-Less Frequency Margining: Up to ±1000

ppm From Nominal

– Internal EEPROM: User Configurable Start-Up

Settings

• Other Features

– Device Control: Fast Mode I

2

C up to 1000 kHz

– 3.3-V Operating Voltage

– Industrial Temperature Range (–40ºC to

+85ºC)

– 7-mm × 5-mm 6-Pin Package

• Default Frequency:

– 70.656 MHz

2 Applications

• High-Performance Replacement for Crystal, SAW,

or Silicon-Based Oscillators

• Switches, Routers, Network Line Cards, Base

Band Units (BBU), Servers, Storage/SAN

• Test and Measurement

• Medical Imaging

• FPGA, Processor Attach

• xDSL, Broadcast Video

3 Description

The LMK61E08 family of ultra-low jitter PLLatinum™

programmable oscillators uses fractional-N frequency

synthesizers with integrated VCOs to generate

commonly used reference clocks. The output on

LMK61E08 can be configured as LVPECL, LVDS, or

HCSL. The device features self-start-up from on-chip

EEPROM to generate a factory-programmed default

output frequency, or the device registers and

EEPROM settings are fully programmable in-system

through an I

2

C serial interface. The device provides

fine and coarse frequency margining control through

an I

2

C serial interface, making it a digitally-controlled

oscillator (DCXO).

The PLL feedback divider can be updated to adjust

the output frequency without spikes or glitches in

steps of <1ppb using a PFD of 12.5 MHz (R

divider=4, doubler disabled) for compatibility with

xDSL requirements, or in steps of <5.2 ppb using a

PFD of 100 MHz (R divider=1, doubler enabled) for

compatibility with broadcast video requirements. The

frequency margining features also facilitate system

design verification tests (DVT), such as standards

compliance and system timing margin testing.

Device Information

(1)

PART NUMBER PACKAGE BODY SIZE (NOM)

LMK61E08 QFM (6) 7.00 mm × 5.00 mm

(1) For all available packages, see the orderable addendum at

the end of the data sheet.

Pinout and Simplified Block Diagram

2

LMK61E08

SNAS805 –JUNE 2020

www.ti.com

Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated

Table of Contents

1 Features.................................................................. 1

2 Applications ........................................................... 1

3 Description ............................................................. 1

4 Revision History..................................................... 2

5 Pin Configuration and Functions......................... 3

6 Specifications......................................................... 4

6.1 Absolute Maximum Ratings ...................................... 4

6.2 ESD Ratings ............................................................ 4

6.3 Recommended Operating Conditions....................... 4

6.4 Thermal Information.................................................. 4

6.5 Electrical Characteristics - Power Supply ................. 5

6.6 LVPECL Output Characteristics................................ 5

6.7 LVDS Output Characteristics .................................... 5

6.8 HCSL Output Characteristics.................................... 5

6.9 Frequency Tolerance Characteristics ....................... 6

6.10 Frequency Margining Characteristics ..................... 6

6.11 Power-On Reset Characteristics (VDD).................. 6

6.12 I

2

C-Compatible Interface Characteristics (SDA,

SCL)........................................................................... 6

6.13 PSRR Characteristics ............................................. 7

6.14 Other Characteristics .............................................. 7

6.15 PLL Clock Output Jitter Characteristics .................. 7

6.16 Typical 156.25-MHz Output Phase Noise

Characteristics ........................................................... 8

6.17 Typical 161.1328125 MHz Output Phase Noise

Characteristics ........................................................... 8

6.18 Additional Reliability and Qualification.................... 8

6.19 Typical Characteristics............................................ 9

7 Parameter Measurement Information ................ 13

7.1 Device Output Configurations ................................. 13

8 Detailed Description............................................ 15

8.1 Overview ................................................................. 15

8.2 Functional Block Diagram ....................................... 15

8.3 Feature Description................................................. 16

8.4 Device Functional Modes........................................ 19

8.5 Programming........................................................... 22

8.6 Register Maps......................................................... 26

9 Application and Implementation ........................ 39

9.1 Application Information............................................ 39

9.2 Typical Application .................................................. 39

10 Power Supply Recommendations ..................... 43

11 Layout................................................................... 43

11.1 Layout Guidelines ................................................. 43

11.2 Layout Example .................................................... 44

12 Device and Documentation Support ................. 45

12.1 Documentation Support ....................................... 45

12.2 Receiving Notification of Documentation Updates 45

12.3 Support Resources ............................................... 45

12.4 Trademarks........................................................... 45

12.5 Electrostatic Discharge Caution............................ 45

12.6 Glossary................................................................ 45

13 Mechanical, Packaging, and Orderable

Information ........................................................... 45

13.1 Package Option Addendum.................................. 46

4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

DATE VERSION NOTES

June 2020 * Initial release.

SCL OUTN

VDDSDA

GND OUTP

1 6

2 5

43

3

LMK61E08

www.ti.com

SNAS805 –JUNE 2020

Submit Documentation FeedbackCopyright © 2020, Texas Instruments Incorporated

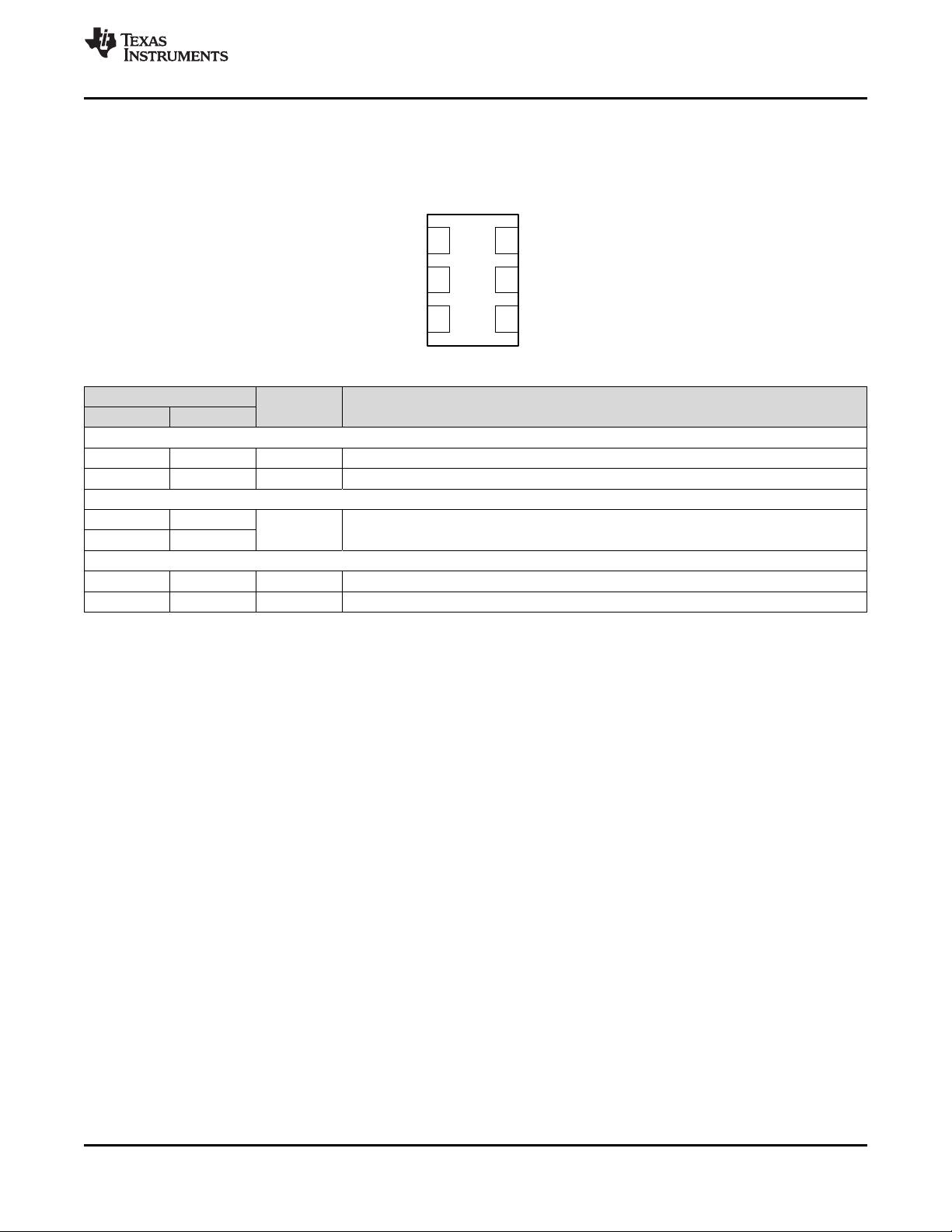

5 Pin Configuration and Functions

SIA Package

6-Pin QFM

Top View

Pin Functions

PIN

I/O DESCRIPTION

NAME NO.

POWER

GND 3 Ground Device Ground.

VDD 6 Power 3.3-V Power Supply.

OUTPUT BLOCK

OUTP 4

Output Differential Output Pair (LVPECL, LVDS, or HCSL).

OUTN 5

DIGITAL CONTROL / INTERFACES

SCL 2 LVCMOS I

2

C Serial Clock (open-drain). Requires an external pullup resistor to VDD.

SDA 1 LVCMOS I

2

C Serial Data (bidirectional, open-drain). Requires an external pullup resistor to VDD.

4

LMK61E08

SNAS805 –JUNE 2020

www.ti.com

Submit Documentation Feedback Copyright © 2020, Texas Instruments Incorporated

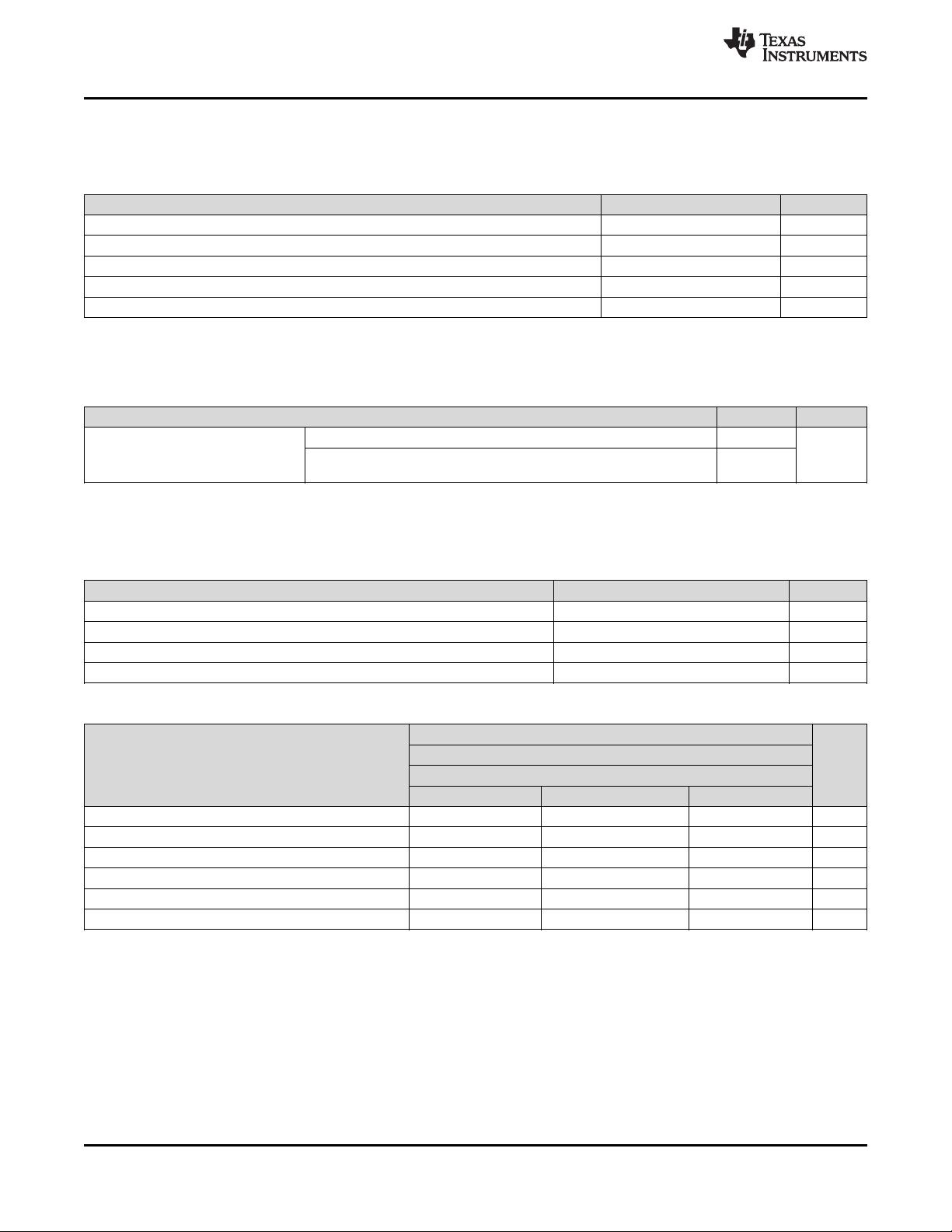

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings

only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended

Operating Conditions. Exposure to absolute maximum-rated conditions for extended periods may affect device reliability.

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)

(1)

MIN MAX UNIT

VDD Device supply voltage –0.3 3.6 V

V

IN

Input voltage for logic inputs –0.3 VDD + 0.3 V

V

OUT

Output voltage for clock outputs –0.3 VDD + 0.3 V

T

J

Junction temperature 150 °C

T

STG

Storage temperature –40 125 °C

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

6.2 ESD Ratings

VALUE UNIT

V

(ESD)

Electrostatic discharge

Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001

(1)

±2000

V

Charged-device model (CDM), per JEDEC specification JESD22-

C101

(2)

±500

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

MIN NOM MAX UNIT

VDD Device supply voltage 3.135 3.3 3.465 V

T

A

Ambient temperature –40 25 85 °C

T

J

Junction temperature 115 °C

t

RAMP

VDD power-up ramp time 0.1 100 ms

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

report.

(2) The package thermal resistance is calculated on a 4-layer JEDEC board.

(3) Connected to GND with 3 thermal vias (0.3-mm diameter).

(4) ψ

JB

(junction-to-board) is used when the main heat flow is from the junction to the GND pad. See Layout Guidelines for more information

on ensuring good system reliability and quality.

6.4 Thermal Information

THERMAL METRIC

(1)

LMK61E08

(2) (3) (4)

UNIT

SIA (QFM)

8 PINS

Airflow (LFM) 0 Airflow (LFM) 200 Airflow (LFM) 400

R

θJA

Junction-to-ambient thermal resistance 54 44 41.2 °C/W

R

θJC(top)

Junction-to-case (top) thermal resistance 34 n/a n/a °C/W

R

θJB

Junction-to-board thermal resistance 36.7 n/a n/a °C/W

ψ

JT

Junction-to-top characterization parameter 11.2 16.9 21.9 °C/W

ψ

JB

Junction-to-board characterization parameter 36.7 37.8 38.9 °C/W

R

θJC(bot)

Junction-to-case (bottom) thermal resistance n/a n/a n/a °C/W

5

LMK61E08

www.ti.com

SNAS805 –JUNE 2020

Submit Documentation FeedbackCopyright © 2020, Texas Instruments Incorporated

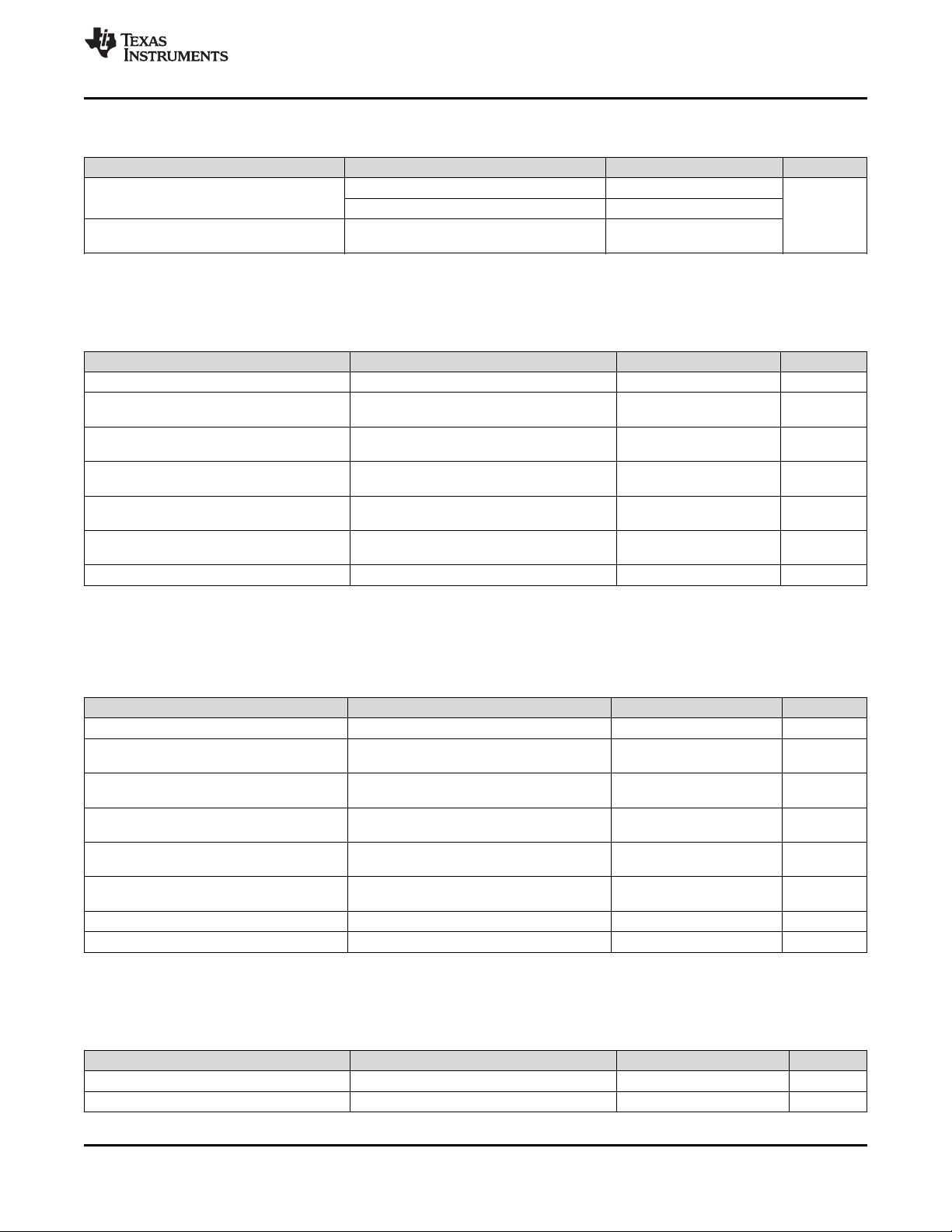

(1) Refer to Parameter Measurement Information for relevant test conditions.

(2) On-chip power dissipation should exclude 40 mW, dissipated in the 150-Ω termination resistors, from total power dissipation.

6.5 Electrical Characteristics - Power Supply

(1)

VDD = 3.3 V ± 5%, T

A

= –40°C to 85°C

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

IDD Device current consumption LVPECL

(2)

162 208

mA

HCSL 155 196

IDD-PD Device current consumption

when output is disabled

120

(1) Refer to Parameter Measurement Information for relevant test conditions.

(2) An output frequency over f

OUT

maximum spec is possible, but output swing may be less than V

OD

minimum spec.

(3) Ensured by characterization.

6.6 LVPECL Output Characteristics

(1)

VDD = 3.3 V ± 5%, T

A

= –40C to 85°C

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

f

OUT

Output frequency

(2)

10 1000 MHz

V

OD

Output voltage swing

(V

OH

- V

OL

)

(2)

700 800 1200 mV

V

OUT, DIFF, PP

Differential output peak-to-

peak swing

2 x

|V

OD

|

V

V

OS

Output common-mode voltage VDD –

1.55

V

t

R

/ t

F

Output rise/fall time (20% to

80%)

(3)

120 200 ps

PN-Floor Output phase noise floor

(f

OFFSET

> 10 MHz)

156.25 MHz

–165

dBc/Hz

ODC Output duty cycle

(3)

45% 55%

(1) An output frequency over f

OUT

max spec is possible, but output swing may be less than V

OD

min spec.

(2) Ensured by characterization.

6.7 LVDS Output Characteristics

(1)

VDD = 3.3 V ± 5%, T

A

= –40°C to 85°C

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

f

OUT

Output Frequency

(1)

10 900 MHz

V

OD

Output Voltage Swing

(V

OH

- V

OL

)

(1)

300 390 480 mV

V

OUT, DIFF, PP

Differential Output Peak-to-

Peak Swing

2 x

|V

OD

|

V

V

OS

Output Common Mode

Voltage

1.2 V

t

R

/ t

F

Output Rise/Fall Time (20% to

80%)

(2)

150 250 ps

PN-Floor Output Phase Noise Floor

(f

OFFSET

> 10 MHz)

156.25 MHz

–162 dBc/Hz

ODC Output Duty Cycle

(2)

45% 55%

R

OUT

Differential Output Impedance 125 Ω

(1) Refer to Parameter Measurement Information for relevant test conditions.

6.8 HCSL Output Characteristics

(1)

VDD = 3.3 V ± 5%, T

A

= –40°C to 85°C

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

f

OUT

Output frequency 10 400 MHz

V

OH

Output high voltage 600 850 mV

剩余53页未读,继续阅读

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0

最新资源