没有合适的资源?快使用搜索试试~ 我知道了~

TI-BQ24105-Q1.pdf

需积分: 8 1 下载量 3 浏览量

2022-10-29

19:59:30

上传

评论 5

收藏 1.44MB PDF 举报

温馨提示

试读

38页

TI-BQ24105-Q1.pdf

资源详情

资源评论

资源推荐

STAT1

IN

IN

PG

VCC

TTC

ISET1

ISET2

STAT2

PGND

PGND

CE

SNS

BAT

FB

TS

OUT

OUT

VTSB

VSS

20

1

11

10

2

3

4

5

6

7

8

9

19

18

17

16

15

14

13

12

bq24105-Q1

www.ti.com

SLUS953A –AUGUST 2009–REVISED APRIL 2012

SYNCHRONOUS SWITCHMODE, LI-ION AND LI-POLYMER CHARGE-MANAGEMENT

IC WITH INTEGRATED POWER FETs ( bqSWITCHER™)

Check for Samples: bq24105-Q1

1

FEATURES

DESCRIPTION

The bqSWITCHER™ series are highly integrated Li-

23

• Qualified for Automotive Applications

ion and Li-polymer switch-mode charge management

• Ideal For Highly Efficient Charger Designs For

devices targeted at a wide range of portable

Single-, Two-, or Three-Cell Li-Ion and Li-

applications. The bqSWITCHER™ series offers

Polymer Battery Packs

integrated synchronous PWM controller and power

FETs, high-accuracy current and voltage regulation,

• Also for LiFePO

4

Battery (see Using bq24105

charge preconditioning, charge status, and charge

to Charge LiFePO4 Battery)

termination, in a small, thermally enhanced QFN

• Integrated Synchronous Fixed-Frequency

package.

PWM Controller Operating at 1.1 MHz

The bqSWITCHER charges the battery in three

With 0% to 100% Duty Cycle

phases: conditioning, constant current, and constant

• Integrated Power FETs For Up To 2-A Charge

voltage. Charge is terminated based on user-

Rate

selectable minimum current level. A programmable

• High-Accuracy Voltage and Current Regulation

charge timer provides a safety backup for charge

termination. The bqSWITCHER automatically restarts

• Stand-Alone (Built-In Charge Management and

the charge cycle if the battery voltage falls below an

Control) Version

internal threshold. The bqSWITCHER automatically

• Status Outputs For LED or Host Processor

enters sleep mode when V

CC

supply is removed.

Interface Indicates Charge-In-Progress, Charge

Completion, Fault, and AC-Adapter Present

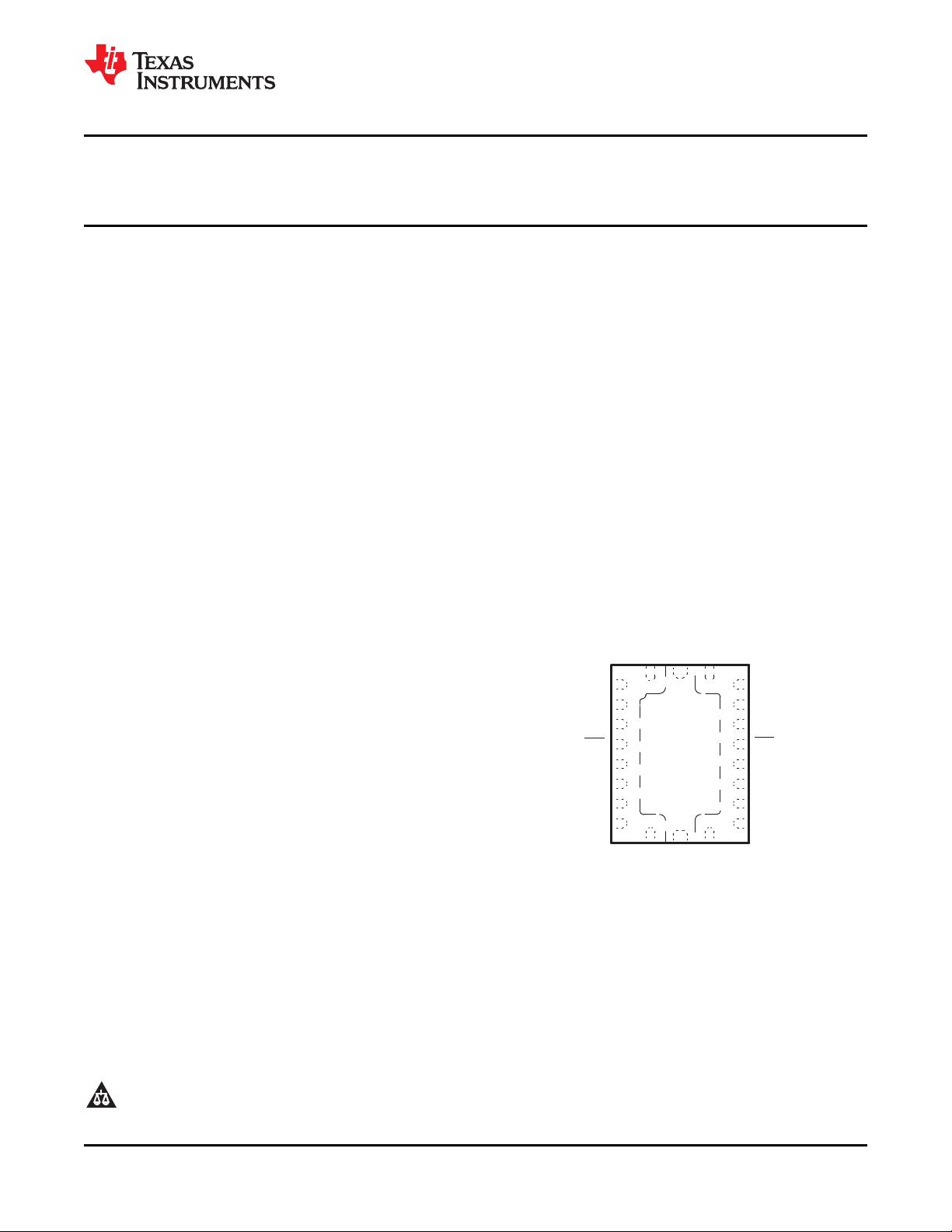

RHL PACKAGE

Conditions

(TOP VIEW)

• 20-V Maximum Voltage Rating on IN and OUT

Pins

• High-Side Battery Current Sensing

• Battery Temperature Monitoring

• Automatic Sleep Mode for Low Power

Consumption

• Reverse Leakage Protection Prevents Battery

Drainage

• Thermal Shutdown and Protection

• Built-In Battery Detection

• Available in 20-Pin, 3.5 mm × 4.5 mm, QFN

Package

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2bqSWITCHER, PowerPAD are trademarks of Texas Instruments.

3All other trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Copyright © 2009–2012, Texas Instruments Incorporated

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

bq24105-Q1

SLUS953A –AUGUST 2009–REVISED APRIL 2012

www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with

appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more

susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

ORDERING INFORMATION

(1)

T

A

PACKAGE

(2)

ORDERABLE PART NUMBER TOP-SIDE MARKING

–40°C to 85°C QFN – RHL Reel of 3000 BQ24105IRHLRQ1 BQ24105

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI

web site at www.ti.com.

(2) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

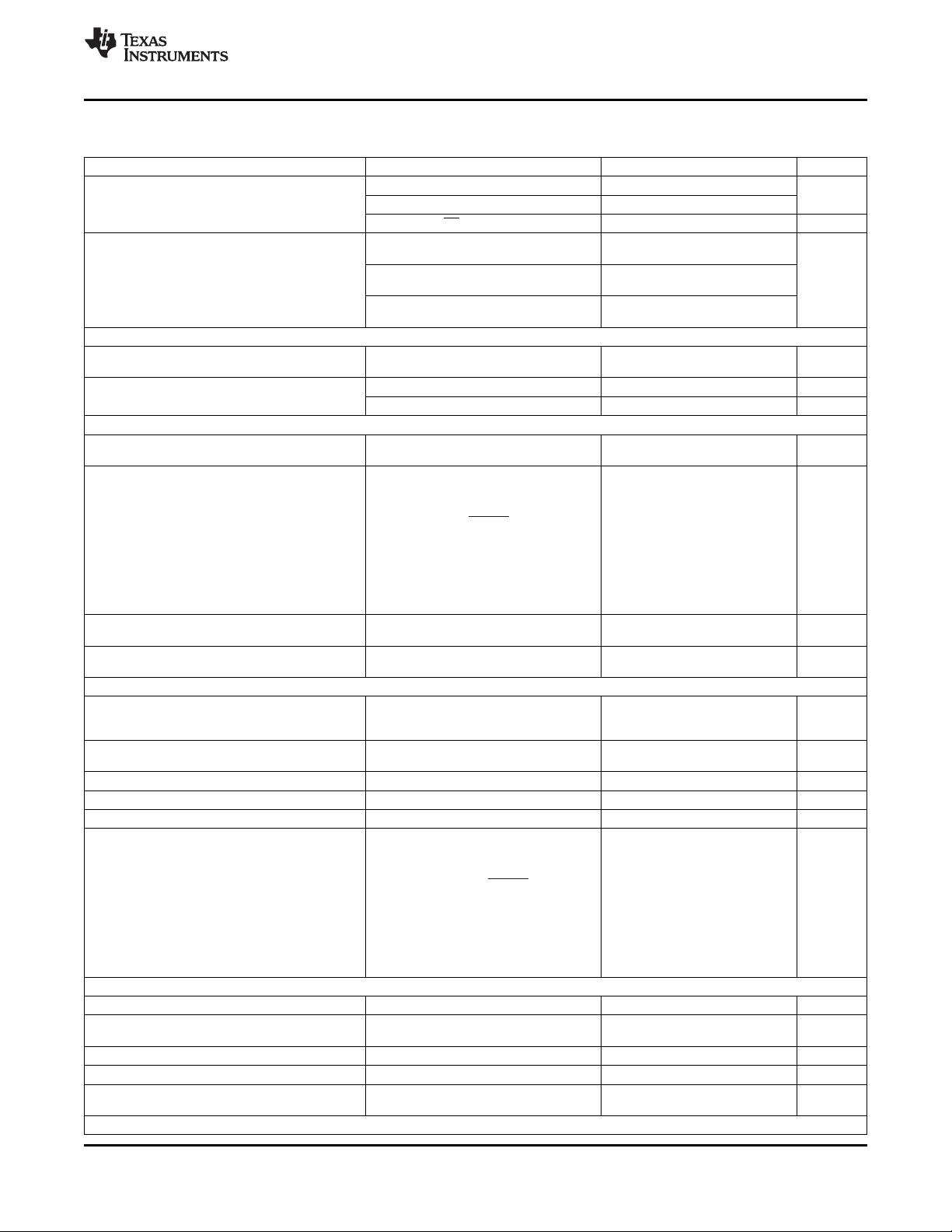

ABSOLUTE MAXIMUM RATINGS

(1)

over operating free-air temperature range (unless otherwise noted)

Supply voltage range (with respect to V

SS

) IN, VCC 20 V

STAT1, STAT2, PG, CE, SNS, BAT –0.3 V to 20 V

OUT –0.7 V to 20 V

Input voltage range (with respect to V

SS

and PGND) TS, TTC 7 V

VTSB 3.6 V

ISET1, ISET2 3.3 V

Voltage difference between SNS and BAT inputs (V

SNS

– V

BAT

) ±1 V

Output sink STAT1, STAT2, PG 10 mA

Output current (average) OUT 2.2 A

T

A

Operating free-air temperature range –40°C to 85°C

T

J

Junction temperature range –40°C to 125°C

T

stg

Storage temperature –65°C to 150°C

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds 300°C

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating

conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

PACKAGE DISSIPATION RATINGS

T

A

< 40°C DERATING FACTOR

PACKAGE θ

JA

θ

JC

POWER RATING ABOVE T

A

= 40°C

RHL

(1)

46.87°C/W 2.5°C/W 1.81 W 0.021 W/°C

(1) This data is based on using the JEDEC High-K board, and the exposed die pad is connected to a copper pad on the board. This is

connected to the ground plane by a 2x3 via matrix.

RECOMMENDED OPERATING CONDITIONS

MIN MAX UNIT

Supply voltage, V

CC

and IN (Tie together) 4.35

(1)

16

(2)

V

Operating junction temperature range, T

J

–40 125 °C

(1) The IC continues to operate below V

min

, to 3.5 V, but the specifications are not tested and not specified.

(2) The inherent switching noise voltage spikes should not exceed the absolute maximum rating on either the IN or OUT pins. A tight layout

minimizes switching noise.

ELECTRICAL CHARACTERISTICS

T

J

= 0°C to 125°C and recommended supply voltage range (unless otherwise stated)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Input Currents

2 Copyright © 2009–2012, Texas Instruments Incorporated

V

IREG

+

1V

RSET1

1000,

V

IREG*PRE

+

0.1V

RSET2

1000,

bq24105-Q1

www.ti.com

SLUS953A –AUGUST 2009–REVISED APRIL 2012

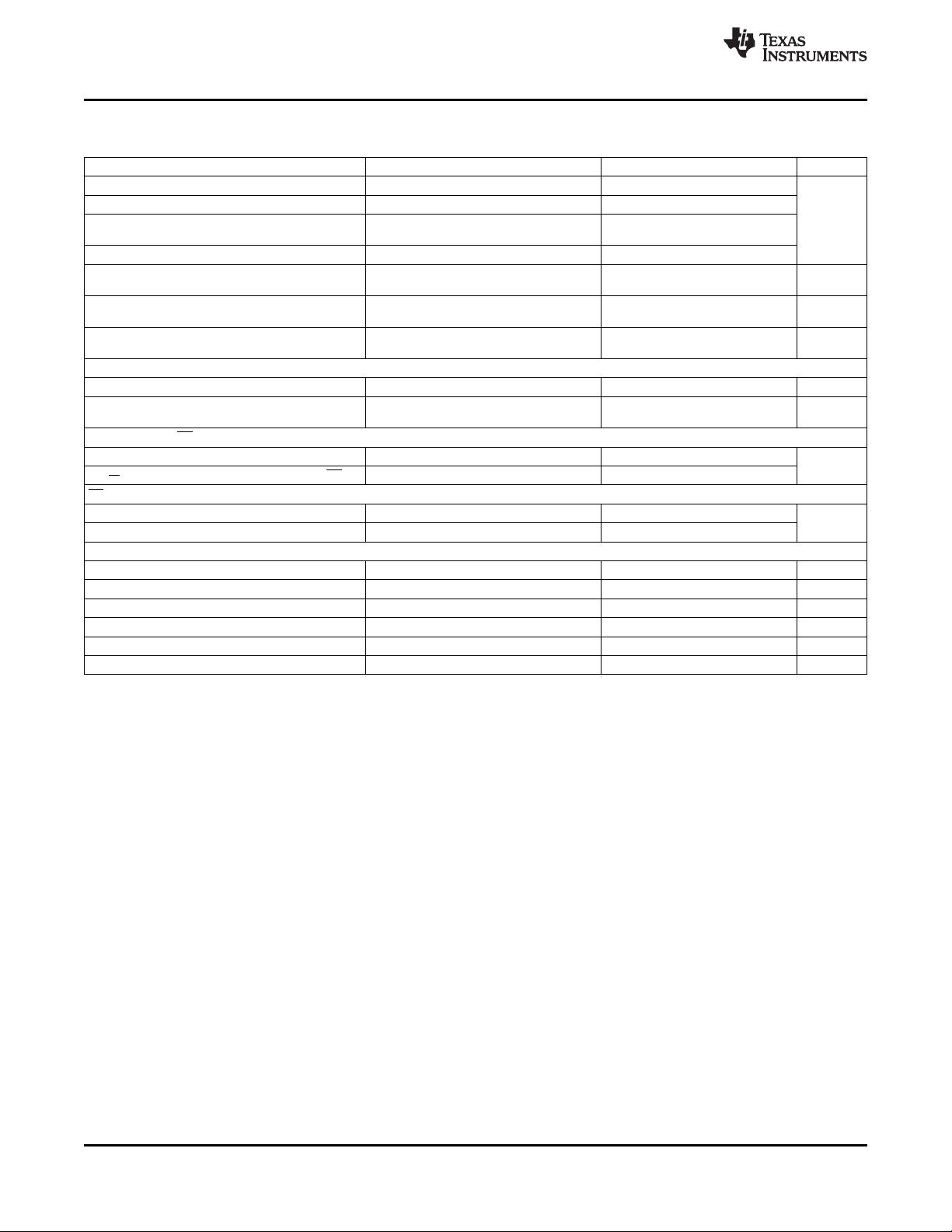

ELECTRICAL CHARACTERISTICS (continued)

T

J

= 0°C to 125°C and recommended supply voltage range (unless otherwise stated)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

V

CC

> V

CC(min)

, PWM switching 10

mA

I

(VCC)

V

CC

supply current V

CC

> V

CC(min)

, PWM NOT switching 5

V

CC

> V

CC(min)

, CE = HIGH 315 μA

0°C ≤ T

J

≤ 65°C, V

I(BAT)

= 4.2 V,

3.5

V

CC

< V

(SLP)

or V

CC

> V

(SLP)

but not in charge

Battery discharge sleep current, (SNS, 0°C ≤ T

J

≤ 65°C, V

I(BAT)

= 8.4 V,

I

(SLP)

5.5 μA

BAT, OUT, FB pins) V

CC

< V

(SLP)

or V

CC

> V

(SLP)

but not in charge

0°C ≤ T

J

≤ 65°C, V

I(BAT)

= 12.6 V,

7.7

V

CC

< V

(SLP)

or V

CC

> V

(SLP)

but not in charge

Voltage Regulation

Feedback regulation REF for bq24105

V

IBAT

I

IBAT

= 25 nA typical into pin 2.1 V

(W/FB)

T

A

= 25°C –0.5% 0.5%

Voltage regulation accuracy

–1% 1%

Current Regulation - Fast Charge

V

LOWV

≤ V

I(BAT)

< V

OREG

,

I

OCHARGE

Output current range of converter 150 2000 mA

V

(VCC)

- V

I(BAT)

> V

(DO-MAX)

100 mV ≤ V

IREG

≤ 200 mV,

V

IREG

Voltage regulated across R

(SNS)

Accuracy –10% 10%

Programmed Where

5 kΩ ≤ RSET1 ≤ 10 kΩ, Select RSET1 to

program V

IREG

,

V

IREG(measured)

= I

OCHARGE

+ R

SNS

(–10% to 10% excludes errors due to RSET1

and R

(SNS)

tolerances)

V

(LOWV)

≤ V

I(BAT)

≤ V

O(REG)

,

V

(ISET1)

Output current set voltage 1 V

V

(VCC)

≤ V

I(BAT)

×

V(DO-MAX)

V

LOWV

≤ V

I(BAT)

< V

O(REG)

,

K

(ISET1)

Output current set factor 1000 V/A

V

(VCC)

≤ V

I(BAT)

+

V(DO-MAX)

Precharge and Short-Circuit Current Regulation

Precharge to fast-charge transition voltage

V

LOWV

threshold, BAT, 68 71.4 75 %V

O(REG)

bq24100/03/03A/04/05/08/09 ICs only

Deglitch time for precharge to fast charge Rising voltage;

t 20 30 40 ms

transition, t

RISE

, t

FALL

= 100 ns, 2-mV overdrive

I

OPRECHG

Precharge range V

I(BAT)

< V

LOWV

, t < t

PRECHG

15 200 mA

V

(ISET2)

Precharge set voltage, ISET2 V

I(BAT)

< V

LOWV

, t < t

PRECHG

100 mV

K

(ISET2)

Precharge current set factor 1000 V/A

100 mV ≤ V

IREG-PRE

≤ 100 mV,

V

IREG-PRE

Voltage regulated across R

SNS

-Accuracy –20% 20%

(PGM) Where

1.2 kΩ ≤ RSET2 ≤ 10 kΩ, Select RSET1

to program V

IREG-PRE

,

V

IREG-PRE

(Measured) = I

OPRE-CHG

× R

SNS

(–20% to 20% excludes errors due to RSET1

and R

SNS

tolerances)

Charge Termination (Current Taper) Detection

I

TERM

Charge current termination detection range V

I(BAT)

> V

RCH

15 200 mA

Charge termination detection set voltage,

V

TERM

V

I(BAT)

> V

RCH

100 mV

ISET2

K

(ISET2)

Termination current set factor 1000 V/A

Charger termination accuracy V

I(BAT)

> V

RCH

–20% 20%

Both rising and falling,

t

dg-TERM

Deglitch time for charge termination 20 30 40 ms

2-mV overdrive t

RISE

, t

FALL

= 100 ns

Temperature Comparator and VTSB Bias Regulator

Copyright © 2009–2012, Texas Instruments Incorporated 3

bq24105-Q1

SLUS953A –AUGUST 2009–REVISED APRIL 2012

www.ti.com

ELECTRICAL CHARACTERISTICS (continued)

T

J

= 0°C to 125°C and recommended supply voltage range (unless otherwise stated)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

%

LTF

Cold temperature threshold, TS, % of bias V

LTF

= V

O(VTSB)

× % LTF/100 72.8% 73.5% 74.2%

%

HTF

Hot temperature threshold, TS, % of bias V

HTF

= V

O(VTSB)

× % HTF/100 33.7% 34.4% 35.1%

Cutoff temperature threshold, TS, % of

%

TCO

V

TCO

= V

O(VTSB)

× % TCO/100 28.7% 29.3% 29.9%

bias

LTF hysteresis 0.5% 1% 1.5%

Both rising and falling,

t

dg-TS

Deglitch time for temperature fault, TS 20 30 40 ms

2-mV overdrive t

RISE

, t

FALL

= 100 ns

V

CC

> V

IN(min)

,

V

O(VTSB)

TS bias output voltage 3.15 V

I

(VTSB)

= 10 mA 0.1 μF ≤ C

O(VTSB)

≤ 1 μF

V

CC

>

IN(min)

,

V

O(VTSB)

TS bias voltage regulation accuracy –10% 10%

I

(VTSB)

= 10 mA 0.1 μF ≤ C

O(VTSB)

≤ 1 μF

Battery Recharge Threshold

V

RCH

Recharge threshold voltage Below V

OREG

75 100 125 mV/cell

V

I(BAT)

< decreasing below threshold,

t

dg-RCH

Deglitch time 20 30 40 ms

t

FALL

= 100 ns 10-mV overdrive

Stat1, Stat2, and PG Outputs

V

OL(STATx)

Low-level output saturation voltage, STATx I

O

= 5 mA 0.5

V

V

OL(PG)

Low-level output saturation voltage, PG I

O

= 10 mA 0.1

CE Input

V

IL

Low-level input voltage I

IL

= 5 μA 0 0.4

V

V

IH

High-level input voltage I

IH

= 20 μA 1.3 V

CC

TTC Input

t

PRECHG

Precharge timer 1440 1800 2160 s

t

CHARGE

Programmable charge timer range t

(CHG)

= C

(TTC)

× K

(TTC)

25 572 minutes

Charge timer accuracy 0.01 μF ≤ C

(TTC)

≤ 0.18 μF -10% 10%

K

TTC

Timer multiplier 2.6 min/nF

C

TTC

Charge time capacitor range 0.01 0.22 μF

V

TTC_EN

TTC enable threshold voltage V

(TTC)

rising 200 mV

4 Copyright © 2009–2012, Texas Instruments Incorporated

bq24105-Q1

www.ti.com

SLUS953A –AUGUST 2009–REVISED APRIL 2012

ELECTRICAL CHARACTERISTICS (continued)

T

J

= 0°C to 125°C and recommended supply voltage range (unless otherwise stated)

PARAMETER TEST CONDITIONS MIN TYP MAX UNIT

Sleep Comparator

V

CC

≤ V

IBAT

V

CC

≤ V

IBAT

2.3 V ≤ V

I(OUT)

≤ V

OREG,

for 1 or 2 cells

+5 mV +75 mV

V

SLP-ENT

Sleep-mode entry threshold V

V

I(OUT)

= 12.6 V, R

IN

= 1 kΩ V

CC

≤ V

IBAT

V

CC

≤ V

IBAT

bq24105/15

(1)

-4 mV +73 mV

V

SLP-EXIT

Sleep-mode exit hysteresis, 2.3 V ≤ V

I(OUT)

≤ V

OREG

40 160 mV

V

CC

decreasing below threshold,

t

FALL

= 100 ns, 10-mV overdrive, 5 μs

PMOS turns off

t

dg-SLP

Deglitch time for sleep mode

V

CC

decreasing below threshold,

t

FALL

= 100 ns, 10-mV overdrive, 20 30 40 ms

STATx pins turn off

UVLO

V

UVLO-ON

IC active threshold voltage V

CC

rising 3.15 3.30 3.50 V

IC active hysteresis V

CC

falling 120 150 mV

PWM

7 V ≤ V

CC

≤ V

CC(max)

400

Internal P-channel MOSFET on-resistance

4.5 V ≤ V

CC

≤ 7 V 500

mΩ

7 V ≤ V

CC

≤ V

CC(max)

130

Internal N-channel MOSFET on-resistance

4.5 V ≤ V

CC

≤ 7 V 150

f

OSC

Oscillator frequency 1.1 MHz

Frequency accuracy –9% 9%

D

MAX

Maximum duty cycle 100%

D

MIN

Minimum duty cycle 0%

t

TOD

Switching delay time (turn on) 20 ns

t

syncmin

Minimum synchronous FET on time 60 ns

Synchronous FET minimum current-off

50 400 mA

threshold

(2)

Battery Detection

Battery detection current during time-out

I

DETECT

V

I(BAT)

< V

OREG

– V

RCH

2 mA

fault

I

DISCHRG1

Discharge current V

SHORT

< V

I(BAT)

< V

OREG

– V

RCH

400 μA

t

DISCHRG1

Discharge time V

SHORT

< V

I(BAT)

< V

OREG

– V

RCH

1 s

I

WAKE

Wake current V

SHORT

< V

I(BAT)

< V

OREG

– V

RCH

2 mA

t

WAKE

Wake time V

SHORT

< V

I(BAT)

< V

OREG

– V

RCH

0.5 s

Begins after termination detected,

I

DISCHRG2

Termination discharge current 400 μA

V

I(BAT)

≤ V

OREG

t

DISCHRG2

Termination time 262 ms

Output Capacitor

Required output ceramic capacitor range

C

OUT

from SNS to PGND, between inductor and 4.7 10 47 μF

R

SNS

Required SNS capacitor (ceramic) at SNS

C

SNS

0.1 μF

pin

Protection

Threshold over V

OREG

to turn off P-channel

V

OVP

OVP threshold voltage MOSFET, STAT1, and STAT2 during charge 110 117 121 %V

O(REG)

or termination states

I

LIMIT

Cycle-by-cycle current limit 2.6 3.6 4.5 A

V

SHORT

Short-circuit voltage threshold, BAT V

I(BAT)

falling 1.95 2 2.05 V/cell

I

SHORT

Short-circuit current V

I(BAT)

≤ V

SHORT

35 65 mA

T

SHTDWN

Thermal trip 165 °C

Thermal hysteresis 10 °C

(1) For bq24105 and bq24115 only. R

IN

is connected between IN and PGND pins and needed to ensure sleep entry.

(2) N-channel always turns on for ~60 ns and then turns off if current is too low.

Copyright © 2009–2012, Texas Instruments Incorporated 5

剩余37页未读,继续阅读

不觉明了

- 粉丝: 3238

- 资源: 5614

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0