2020年《计算机组成原理》课程期末考卷(A卷)附答案

需积分: 0 174 浏览量

更新于2022-06-09

2

收藏 570KB PDF 举报

《计算机组成原理》是计算机科学与技术领域的重要基础课程,主要研究计算机系统的基本组成和工作原理。本课程期末考卷的题目涵盖了计算机组成原理的核心概念,包括I/O外设与主机的交互、控制单元CU的功能、主存与I/O设备的数据传输、Cache与主存的地址映射等关键知识点。

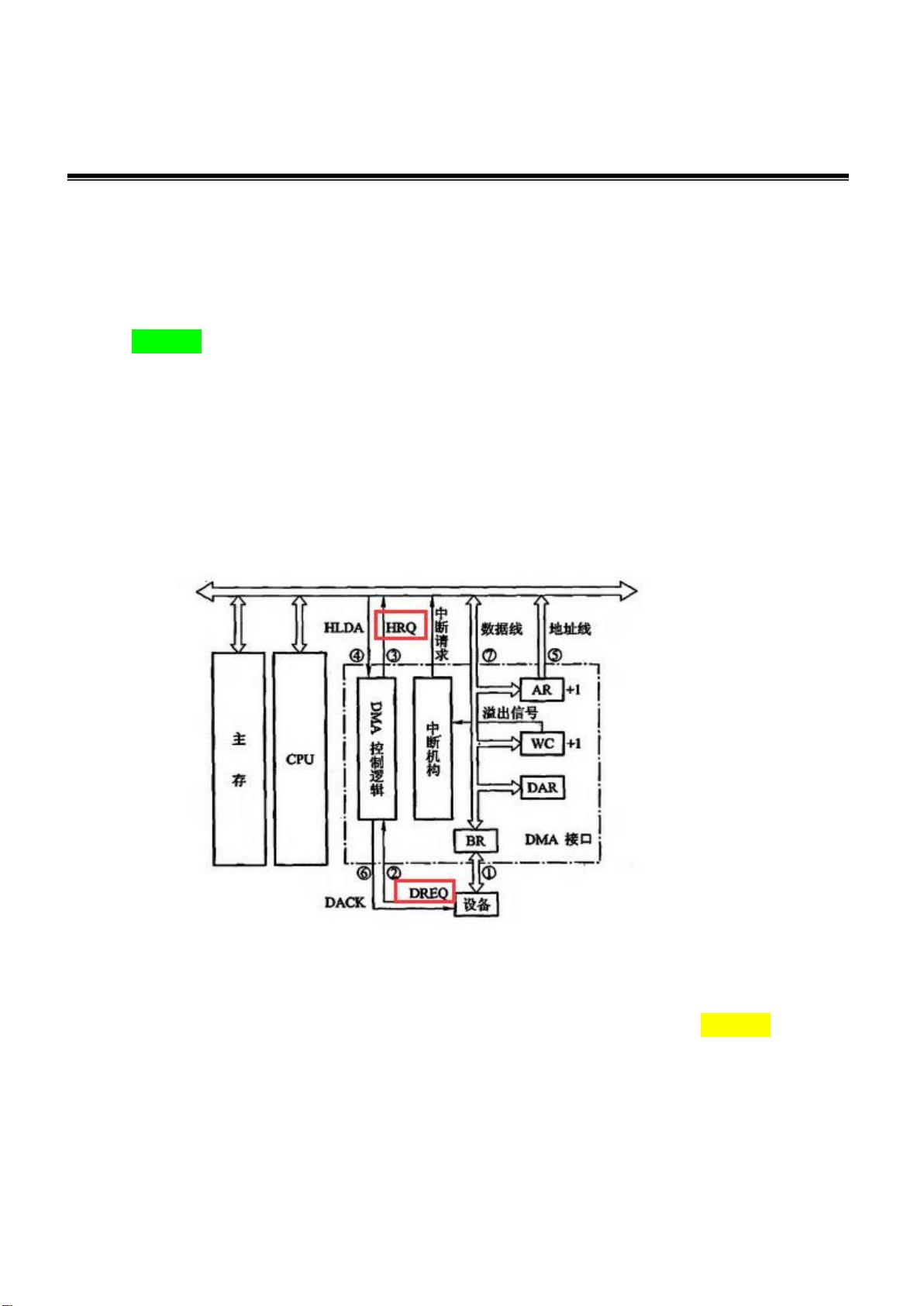

1. I/O外设与主机的反馈线是计算机系统中实现通信和控制的重要手段。例如,CPU通过总线协议与I/O接口进行数据交换时,可能会发送BG信号表示总线同意,而外设通过BS信号反馈总线状态。在DMA方式中,DREQ和HRO是外设与CPU通信的握手信号,确保数据传输的同步。此外,状态线如'ready'和'busy'用于告知主机外设的工作状态。

2. 控制单元CU是计算机系统的心脏,负责发出各种控制信号以协调各个组件的操作。对主存,它会产生R/W信号指示读写操作,并通过片选CS信号选择特定的内存芯片。对ALU,CU会设置运算器工作方式的控制信号S1S2S3S4以及运算脉冲。对I/O设备,CU会发送INTR中断请求信号和HLDA保持允许信号。

3. 主存与I/O设备直接通信通常采用DMA方式,这需要在两者之间设立数据总线,以实现数据的快速、无CPU干预的传输。

4. 图2描述了输入设备与CPU的同步数据输入传输过程。在这个过程中,总线周期的四个时钟周期分别用于地址传输、读命令、数据提供和撤销命令。地址信号需要保持整个总线周期以确保正确寻址,读命令在地址信号之后出现是为了避免地址错误。如果改为CPU与输出设备间的传输,需要将读命令变为写命令,数据会提前出现在数据总线上。若总线周期不足,可以采用异步或半同步方式。当涉及CPU与存储器间传输时,需要增加片选CS信号,以确保正确选择存储芯片。

5. 在全相联映射的Cache与主存地址映射中,因为主存的任何一块都可以映射到Cache的任何位置,所以主存地址不需要包含Cache字块地址。在比较主存字块标记和Cache标记时,需要遍历Cache的所有标记位,以查找匹配项,为了提高速度,可以采用硬件加速机制,如硬件比较器或哈希表。

以上内容详细解析了考卷中涉及的计算机组成原理知识点,包括I/O交互机制、控制单元的作用、数据传输方式以及Cache地址映射等,这些都是理解计算机系统基本运作的关键。学习这些内容有助于深入理解计算机系统的内部工作流程。

就是搞笑

- 粉丝: 3112

- 资源: 1

最新资源

- 光伏逆变器设计方案TMS320F28335-176资料 PCB 原理图 源代码 1. 本设计DC-DC采用Boost升压,DCAC采用单相全桥逆变电路结构 2. 以TI公司的浮点数字信号控制器TMS

- 通讯录排序-基于Python实现的通讯录多维度排序方法

- 全志V3S linux qt程序实现按键控制LED灯代码.zip

- allwinner全志-V3S-LINUX-QT-实现RJ45以太网数据收发通讯.zip

- allwinner全志-V3S-LINUX-QT-第一个程序实现helloword.zip

- 扑克牌数字检测19-YOLO(v5至v11)、COCO、CreateML、Paligemma、TFRecord、VOC数据集合集.rar

- allwinner全志-V3S-LINUX-QT-GC0308摄像头实现人脸检测-MTCNN神经网络-OPENCV-FACENET.zip

- 毕业设计-基于SpringBoot+Mybatis开发的分布式校园租赁系统全部资料+详细文档+高分项目.zip

- 毕业设计-基于java的校园二手交易系统全部资料+详细文档+高分项目.zip

- 毕业设计-基于Hadoop的校园资源云存储的设计与开发全部资料+详细文档+高分项目.zip

- 毕业设计-基于tp5的校园生活系统全部资料+详细文档+高分项目.zip

- 毕业设计-基于SpringBoot的二手商城系统、二手交易平台,校园二手书籍交易,社区二手交易平台全部资料+详细文档+高分项目.zip

- 基于 Next.js(RSC) & tRPC 的多功能校园表白墙论坛系统校园万能墙全部资料+详细文档+高分项目.zip

- 基于 Laravel 校园二手交易平台全部资料+详细文档+高分项目.zip

- 基于 微信小程序-云开发 的校园服务平台(提供二手交易和失物招领功能)全部资料+详细文档+高分项目.zip

- 基于 React Native 的校园社交APP.全部资料+详细文档+高分项目.zip