MISC Architecture Specification v1.0

Sanechips Confidential 2023/06/29 1

AIA

Architecture Specification

Text highlighted in yellow is either Work in Progress or TBD

MISC Architecture Specification v1.0

Sanechips Confidential 2023/06/29 2

Revision History:

Date

Version

Comment

2023/4/3

0.1

Initial draft

目录

1Overview ............................................................................................................................................................4

1.1 block diagram: .................................................................................................................................................4

1.2 Acronyms .........................................................................................................................................................5

1.3 AIA 功能说明...................................................................................................................................................5

2 AIA Top Architecture..........................................................................................................................................5

2.1 AIA Top Interfaces ...........................................................................................................................................6

2.1.1 APLIC 接口.......................................................................................................................................6

2.1.2 APLIC 接口时序图...........................................................................................................................9

2.1.3 IMSIC 接口.....................................................................................................................................10

2.1.4 IMSIC 接口时序图.........................................................................................................................13

2.2 AIA main flow.................................................................................................................................................14

2.2.1 APLIC IDC flow ...............................................................................................................................14

2.2.2 APLIC IDC (legacy)flow .............................................................................................................16

2.2.3 APLIC IMSIC flow............................................................................................................................17

3 子模块设计 .....................................................................................................................................................18

3.1 APLIC 子模块设计 .........................................................................................................................................18

3.1.1 APLIC 模块划分.............................................................................................................................18

3.1.2 aplic_gateway 逻辑设计...............................................................................................................19

3.1.3 aplic_intr_route 逻辑设计 ............................................................................................................20

3.1.4 aplic_regfile 逻辑设计 ..................................................................................................................22

3.2 IMSIC 子模块设计.........................................................................................................................................24

3.2.1 IMSIC 模块划分.............................................................................................................................24

3.3 BUS 子模块设计............................................................................................................................................39

3.3.1 MSI 中断在 CMN 中传输过程......................................................................................................39

3.3.2 AXI4_Stream 与 pub 数据转换.....................................................................................................40

3.4 CLINT timer 模块设计 ...................................................................................................................................42

3.4.1 timer 模块功能 .............................................................................................................................42

3.4.2 timer 模块接口信号 .....................................................................................................................43

3.4.3 timer 模块数据流 .........................................................................................................................44

3.4.4 timer 模块寄存器 .........................................................................................................................45

3.5 模块寄存器说明 ...........................................................................................................................................45

3.5.1 AIA 架构下新增的 CSR..................................................................................................................45

3.5.2 CSRs for external interrupts via an IMSIC ......................................................................................46

3.5.3 Indirectly accessed interrupt-file registers ....................................................................................48

MISC Architecture Specification v1.0

Sanechips Confidential 2023/06/29 3

3.5.4 AIA memory-mapped regs.............................................................................................................54

3.5.5 aplic 发送 MSI 地址计算过程 ......................................................................................................69

4 Open Items ......................................................................................................................................................70

MISC Architecture Specification v1.0

Sanechips Confidential 2023/06/29 4

1Overview

This document describes AIA micro-Architecture Specification.

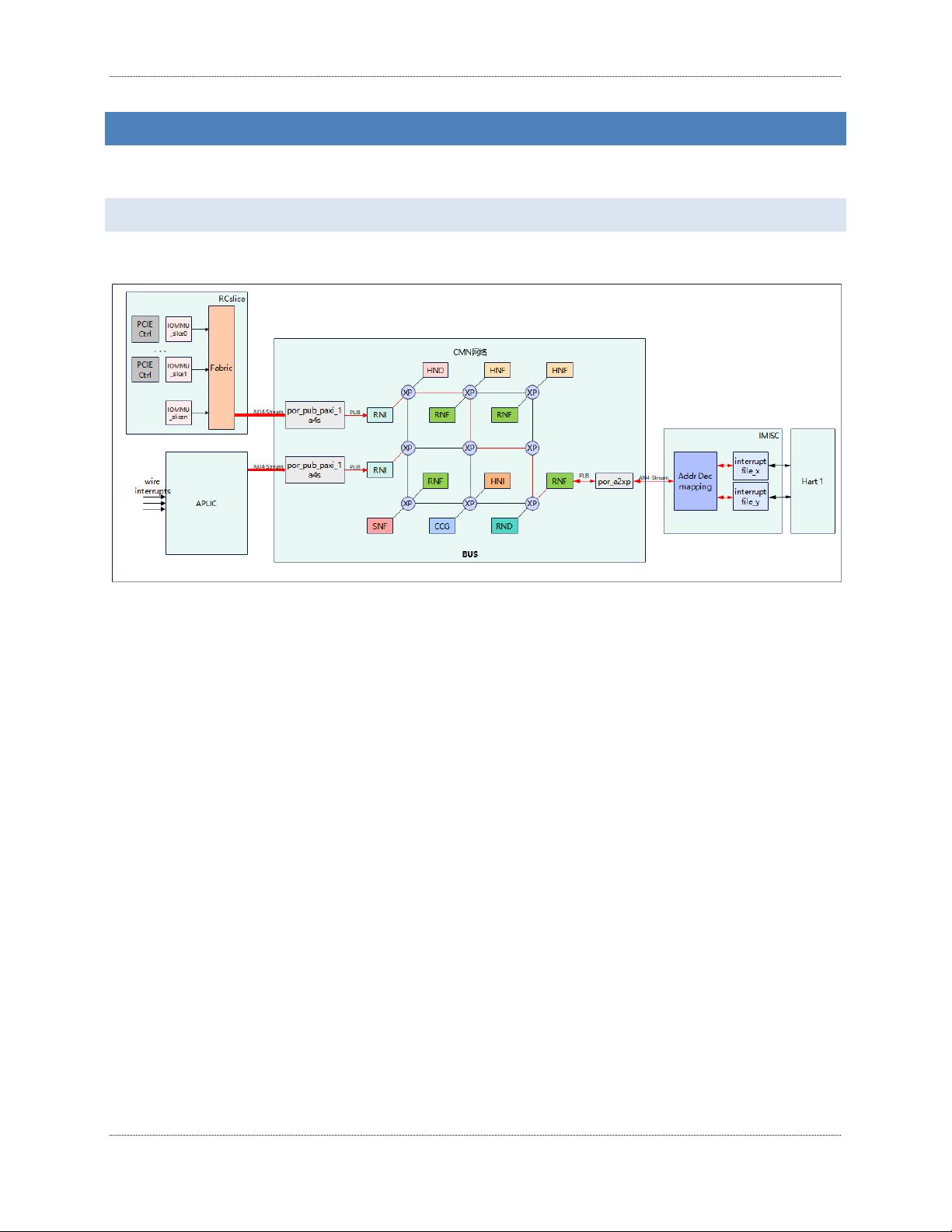

1.1 block diagram:

high level block diagram:

Figure 1: The AIA high level block diagram

如图所示,通过 PCIE 产生的中断信息和有线中断在 APLIC 处理后的中断信息采用 AXI4_Stream 数据流

的方式通过 por_pub_paxi_1a4s 模块转化为 pub 数据,在 RNI 节点接入至 CMN 网络,并通过 XP 路由至 RNF

节点,通过 por_a2xp 模块转化为 AXI4_Stream 数据流,在 IMSIC 模块进行中断数据、ID 等处理,并将信息

传给 Hart 进行中断处理,其中 por_pub_paxi_1a4s 模块和 por_a2xp 模块均是 CMN 网络中数据转换模块。本

设计支持跨 Die 跨 socket 路由。

AIA 中断控制器主要分为 APLIC 和 IMSIC 两个主要部分。

外部中断由 APLIC 接收,APLIC 可以根据模式选择直发或者转成 MSI 转发给 IMSIC 处理。两种模式均由

A4S 总线路由。APLIC 支持 M 模式和 S 模式下的中断请求。

本设计完全支持 MSI。每个 hart 都有 IMSIC,可用来控制 external interrupt。每个 IMSIC 在机器的地址

空间中被分配了一个或多个不同的地址。IMSIC 支持 M 模式,S 模式和 VS 模式下的中断请求。所有 IMSIC

在机器的实体地址空间中都有唯一的地址,可以接收 MSI 来自其他 hart 或 device。hart 的 MSC 纪录在

IMSIC 的 interrupt file 当中,该 file 主要纪录 interrupt pending bit 和 interrupt enablebit。支持其他 hart 的请

求即实现了 IPI。IMSIC 针对 machine level 和 supervisor level 及 virtual supervisorlevel 皆有单独的地址。通过

不同的地址写入的权限管理,可以给予或拒绝每个级别发出 interrupt 信号,支持虚拟化。

MISC Architecture Specification v1.0

Sanechips Confidential 2023/06/29 5

1.2 Acronyms

� AIA (Advanced Interrupt Architecture)

� PLIC (Platform-Level Interrupt Controller)

� APLIC (Advanced Platform-Level Interrupt Controller)

� IMSIC (Incoming Message-Signaled Interrupt Controller)

� MSI (message-signaled interrupt)

� hart (hardware thread)

1.3 AIA 功能说明

本设计实现以下功能:

� 以 RISC-V privileged 为基础,符合 RISC-V Advanced Interrupt Architecture 架构要求。

� 支持有线中断(wire interrupt),支持 MSI(message-signaled interrupts)。

� 对于 wire interrupt 定义新的 Interrupt controller 也就是 advanced PLIC(APLIC),该 interrupt

controller 为每个特权级别(machine level、supervisor level),都有一个独立的控制界面可以将

wired interrupt 转换成 MSI。

� 支持 RISC-V hart software interrupt(IMSIC 支持 IPI)。

� 允许软件将所有 interrupt priority 排序,而非只依靠单独的 interrupt controller 对 external interrupt

进行 priority 排序。

� 当 hart 实现 hypervisor extension 时,可以为 virtual machine(VM)的 interrupt 提供架构定义的支

持,实现了中断虚拟化。

� 透过 I/O MMU (memory management unit)的帮助,运行在 VM 中的 guest OS 有最大的机会和能力

直接控制设备,避免让 hardware interrupt 限制了 VM 数量的因素。

� 在实现的弹性、效率和灵活性之间,尽可能保持最佳的折衷,从而实现上述所有目标

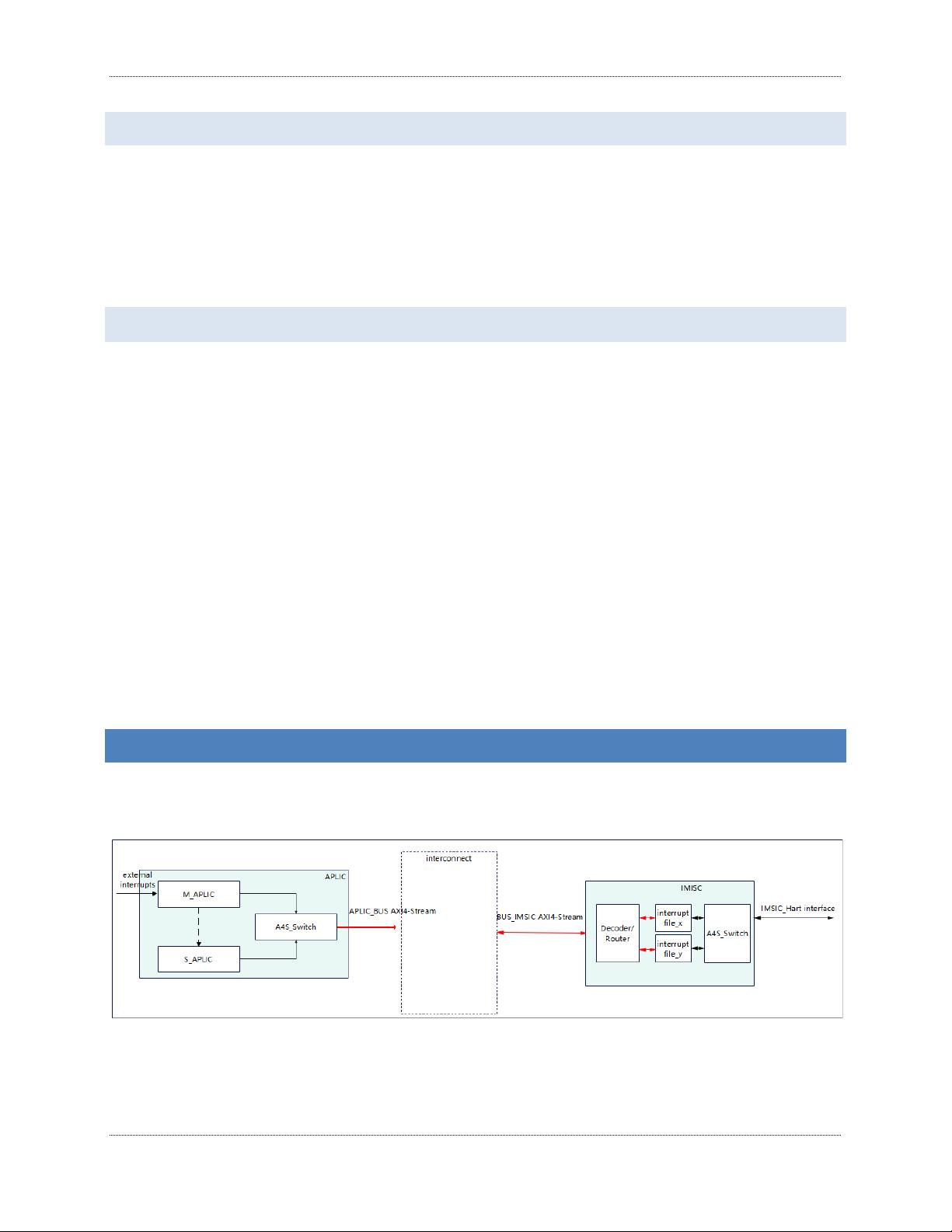

2 AIA Top Architecture

本设计同时支持 APLIC 和 IMSIC 的硬件实现。APLIC 同时支持 IDC 模式和 MSI 模式。IMSIC 的消息来源有

PCIE,APLIC,其他 hart 的中断请求。

Figure 2: The AIA Top Architecture

单个 APLIC 支持固定数量的中断源,与 APLIC 上的物理输入中断线完全对应。支持电平/边沿敏感中断

触发。每个 APLIC 的中断源都有一个固定的唯一标识号,范围为 1 到 N,其中 N 是 APLIC 中中断源的总数。