没有合适的资源?快使用搜索试试~ 我知道了~

32Meg x 8, 16Meg x16 256Mb SYNCHRONOUS DRAM手册

需积分: 0 0 下载量 137 浏览量

2024-05-12

20:41:04

上传

评论

收藏 863KB PDF 举报

温馨提示

试读

63页

256Mb SDRAM是一种高速CMOS动态随机访问存储器,设计用于3.3V VDD和3.3V VDDQ存储系统,包含268,4355,456位。内部配置为具有同步接口的四组DRAM。每个67,108,864位的组被组织成8,192行,512列,16位,或8,192行,1024列,8位。在启动自动预充电功能的情况下,在突发序列的末尾发起的自定时行预充电是可用的。预充电的一个银行,而访问其他三个银行之一,将隐藏预充电周期,并提供无缝,高速,随机访问操作。256Mb的SDRAM包括自动刷新模式和省电、断电模式。所有信号都注册在时钟信号CLK的正边缘。所有输入和输出都是LVTTL兼容的。256Mb的SDRAM具有以自动列地址生成的高数据速率同步突发数据的能力,能够在内部bank之间交错隐藏预充电时间,以及在每个时钟周期上随机改变列地址的能力。SDRAM的读写访问是面向突发的,从一个选定的位置开始,并在一个编程序列中继续为一个可编程的数量的位置。活动命令的注册从访问开始,然后是读或写命令。

资源推荐

资源详情

资源评论

IS42S83200G, IS42S16160G

IS45S83200G, IS45S16160G

Integrated Silicon Solution, Inc. — www.issi.com 1

Rev. A

3/20/2012

Copyright © 2012 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time with-

out notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain

the latest version of this device specification before relying on any published information and before placing orders for products.

Integrated Silicon Solution, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can

reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such ap-

plications unless Integrated Silicon Solution, Inc. receives written assurance to its satisfaction, that:

a.) the risk of injury or damage has been minimized;

b.) the user assume all such risks; and

c.) potential liability of Integrated Silicon Solution, Inc is adequately protected under the circumstances

FEATURES

• Clock frequency: 166, 143 MHz

• Fully synchronous; all signals referenced to a

positive clock edge

• Internal bank for hiding row access/precharge

• Single Power supply: 3.3V + 0.3V

• LVTTL interface

• Programmable burst length

– (1, 2, 4, 8, full page)

• Programmable burst sequence:

Sequential/Interleave

• Auto Refresh (CBR)

• Self Refresh

• 8K refresh cycles every 32 ms (A2 grade) or

64 ms (commercial, industrial, A1 grade)

• Random column address every clock cycle

• Programmable CAS latency (2, 3 clocks)

• Burst read/write and burst read/single write

operations capability

• Burst termination by burst stop and precharge

command

OPTIONS

• Package:

54-pin TSOP-II

54-ball BGA

• Operating Temperature Range:

Commercial (0

o

C to +70

o

C)

Industrial (-40

o

C to +85

o

C)

Automotive Grade A1 (-40

o

C to +85

o

C)

Automotive Grade A2 (-40

o

C to +105

o

C)

OVERVIEW

ISSI's 256Mb Synchronous DRAM achieves high-speed

data transfer using pipeline architecture. All inputs and

outputs signals refer to the rising edge of the clock input.

The 256Mb SDRAM is organized as follows.

32Meg x 8, 16Meg x16

256Mb SYNCHRONOUS DRAM

MARCH 2012

IS42S83200G IS42S16160G

8M x 8 x 4 Banks 4M x16x4 Banks

54-pin TSOPII 54-pin TSOPII

54-ball BGA 54-ball BGA

Parameter 32M x 8 16M x 16

Conguration 8M x 8 x 4

banks

4M x 16 x 4

banks

Refresh Count

Com./Ind.

A1

A2

8K/64ms

8K/64ms

8K/16ms

8K/64ms

8K/64ms

8K/16ms

Row Addresses A0-A12 A0-A12

Column Addresses A0-A9 A0-A8

Bank Address Pins BA0, BA1 BA0, BA1

Auto Precharge Pins A10/AP A10/AP

ADDRESS TABLE

KEY TIMING PARAMETERS

Parameter -6 -7 Unit

Clk Cycle Time

CAS Latency = 3 6 7 ns

CAS Latency = 2 10 7.5 ns

Clk Frequency

CAS Latency = 3 166 143 Mhz

CAS Latency = 2 100 133 Mhz

Access Time from Clock

CAS Latency = 3 5.4 5.4 ns

CAS Latency = 2 6.5 5.4 ns

2 Integrated Silicon Solution, Inc. — www.issi.com

Rev. A

3/20/2012

IS42S83200G, IS42S16160G

IS45S83200G, IS45S16160G

DEVICE OVERVIEW

The 256Mb SDRAM is a high speed CMOS, dynamic

random-access memory designed to operate in 3.3V Vdd

and 3.3V Vddq memory systems containing 268,435,456

bits. Internally configured as a quad-bank DRAM with a

synchronous interface. Each 67,108,864-bit bank is orga-

nized as 8,192 rows by 512 columns by 16 bits or 8,192

rows by 1,024 columns by 8 bits.

The 256Mb SDRAM includes an AUTO REFRESH MODE,

and a power-saving, power-down mode. All signals are

registered on the positive edge of the clock signal, CLK.

All inputs and outputs are LVTTL compatible.

The 256Mb SDRAM has the ability to synchronously burst

data at a high data rate with automatic column-address

generation, the ability to interleave between internal banks

to hide precharge time and the capability to randomly

change column addresses on each clock cycle during

burst access.

A self-timed row precharge initiated at the end of the burst

sequence is available with the AUTO PRECHARGE function

enabled.

Precharge

one bank while accessing one of the

other three banks will hide the

precharge

cycles and provide

seamless, high-speed, random-access operation.

SDRAM

read and write accesses are burst oriented starting

at a selected location and continuing for a programmed

number of locations in a programmed sequence. The

registration of an ACTIVE command begins accesses,

followed by a READ or WRITE command. The ACTIVE

command in conjunction with address bits registered are

used to select the bank and row to be accessed (BA0,

BA1 select the bank; A0-A12 select the row). The READ

or WRITE commands in conjunction with address bits

registered are used to select the starting column location

for the burst access.

Programmable READ or WRITE burst lengths consist of

1, 2, 4 and 8 locations or full page, with a burst terminate

option.

CLK

CKE

CS

RAS

CAS

WE

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

BA0

BA1

A10

A12

COMMAND

DECODER

&

CLOCK

GENERATOR

MODE

REGISTER

REFRESH

CONTROLLER

REFRESH

COUNTER

SELF

REFRESH

CONTROLLER

ROW

ADDRESS

LATCH

MULTIPLEXER

COLUMN

ADDRESS LATCH

BURST COUNTER

COLUMN

ADDRESS BUFFER

COLUMN DECODER

DATA IN

BUFFER

DATA OUT

BUFFER

DQML

DQMH

DQ 0-15

V

DD

/V

DDQ

V

ss

/V

ss

Q

13

13

9

13

13

9

16

16 16

16

512

(x 16)

8192

8192

8192

ROW DECODER

8192

MEMORY CELL

ARRAY

BANK 0

SENSE AMP I/O GATE

BANK CONTROL LOGIC

ROW

ADDRESS

BUFFER

A11

2

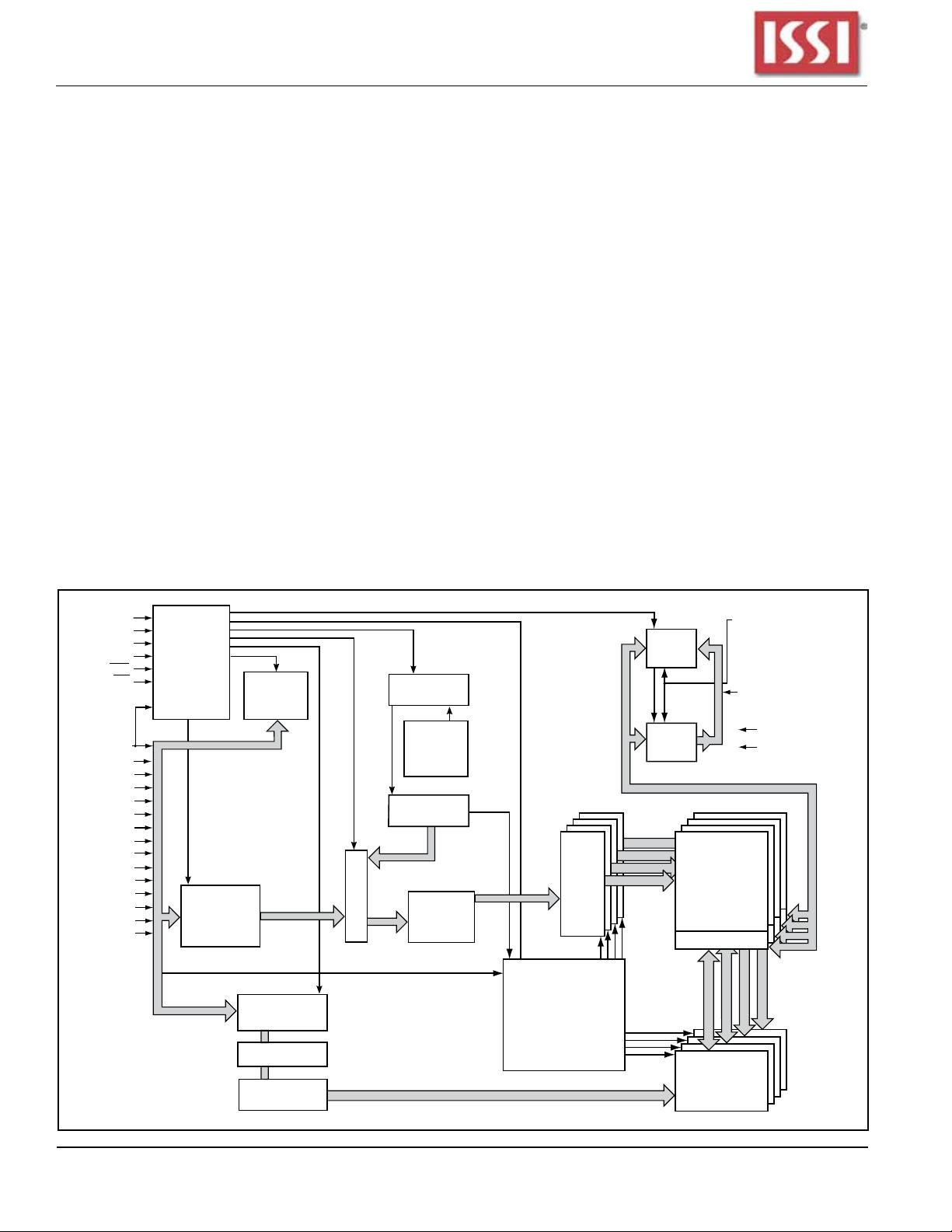

FUNCTIONAL BLOCK DIAGRAM (FOR 4Mx16x4 BANKS SHOWN)

Integrated Silicon Solution, Inc. — www.issi.com 3

Rev. A

3/20/2012

IS42S83200G, IS42S16160G

IS45S83200G, IS45S16160G

V

DD

DQ0

V

DD

Q

NC

DQ1

V

SS

Q

NC

DQ2

V

DD

Q

NC

DQ3

V

SS

Q

NC

V

DD

NC

WE

CAS

RAS

CS

BA0

BA1

A10

A0

A1

A2

A3

V

DD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

V

SS

DQ7

V

SS

Q

NC

DQ6

V

DD

Q

NC

DQ5

V

SS

Q

NC

DQ4

V

DD

Q

NC

V

SS

NC

DQM

CLK

CKE

A12

A11

A9

A8

A7

A6

A5

A4

V

SS

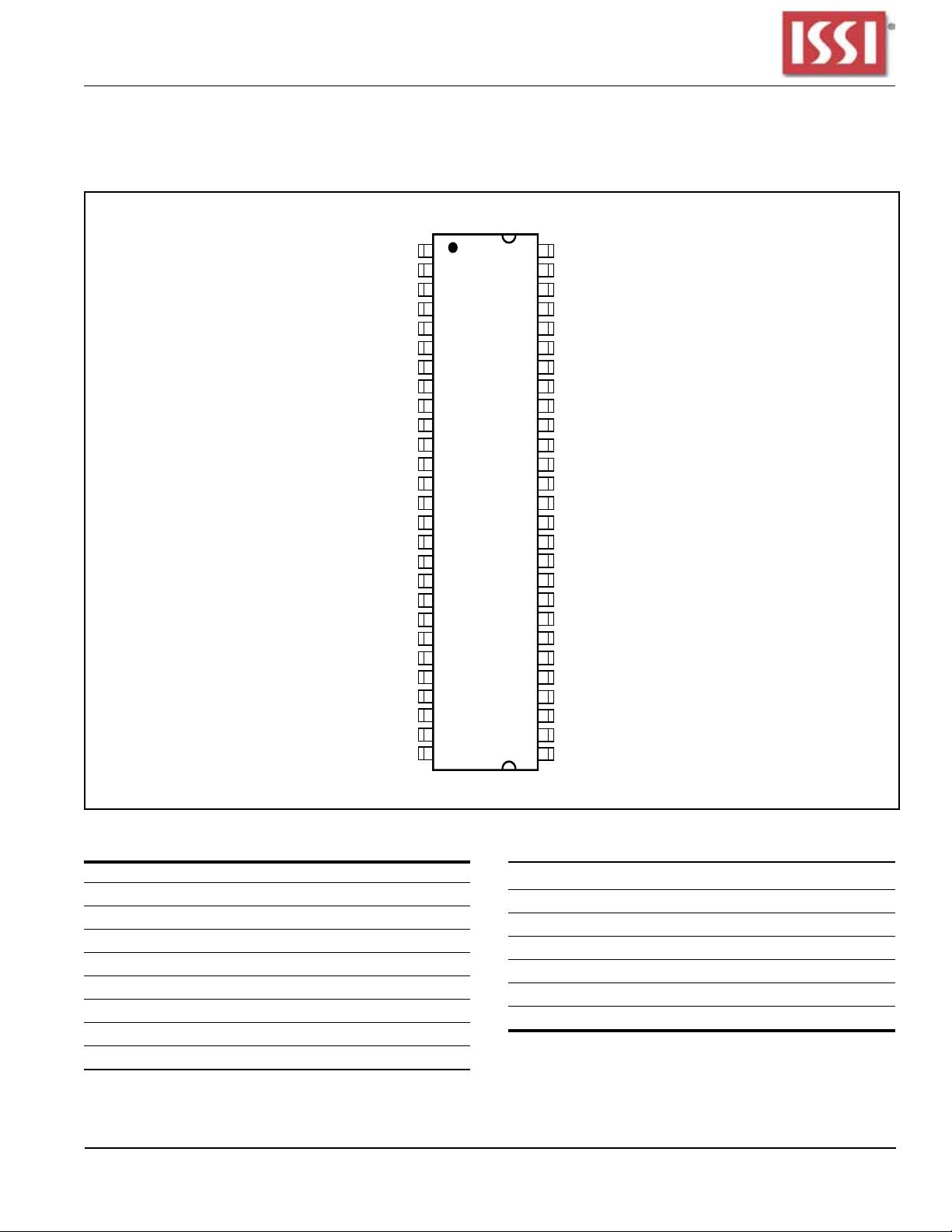

PIN CONFIGURATIONS

54 pin TSOP - Type II for x8

PIN DESCRIPTIONS

A0-A12 Row Address Input

A0-A9 Column Address Input

BA0, BA1 Bank Select Address

DQ0 to DQ7 Data I/O

CLK System Clock Input

CKE Clock Enable

CS Chip Select

RAS Row Address Strobe Command

CAS Column Address Strobe Command

WE Write Enable

DQM Data Input/Output Mask

Vdd Power

Vss Ground

Vddq Power Supply for I/O Pin

Vssq Ground for I/O Pin

NC No Connection

4 Integrated Silicon Solution, Inc. — www.issi.com

Rev. A

3/20/2012

IS42S83200G, IS42S16160G

IS45S83200G, IS45S16160G

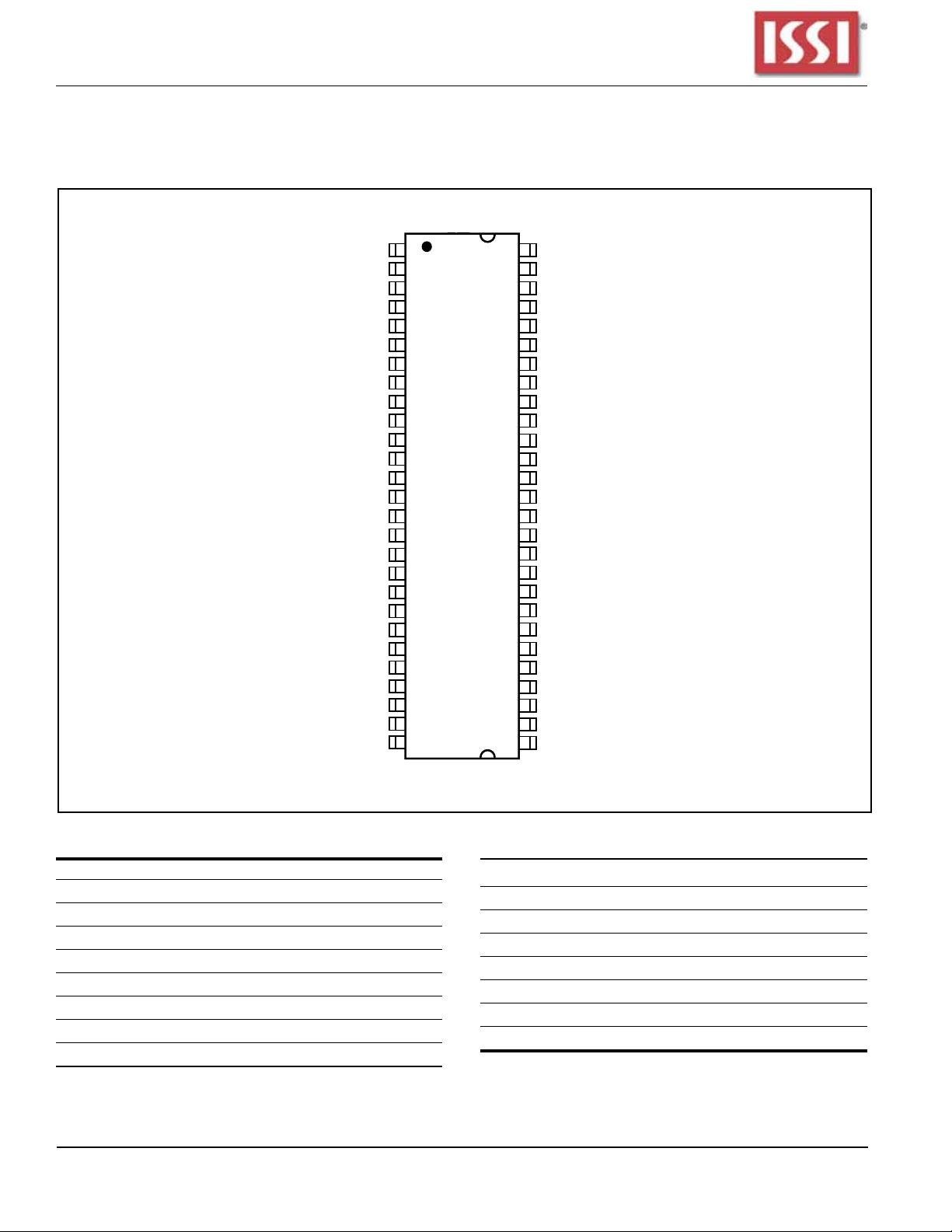

PIN CONFIGURATIONS

54 pin TSOP - Type II for x16

PIN DESCRIPTIONS

A0-A12 Row Address Input

A0-A8 Column Address Input

BA0, BA1 Bank Select Address

DQ0 to DQ15 Data I/O

CLK System Clock Input

CKE Clock Enable

CS Chip Select

RAS Row Address Strobe Command

CAS Column Address Strobe Command

V

DD

DQ0

V

DD

Q

DQ1

DQ2

V

SS

Q

DQ3

DQ4

V

DD

Q

DQ5

DQ6

V

SS

Q

DQ7

V

DD

DQML

WE

CAS

RAS

CS

BA0

BA1

A10

A0

A1

A2

A3

V

DD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

V

SS

DQ15

V

SS

Q

DQ14

DQ13

V

DD

Q

DQ12

DQ11

V

SS

Q

DQ10

DQ9

V

DD

Q

DQ8

V

SS

NC

DQMH

CLK

CKE

A12

A11

A9

A8

A7

A6

A5

A4

V

SS

WE Write Enable

DQML x16 Lower Byte, Input/Output Mask

DQMH x16 Upper Byte, Input/Output Mask

Vdd Power

Vss Ground

Vddq Power Supply for I/O Pin

Vssq Ground for I/O Pin

NC No Connection

Integrated Silicon Solution, Inc. — www.issi.com 5

Rev. A

3/20/2012

IS42S83200G, IS42S16160G

IS45S83200G, IS45S16160G

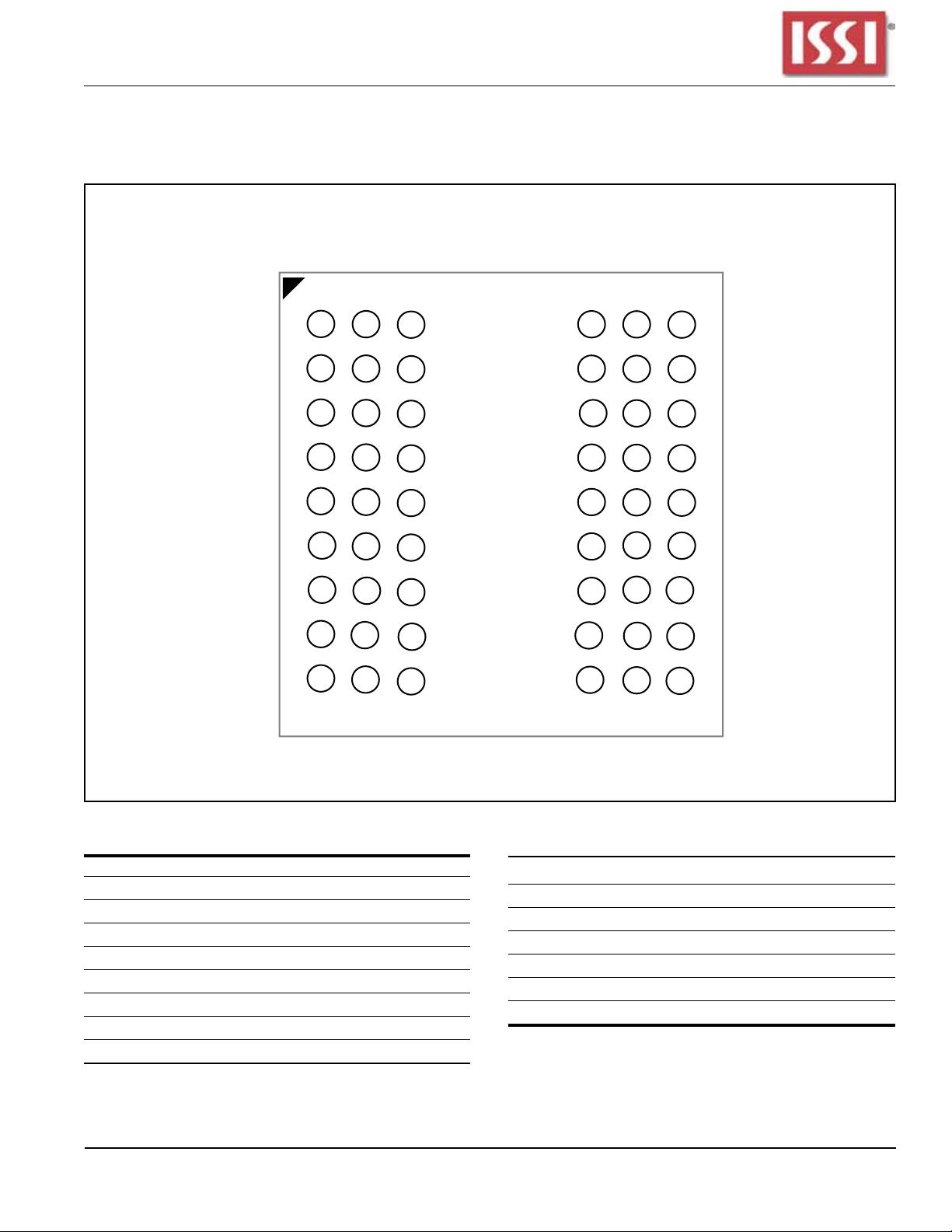

PIN CONFIGURATION

54-ball TF-BGA for x8 (Top View) (8.00 mm x 8.00 mm Body, 0.8 mm Ball Pitch)

package code: B

1 2 3 4 5 6 7 8 9

A

B

C

D

E

F

G

H

J

VSS

A12

A8

VSS

NC

CLK

A11

A7

A5

VSSQ

VDDQ

VSSQ

VDDQ

VSS

CKE

A9

A6

A4

VDDQ

VSSQ

VDDQ

VSSQ

VDD

CAS

BA0

A0

A3

DQ0

RAS

BA1

A1

A2

VDD

WE

CS

A10

VDD

PIN DESCRIPTIONS

A0-A12 Row Address Input

A0-A9 Column Address Input

BA0, BA1 Bank Select Address

DQ0 to DQ7 Data I/O

CLK System Clock Input

CKE Clock Enable

CS Chip Select

RAS Row Address Strobe Command

CAS Column Address Strobe Command

WE Write Enable

DQM Data Input/Output Mask

Vdd Power

Vss Ground

Vddq Power Supply for I/O Pin

Vssq Ground for I/O Pin

NC No Connection

NC

NC

NC

NC

DQM

DQ7

DQ6

DQ5

DQ4

NC

NC

NC

NC

NC

DQ1

DQ2

DQ3

剩余62页未读,继续阅读

资源评论

伊宇韵

- 粉丝: 2056

- 资源: 3

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 01-spring-boot-overview

- vgg模型-基于深度学习AI算法对猫的动作行为识别-不含数据集图片-含逐行注释和说明文档.zip

- vgg模型-CNN图像分类识别人脸-不含数据集图片-含逐行注释和说明文档.zip

- Detect It Easy v3.03

- shufflenet模型-基于人工智能的卷积网络训练识别鞋类-不含数据集图片-含逐行注释和说明文档.zip

- shufflenet模型-python语言pytorch框架训练识别樱桃新鲜度-不含数据集图片-含逐行注释和说明文档.zip

- 优质资源,让 .NET 开发更简单,更通用,更流行

- resnet模型-基于深度学习对苹果颜色识别-不含数据集图片-含逐行注释和说明文档.zip

- mobilenet模型-基于图像分类算法对食物美食识别-不含数据集图片-含逐行注释和说明文档.zip

- ImmunityDebugger

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功