没有合适的资源?快使用搜索试试~ 我知道了~

H9CKNNNBKTMRPR_REV0.3

需积分: 9 4 下载量 16 浏览量

2018-07-27

09:57:48

上传

评论

收藏 2.42MB PDF 举报

温馨提示

试读

138页

SKhynix 256 FGPA Specification 16Gb LPDDR3(X32,2channel)

资源推荐

资源详情

资源评论

This document is a general product description and is subject to change without notice. SK hynix does not assume any responsibility

for use of circuits described. No patent licenses are implied.

Rev 0.3 / Nov. 2013 1

256ball FBGA Specification

16Gb LPDDR3 (x32, 2-Channel)

Rev 0.3 / Nov. 2013 2

Preliminary

H9CKNNNBKTMRPR

LPDDR3-S8B 16Gb(x32, 2-Channel)

Document Title

FBGA

16Gb (x32, 2-Channel) LPDDR3

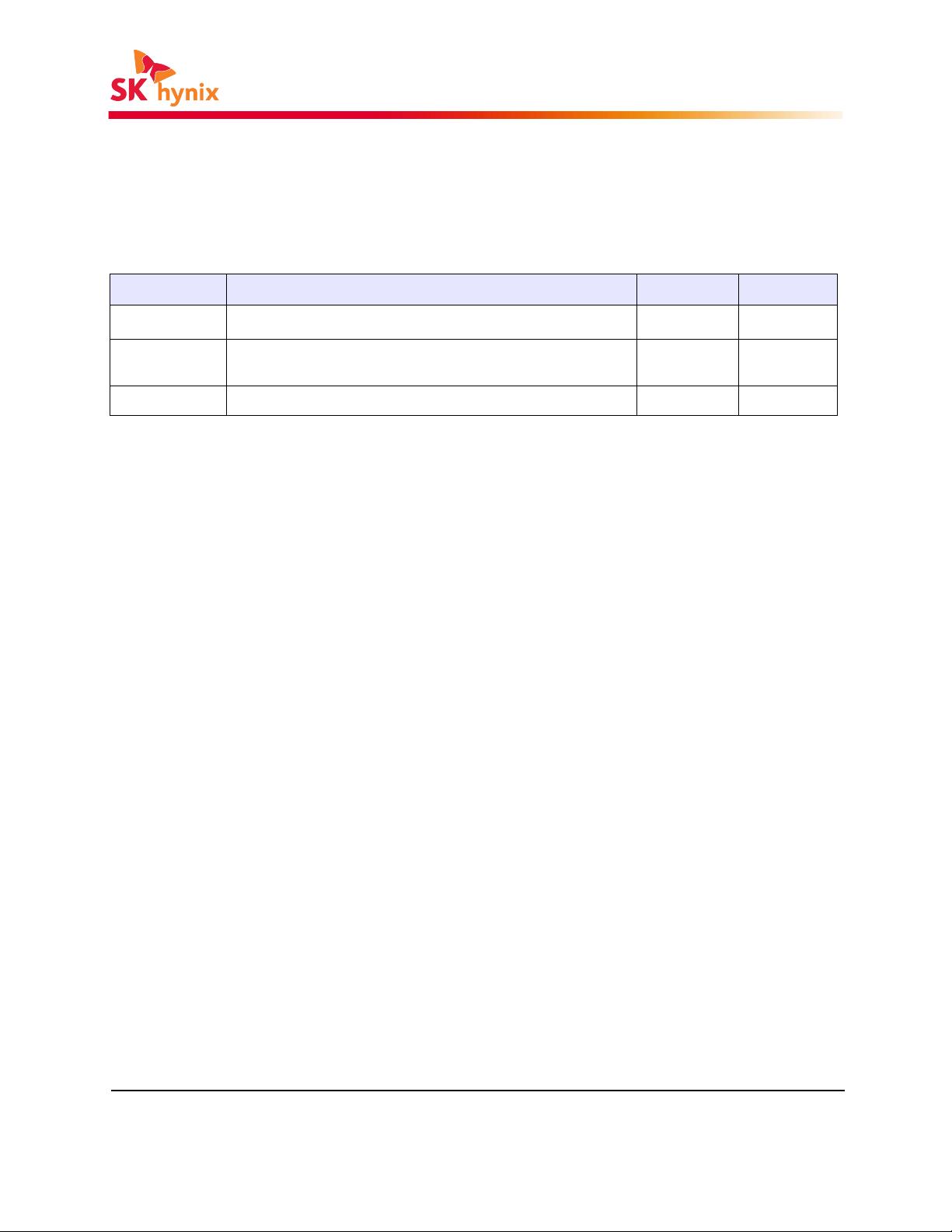

Revision History

Revision No. History Draft Date Remark

0.1

- Initial Draft

Sep. 2013 Preliminary

0.2

- Added DRAM speed 1866Mbps

- Updated IDD specification

Oct. 2013 Preliminary

0.3 - Updated IDD specification Nov. 2013 Preliminary

Rev 0.3 / Nov. 2013 3

Preliminary

H9CKNNNBKTMRPR

LPDDR3-S8B 16Gb(x32, 2-Channel)

FEATURES

[ FBGA ]

● Operation Temperature

- (-30)

o

C ~ 105

o

C

● Package

- 256-ball FBGA - 14.0x14.0mm

2

, 0.70t, 0.40mm pitch

- Lead & Halogen Free

[ LPDDR3 ]

VDD1 = 1.8V (1.7V to 1.95V)

VDD2, VDDCA and VDDQ = 1.2V (1.14V to 1.30)

HSUL_12 interface (High Speed Unterminated Logic 1.2V)

Double data rate architecture for command, address and data Bus;

- all control and address except CS_n, CKE latched at both rising and falling edge of the clock

- CS_n, CKE latched at rising edge of the clock

- two data accesses per clock cycle

Differential clock inputs (CK_t, CK_c)

Bi-directional differential data strobe (DQS_t, DQS_c)

- Source synchronous data transaction aligned to bi-directional differential data strobe (DQS_t, DQS_c)

- Data outputs aligned to the edge of the data strobe (DQS_t, DQS_c) when READ operation

- Data inputs aligned to the center of the data strobe (DQS_t, DQS_c) when WRITE operation

DM masks write data at the both rising and falling edge of the data strobe

Programmable RL (Read Latency) and WL (Write Latency)

Programmable burst length: 8

Auto refresh and self refresh supported

All bank auto refresh and per bank auto refresh supported

Auto TCSR (Temperature Compensated Self Refresh)

PASR (Partial Array Self Refresh) by Bank Mask and Segment Mask

DS (Drive Strength)

DPD (Deep Power Down)

ZQ (Calibration)

ODT (On Die Termination)

Rev 0.3 / Nov. 2013 4

Preliminary

H9CKNNNBKTMRPR

LPDDR3-S8B 16Gb(x32, 2-Channel)

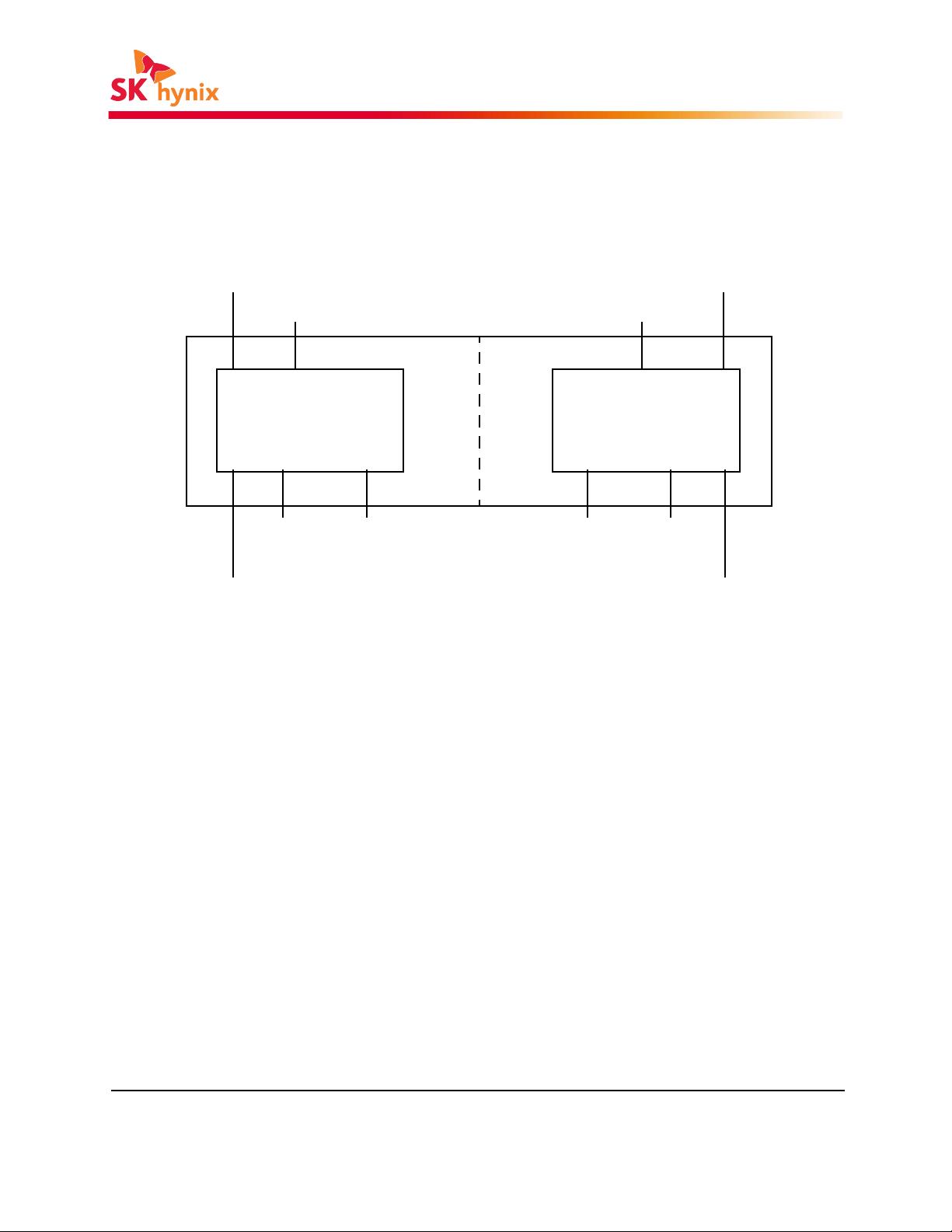

Functional Block Diagram

CS_n

8Gb x32 device

CKE

VDD1, VDD2, VDDCA, VDDQ, Vref(CA/DQ)

(256M x 32)

8Gb x32 device

(256M x 32)

Note

1. Total current consumption is dependent to user operating conditions. AC and DC Characteristics shown in

this specification are based on a single die. of “DC Parameters and Operating Conditions”

Channel A Channel B

CA0 ~ CA9, DM0~DM3

DQS0_t~DQS3_t,

DQS0_c~DQS3_c

CA0 ~ CA9, DM0~DM3

DQS0_t~DQS3_t,

DQS0_c~DQS3_c

DQ0~DQ31

CK_t, CK_c

ZQ, ODT

CK_t, CK_c

ZQ, ODT

DQ0~DQ31

VSS, VSSCA, VSSQ

VDD1, VDD2, VDDCA, VDDQ, Vref(CA/DQ)

VSS, VSSCA, VSSQ

CS_n

CKE

Rev 0.3 / Nov. 2013 5

Preliminary

H9CKNNNBKTMRPR

LPDDR3-S8B 16Gb(x32, 2-Channel)

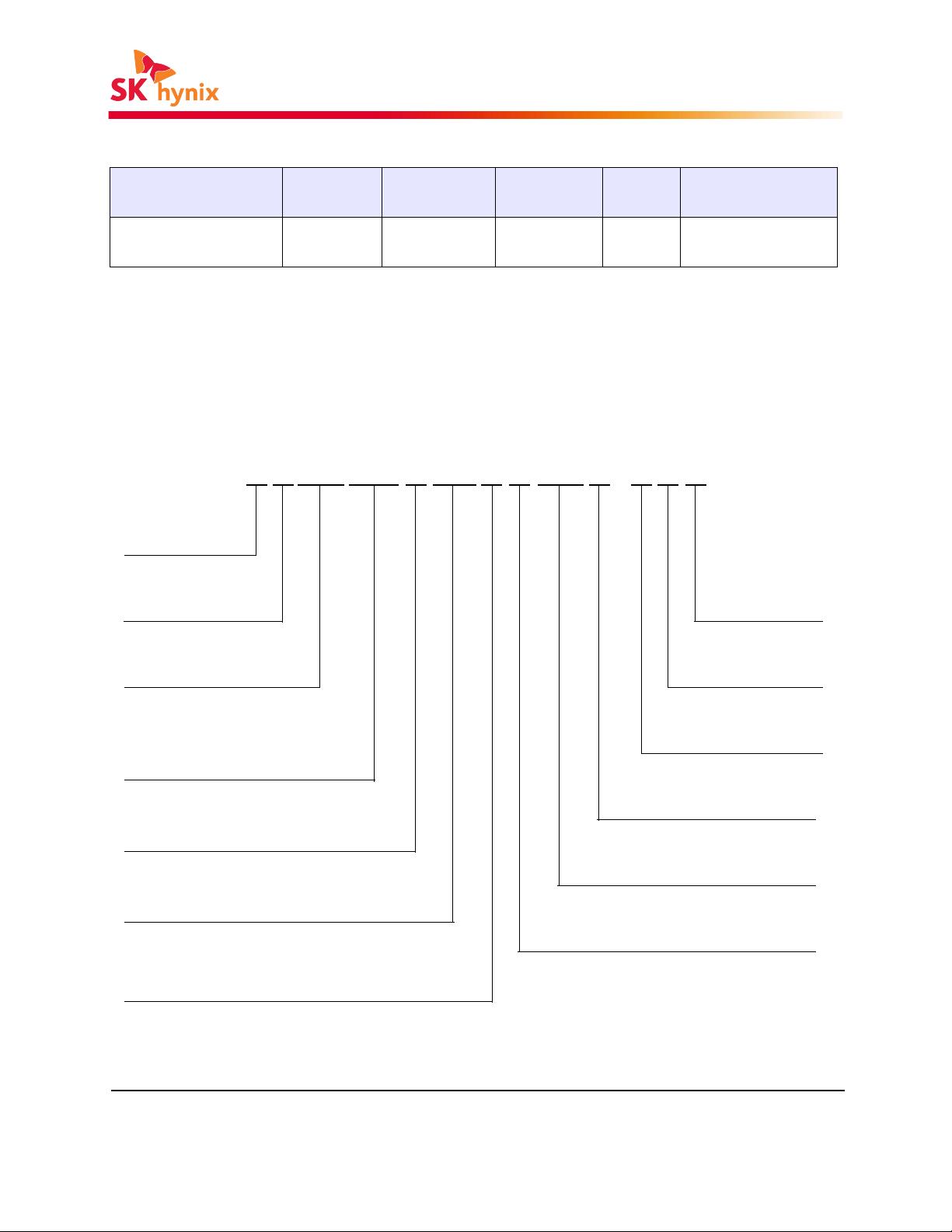

ORDERING INFORMATION

Part Number

Memory

Combination

Operation

Voltage

Density Speed Package

H9CKNNNBKTMRPR-NUH LPDDR3 S8B 1.8V/1.2/1.2/1.2 16Gb(x32, 2Ch) DDR3 1866

256Ball FBGA

(Lead & Halogen Free)

H 9 C K N N N B K T M R P R - N U H

MCP/PoP

Product Mode :

Density, Stack, Block Size

Voltage & I/O for NVM :

Voltage, I/O & Option for DRAM :

None

PoP LPDDR3 only

Density, Stack, CH & CS for DRAM :

NAND Speed : none

Package Material :

Lead & Halogen Free

Package Type :

Generation : 1st

& Page Buffer for NVM

1)

:

None

16Gb, DDP, 2Ch, 1CS

1.2v/1.2, x32, LPDDR3

FBGA 256 Ball 14x14

Temperature :

Mobile (-30~105’C)

SK Hynix Memory

DRAM Speed :

LPDDR3 1866Mbps

剩余137页未读,继续阅读

资源评论

傅培焱

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功