www.wkmic.com

为开微电子 2016年 发布 版权所有

wkmic 12/2016 WK2124串口扩展芯片应用手册 2 of 25

WK2124 串口扩展芯片应用手册

1.产品概述

WK2124 是 SPI

TM

接口的 4 通道 UART 器件,WK2124 实现 SPI 桥接/扩展 4 个增强功能串口

(UART)功能。

扩展的子通道的 UART 具备如下功能特点:

每个子通道UART的波特率、字长、校验格式可以独立设置,最高可以提供2Mbps的通信速

率。

每个子通道可以独立设置工作在IrDA红外通信。

每个子通道具备收/发独立的256 BYTE FIFO,FIFO的中断可按用户需求进行编程触发点。

WK2124 采用 SSOP20 绿色环保无铅封装,可以工作在 2.5~5.0V 的宽工作电压范围,具备可配

置自动休眠/唤醒功能。

[注]:SPI

TM

为MOTOLORA公司的注册商标。

2.基本特性

2.1 原理框图

www.wkmic.com

为开微电子 2016年 发布 版权所有

wkmic 12/2016 WK2124串口扩展芯片应用手册 3 of 25

2.2 封装引脚图

WK2124 封装引脚图 SSOP20:

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

WK2124

GND

SCS

SCLK

SDIN

SDOUT

RX4

TX4

VCC

/RST

/IRQ TX2

RX2

GND

TX1

RX1

TX3

RX3

VCC

OSCI

OSC0

2.3 硬件原理图

1、从原理图上分析,WK2124 和 MCU 之间的连接主要有 3 部分:

A、SPI 总线 :WK2124 通过 SPI 和 MCU 进行数据通信。SPI 会传输命令字节和数据字节。

B、中断:WK2124 的 IRQ 连接到 MCU 的外部中断输入引脚。这个连接不是必须的,如果没有

连接到 MUC 的外部中断输入引脚,那么就只能采用查询的编程方式实现对子串口的数据收发,效

率较低。

C、复位控制:WK2124 的复位引脚,低电平有效,时间长度为 10ms。复位以后,WK2124 的

所有寄存器值恢复到默认值,SPI 总线上的命令解析也会同时复位。

2、时钟电路:通常采用无源晶振,晶振大小和子串口波特率相关,(具体关系请参考数据手册

波特率编程章节)和晶振并联的匹配电阻是 1M 欧的,是必须的。

www.wkmic.com

为开微电子 2016年 发布 版权所有

wkmic 12/2016 WK2124串口扩展芯片应用手册 4 of 25

3.SPI 接口时序与软件编程

3.1 WK2124 SPI 时序综述

WK2124 在 SPI 时序上遵循 SPI 标准时序;但是由于内部的硬件解析协议,WK2124 的 SPI 操作

时序也有一些自身的特点。

1、WK2124 作为 SPI 从设备,支持 SPI 模式 0,即在主机端需要设置 CPOL=0(SPI 时钟极性选择

位),CPHA=0( SPI 时钟相位选择位)。

2、特别的,就是片选信号:片选信号在空闲时应该保持为高电平,拉低片选信号作为一次读写

操作的开始,拉高作为一次操作的结束。

片选信号几种错误的操作:

A. 直接把片选信号接地,或者长期拉低,导致硬件解析协议解析错误。

B. 单个字节拉高拉低片选信号,这样也会导致硬件解析不了命令。

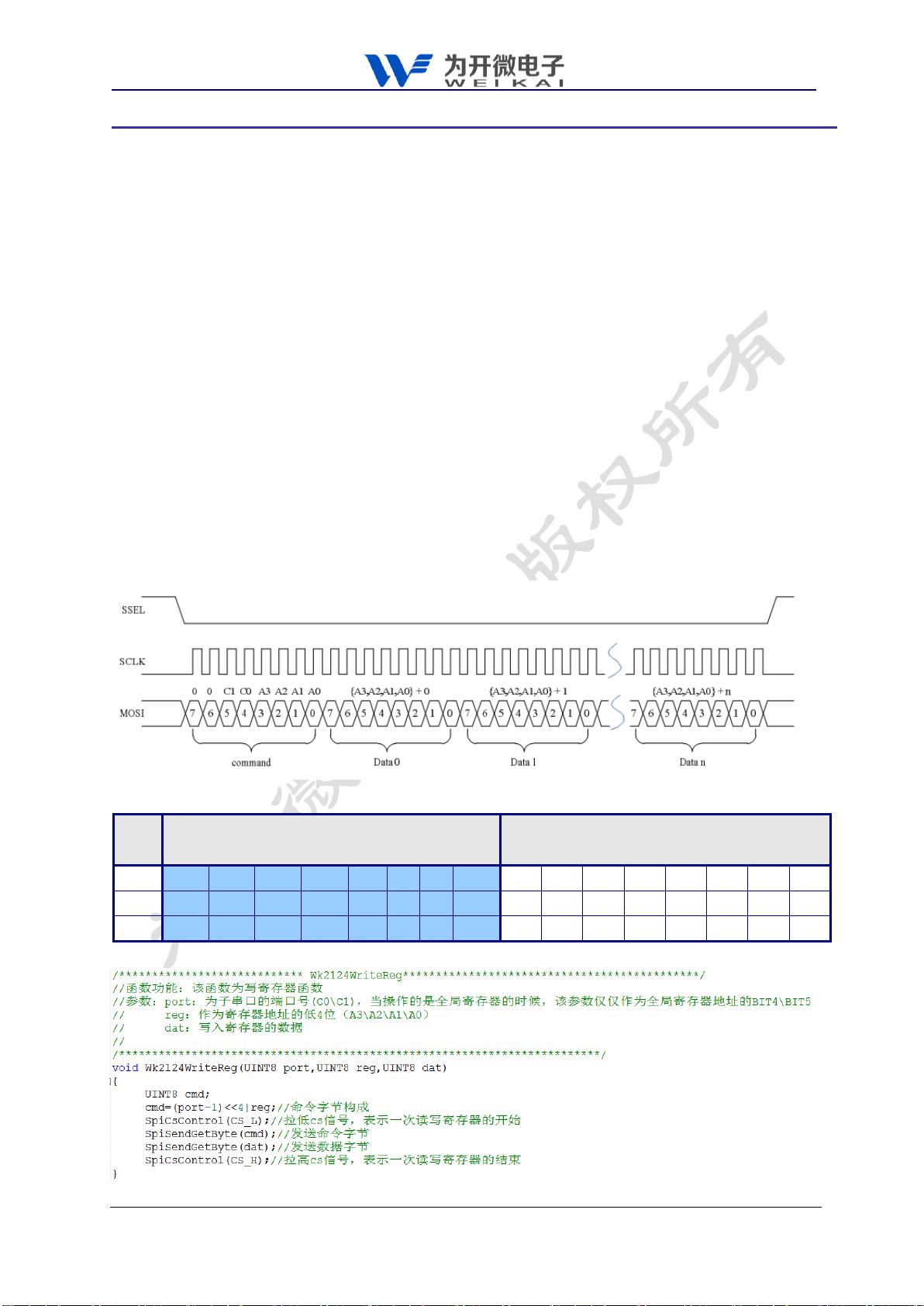

3.2 WK2124 写寄存器时序分析

写寄存器操作时序如图所示:先写入一个命令字节(Command Byte),随后写入相应的数据字

节,数据字节的寄存器地址自动增加。但是通常我们在编程的时候都是,先写入一个命令字节,然后

写一个数据字节,这边操作更加灵活。注意 SSEL(片选信号的控制)。

SPI 写寄存器

SPI

控制字节 CMD

数据字节 DB(写 N 个数据字节,寄存

器地址自动增加)

BIT

7

6

5

4

3

2

1

0

7

6

5

4

3

2

1

0

MOSI

0

0

C1

C0

A3

A2

A1

A0

D7t

D6t

D5t

D4t

D3t

D2t

D1t

D0t

MISO

HZ

HZ

HZ

HZ

HZ

HZ

HZ

HZ

HZ

HZ

HZ

HZ

HZ

HZ

HZ

HZ

编程参考:

www.wkmic.com

为开微电子 2016年 发布 版权所有

wkmic 12/2016 WK2124串口扩展芯片应用手册 5 of 25

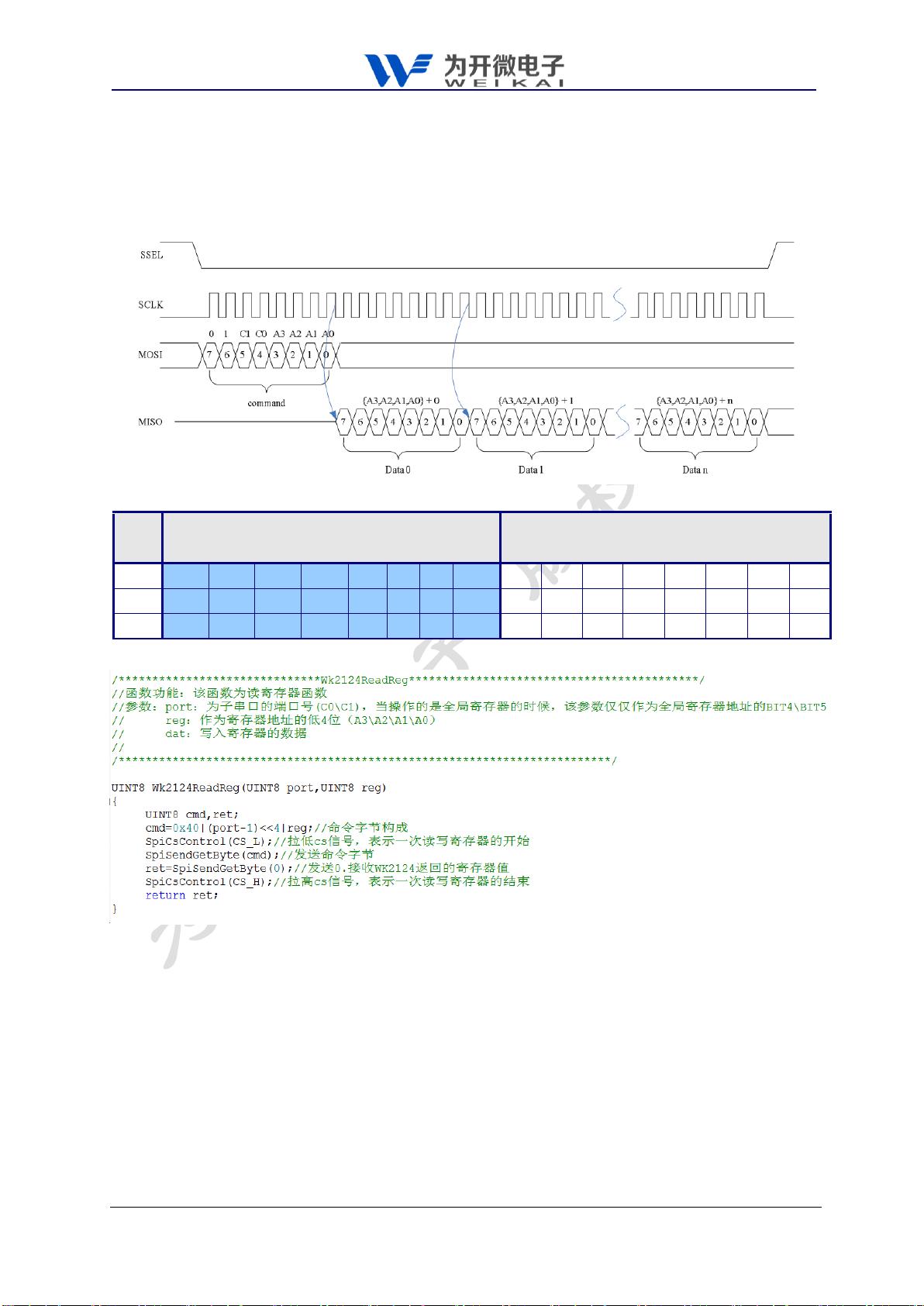

3.3 WK2124 读寄存器时序分析

读寄存器操作时序如图所示:先写入一个命令字节(Command Byte),随后芯片 MISO 线上会

返回相应的数据字节。返回数据字节的寄存器地址自动增加。通常编程都是先发送一个读命令,然

后接收返回的寄存器数据。

SPI 读寄存器

SPI

控制字节 CMD

数据字节 DB(读 N 个数据字节,寄存

器地址自动增加)

BIT

7

6

5

4

3

2

1

0

7

6

5

4

3

2

1

0

MOSI

0

1

C1

C0

A3

A2

A1

A0

X

X

X

X

X

X

X

X

MISO

HZ

HZ

HZ

HZ

HZ

HZ

HZ

HZ

D7t

D6t

D5t

D4t

D3t

D2t

D1t

D0t

编程参考:

3.4 WK2124 写 FIFO 时序分析

写 FIFO 操作时序如图所示:先写入一个命令字节(Command Byte),随后再写入相应的数据字

节,FIFO 地址自动增加。该操作可以一次向 FIFO 中写入多个数据,但是不能超过 256 个字节。通

常我们都会先查询 wk2124 的发送 FIFO 里有多少个字节等待发送,然后再确定能写入 FIFO 的字节

个数,否者如果 FIFO 已经满了,在写入数据,FIFO 就会溢出。