STACKING PERFORMANCE IN THE BINARY COUNTER

1

A.Shanmugapriya,

2

G.Selvarani,

3

P.Shanthanalakshmi,

4

R.Sugandha,

5

S.ArulPriya

1,2,3,4

UG Students,

5

Assistant Professor

1,2,3,4,5

Electronics And Communication Engineering,

M.Kumarasamy College of Engineering, Thalavapalayam, Karur

1

asha[email protected],

2

vinoselva[email protected],

3

p.shanthanalakshmi.in@gmail.com

4

sugandha.[email protected],

5

arulpriyas.ece@mkce.ac.in

Abstract: The solution to the delayed output in the

multiplier by implementing new counter in it to work

highly efficient. It will improve the existing method of

multipliers in the future. More multiplier circuits have

proposed but the it was changed as existing methods in

this world. The existing method which need more steps

to produce the output. In this paper we see that it will

recover the problem which existing in the earliest

method. This paper will mark out a new binary counter

for the efficient use in the multipliers. Hence there is a

use of counter in the multiplier to make efficient for the

products. By comparing the different methods let us see

a brief study in it.

Keywords: Very Large Scale Integration(VLSI), 3 bit

stack circuit, xor gates

1. Introduction

Recent trends in the researches in the VLSI makes a

efficient result in the system. We always used to work

in a high speed and efficient machine. Likewise

efficient addition of operands is essential in the unit.

The speed and power efficiency of circuits is of

critical importance in the performance. The essential

part in the arithmetic logic unit is multiplier circuits.

The binary multiplication of integers or fixed-point

numbers results in partial products that must be added

to produce the final product.The addition of all the

results make some delay in the output and it consume

more power.

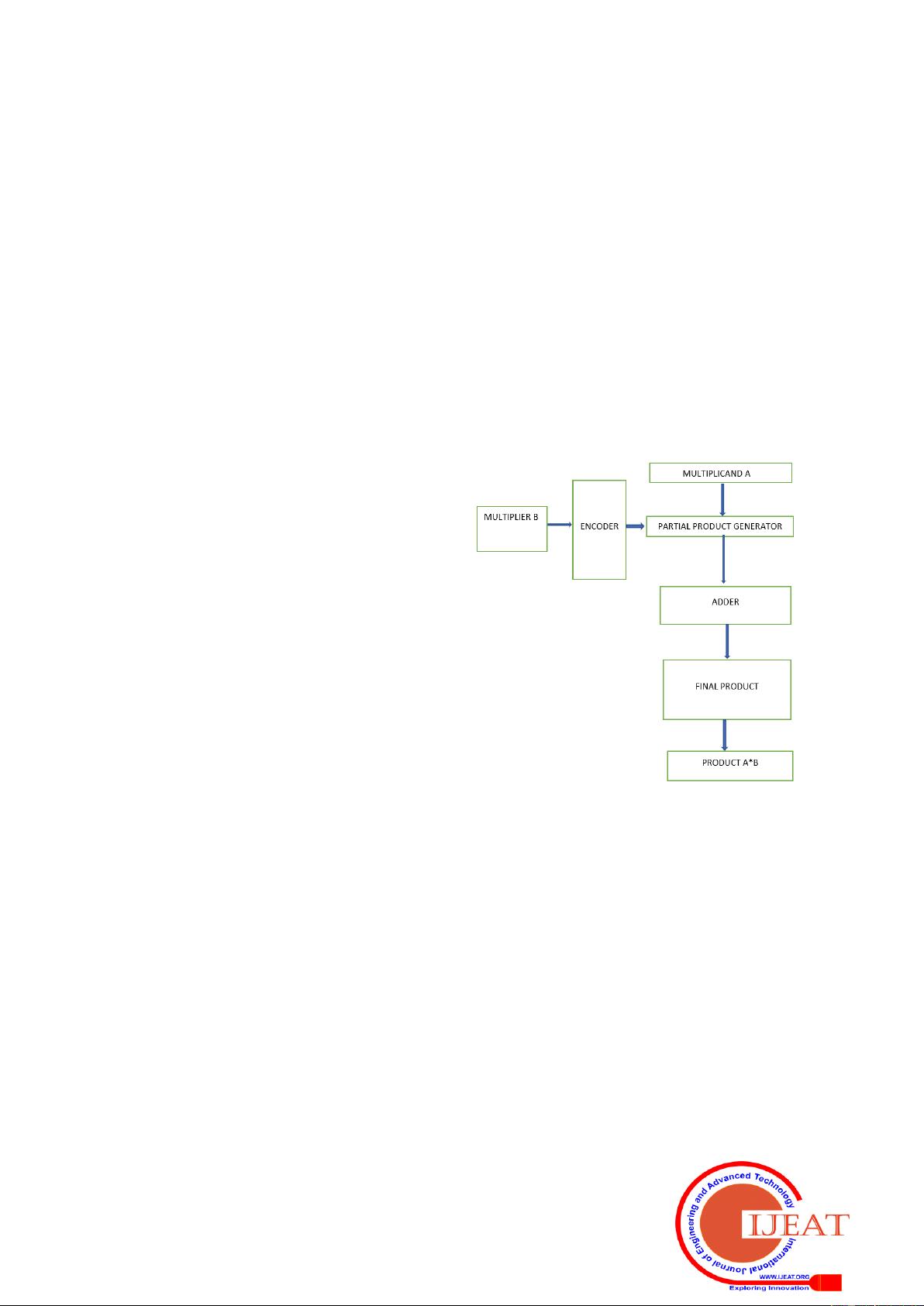

In order to overcome the delay in the addition of

the total products for the output many methods have

been developed. To make the partial products in a

efficient manner column compression method using

multiplier is used in earlier. It is one of the way to make

it reliable which is shown in Wallace tree. It involve in

the full adder function to reduce the group of bits in the

various steps by continuosly reducing in adders with

the help of the carry save adder. In this process it will

complete the task in lesser time but it only give less

performance.

Then the parallel adders which make use of full

adder to implement it. It give high performance

compare to the Wallace tree multiplier. So we are

implemented new counter design to avoid those

complications. In this we have designed the two types

of counter which is compared each other by inserting

into the existing multipliers. The implemented counter

which work with higher performance in the multiplier.

From the designed counters we will see the

proposed method among them because it’s power

consumption and the usage of transistors is less

compare to other counter. In the earlier method the

larger number of bits with equal weight performs more

operations to produce the output with different weight.

In the basic column method bits are performed in the

column to produce the reliable output. In the new

counter it take the 1’s bit and 0’s bit in a separate

sideand it count the number of bits which has equal

weight and produce the output for the count in 3 bits of

increasing the earlier weight. In this method there is a

delay in the circuit because of the complex in its

structure

In the other new counter we implement the less

complex in the circuit with the help of stacker in it. The

delay which makes in the above counter circuit is

less in this counter which is the major problem in all

existing structure.

So we are need to move the other method which is

6:3counter. Stacker circuit which perform to combine

both the 3 bit stack into 6 bit stack. It leads to produce a

new binary counter without xor gates on the delay.

Removing the more number of xor gates in the circuit

make efficient output.

2. VLSI

The System-On-Chip (SoC) revolution challenges both

design and test engineers, especially in the area of

power dissipation. Generally, a circuit or system

consumes more power in test mode than in normal

mode. This extra power consumption can give rise to

severe hazards in circuit reliability or, in some cases,

can provoke instant circuit damage. Moreover, it can

create problems such as increased product cost,

difficulty in performance verification, reduced

autonomy of portable systems, and decrease of overall

International Journal of Pure and Applied Mathematics

Volume 118 No. 20 2018, 1385-1389

ISSN: 1311-8080 (printed version); ISSN: 1314-3395 (on-line version)

url: http://www.ijpam.eu

Special Issue

ijpam.eu

1385