VerilogHDL.rar_tool

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

《Verilog HDL——电子设计自动化(EDA)的利器》 Verilog HDL,全称为“Verilog Hardware Description Language”,是一种广泛使用的硬件描述语言,它允许工程师以接近于人类思考的方式描述数字系统的逻辑和行为。在电子设计自动化(EDA)领域,Verilog HDL扮演着至关重要的角色,是芯片设计、验证、仿真以及综合等环节的核心工具。 Verilog HDL的起源可以追溯到20世纪80年代,当时为了解决复杂集成电路的设计问题而诞生。它是一种面向过程的语言,支持数据流和并行处理,使得设计师能够同时描述多个事件和操作。这种特性使得Verilog不仅适用于系统级设计,也适用于门级和寄存器传输级的设计。 在Verilog HDL中,设计被描述为一系列的模块,每个模块包含输入、输出、时钟和其他内部信号,以及实现其功能的逻辑。这些模块可以通过实例化进行复用,实现大规模设计的模块化和可重用性。例如,一个简单的加法器模块可以被多次实例化,用于构建更复杂的算术逻辑单元。 Verilog HDL提供了丰富的语句类型,如分配语句(assign)、事件控制语句(always)和进程语句(initial),它们分别用于静态逻辑连接、时序逻辑描述和初始化操作。此外,还有非阻塞赋值(<=)和阻塞赋值(=)的区别,这在同步设计中尤其关键,以避免不必要的竞争和冒险条件。 在设计完成后,Verilog代码会通过编译器进行语法和语义检查,然后进入仿真阶段,通过仿真器验证设计的功能正确性。如果一切顺利,设计将被综合成门级网表,进一步映射到具体的硬件芯片上,这个过程可能涉及到优化和约束处理,以满足性能、面积和功耗等目标。 在压缩包中的“VerilogHDL的基知.pdf”文件,很可能是对Verilog HDL的基础知识进行详细讲解的资料,涵盖了Verilog的基本语法、常用模块、设计流程等方面。对于初学者来说,理解这些基础知识是掌握Verilog HDL的关键,也是进入EDA领域的重要一步。 Verilog HDL是电子工程师的得力工具,通过它,我们可以清晰地描述出数字系统的行为和结构,实现从概念到物理实现的无缝过渡。深入学习和熟练掌握Verilog HDL,对于提升电子设计的效率和质量具有重要意义。

VerilogHDL.rar (1个子文件)

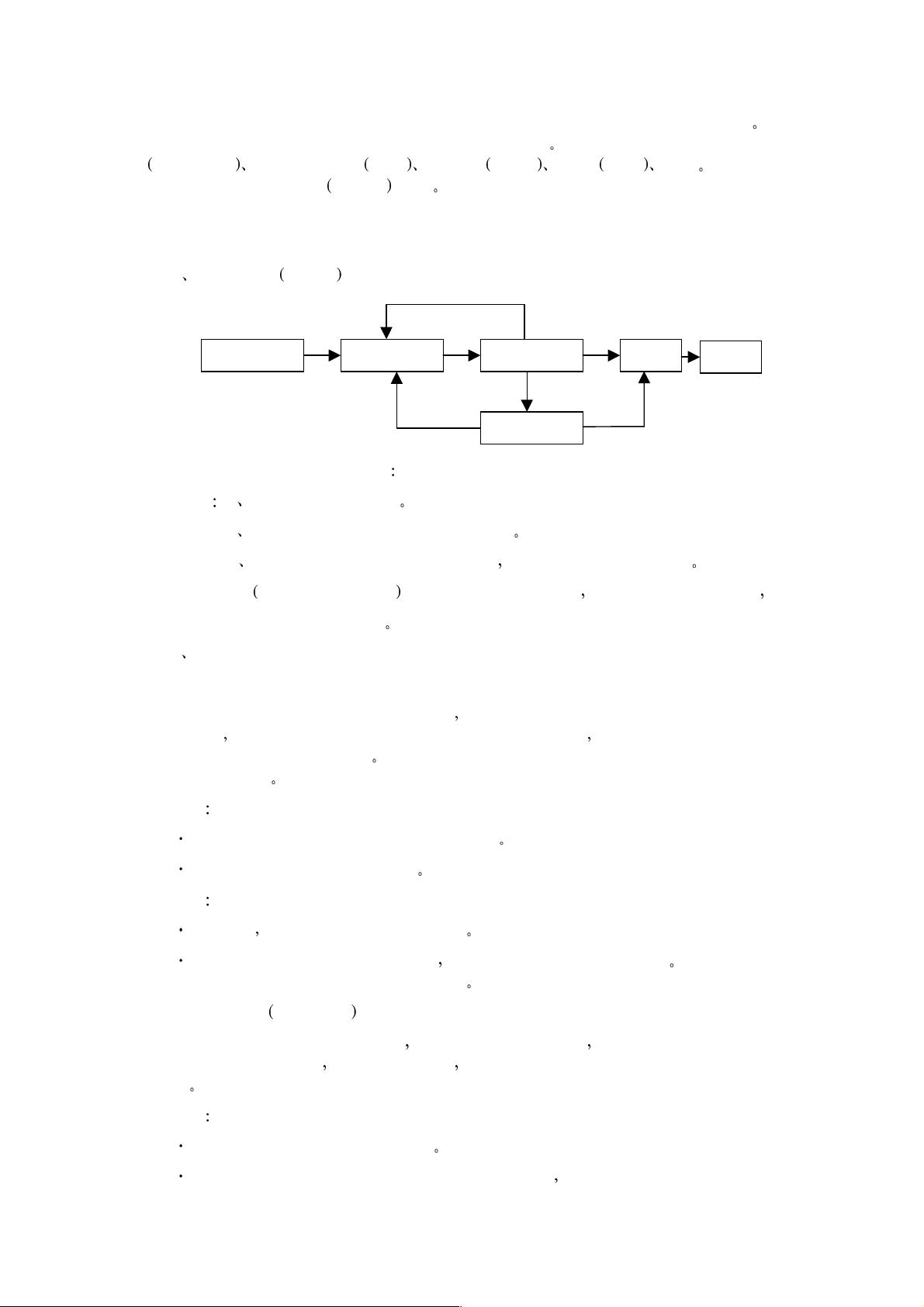

VerilogHDL.rar (1个子文件)  VerilogHDL的基知.pdf 317KB

VerilogHDL的基知.pdf 317KB- 1

- 粉丝: 89

- 资源: 1万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于Pygame库实现新年烟花效果的Python代码

- 浪漫节日代码 - 爱心代码、圣诞树代码

- 睡眠健康与生活方式数据集,睡眠和生活习惯关联分析()

- 国际象棋检测10-YOLO(v5至v9)、COCO、CreateML、Paligemma数据集合集.rar

- 100个情侣头像,唯美手绘情侣头像

- 自动驾驶不同工况避障模型(perscan、simulink、carsim联仿),能够避开预设的(静态)障碍物

- 使用Python和Pygame实现圣诞节动画效果

- 数据分析-49-客户细分-K-Means聚类分析

- 车辆轨迹自适应预瞄跟踪控制和自适应p反馈联合控制,自适应预苗模型和基于模糊p控制均在simulink中搭建 个人觉得跟踪效果相比模糊pid效果好很多,轨迹跟踪过程,转角控制平滑自然,车速在36到72

- 企业可持续发展性数据集,ESG数据集,公司可持续发展性数据(可用于多种企业可持续性研究场景)

信息提交成功

信息提交成功