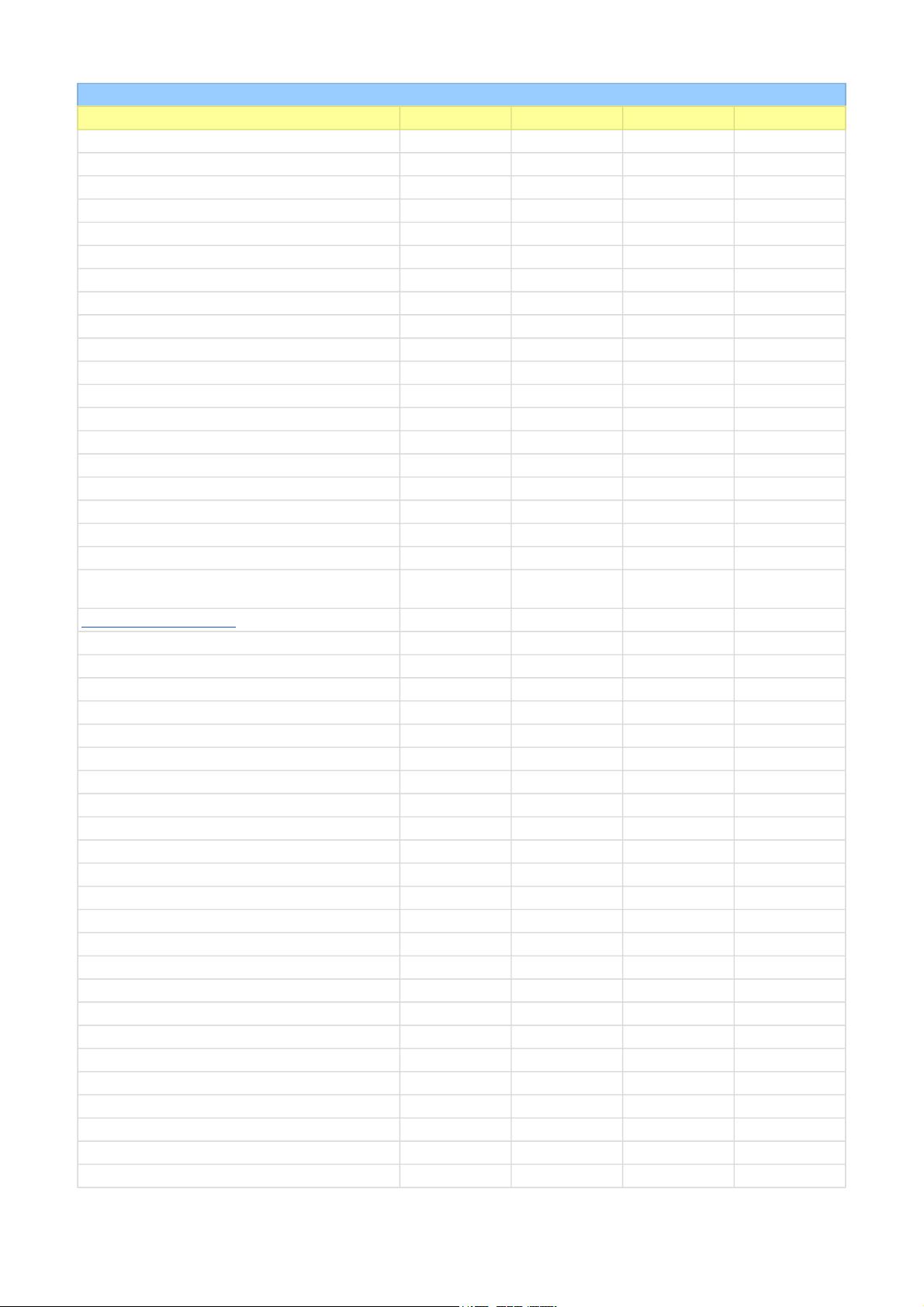

Device Utilization Summary

Slice Logic Utilization Used Available Utilization Note(s)

Number of Slice Registers 6 126,576 1%

Number used as Flip Flops 6

Number used as Latches 0

Number used as Latch-thrus 0

Number used as AND/OR logics 0

Number of Slice LUTs 8 63,288 1%

Number used as logic 8 63,288 1%

Number using O6 output only 8

Number using O5 output only 0

Number using O5 and O6 0

Number used as ROM 0

Number used as Memory 0 15,616 0%

Number of occupied Slices 6 15,822 1%

Number of MUXCYs used 0 31,644 0%

Number of LUT Flip Flop pairs used 8

Number with an unused Flip Flop 2 8 25%

Number with an unused LUT 0 8 0%

Number of fully used LUT-FF pairs 6 8 75%

Number of unique control sets 6

Number of slice register sites lost

to control set restrictions 42 126,576 1%

Number of bonded IOBs 6 326 1%

Number of RAMB16BWERs 0 268 0%

Number of RAMB8BWERs 0 536 0%

Number of BUFIO2/BUFIO2_2CLKs 0 32 0%

Number of BUFIO2FB/BUFIO2FB_2CLKs 0 32 0%

Number of BUFG/BUFGMUXs 1 16 6%

Number used as BUFGs 1

Number used as BUFGMUX 0

Number of DCM/DCM_CLKGENs 0 12 0%

Number of ILOGIC2/ISERDES2s 0 506 0%

Number of IODELAY2/IODRP2/IODRP2_MCBs 0 506 0%

Number of OLOGIC2/OSERDES2s 0 506 0%

Number of BSCANs 0 4 0%

Number of BUFHs 0 384 0%

Number of BUFPLLs 0 8 0%

Number of BUFPLL_MCBs 0 4 0%

Number of DSP48A1s 0 180 0%

Number of ICAPs 0 1 0%

Number of MCBs 0 4 0%

Number of PCILOGICSEs 0 2 0%

Number of PLL_ADVs 0 6 0%

Number of PMVs 0 1 0%

Number of STARTUPs 0 1 0%

Number of SUSPEND_SYNCs 0 1 0%

Average Fanout of Non-Clock Nets 1.88